FPGA設計中,生成時鐘分為兩大類:自動生成時鐘和用戶生成時鐘。前者是指由CMB(Clock Modifying Blocks,例如MMCM、PLL、BUFR 、BUFGCE_DIV、PHASER_x等)生成的時鐘;后者是指用戶通過組合/時序邏輯生成的時鐘。

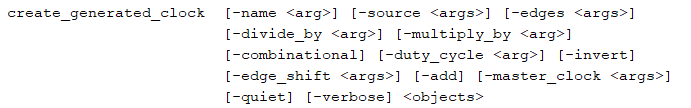

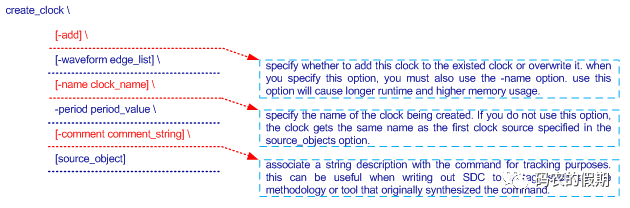

在某些場景下,對于生成時鐘需要借助create_generated_clock創建。這里我們討論一下create_generated_clock的典型應用場景。首先給出create_generated_clock的基本參數,如下圖所示。生成時鐘都有一個與之伴隨的主時鐘(MasterClock)。這個主時鐘可以是全局時鐘管腳進來的時鐘(也就是設計的PrimaryClock),也可以是其他生成時鐘。可通過選項-master_clock指定。

場景1:重命名自動生成時鐘

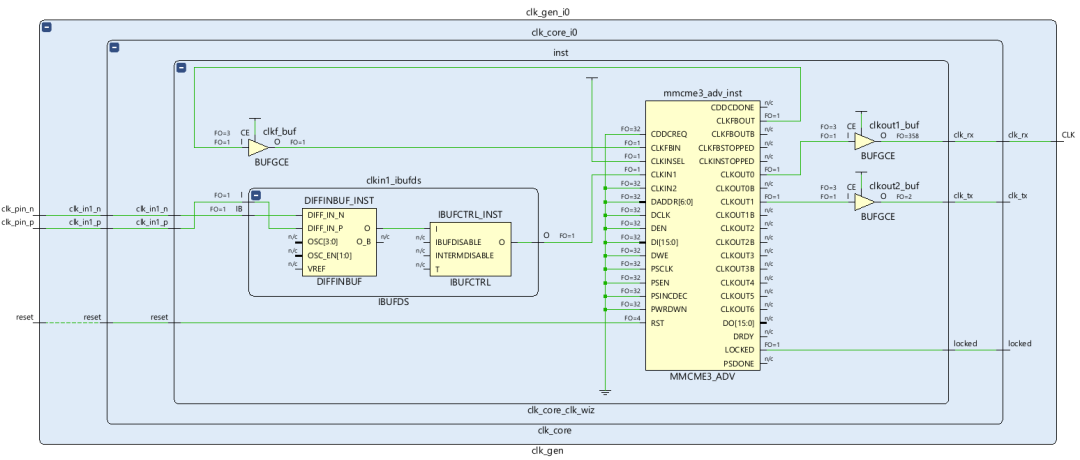

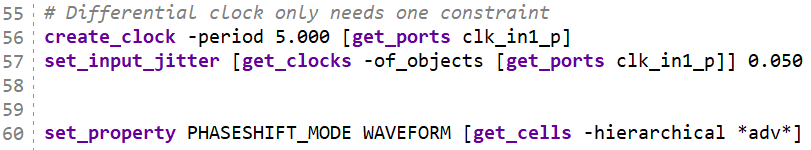

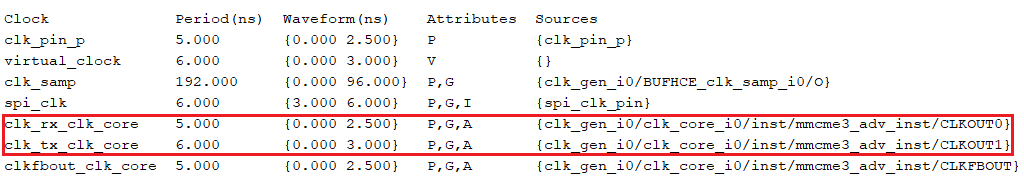

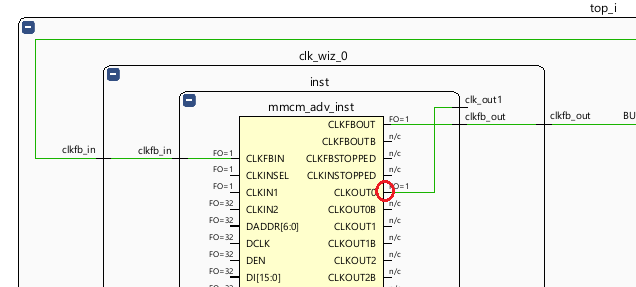

對于自動生成時鐘(又稱自動衍生時鐘),只要創建了主時鐘,工具會自動創建生成時鐘。因此,如果設計中只存在“全局時鐘管腳->MMCM/PLL->BUFG”這種情形,而且MMCM/PLL是通過Clocking Wizard IP生成的,那么用戶就不用通過create_clock創建時鐘,因為IP會自動創建。例如,對于下圖所示設計,IP會自帶約束。在這種情況下,打開綜合后的設計,執行report_clocks命令,可以看到自動生成的時鐘。

如上圖所示,自動生成時鐘的名字之所以如此,是因為我們在調用IP時對輸出端口進行了重命名,如下圖所示。

另一方面,如果我們沒有對端口重命名,而希望生成時鐘名字是期望的名字,以便于閱讀分析以及后續約束的引用,這時就可以通過create_generated_clock命令進行重命名。例如:要將下圖中的MMCM輸出端口CLKOUT0輸出時鐘命名為clk200,這時需要通過選項-name給時鐘命名,同時指定時鐘的端口,這里通過get_pins獲取。

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26873 -

PLL電路

+關注

關注

0文章

92瀏覽量

6595

原文標題:create_generated_clock該怎么使用?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA中時鐘的用法

對邊沿對齊源同步輸入端口的約束

時序約束之時鐘約束

CLOCK作為外部輸出控制Pin的整體延遲?

create_generate_clock無法找到正確的引腳

Xilinx工具vivado使用約束命令時出現警告的解決辦法?

請問如何約束作為輸入時鐘復制的時鐘?

子模塊的generated clock是否需要和其它子模塊進行balance?

靜態時序分析

今日說“法”:TimeQuest約束外設之詭異的Create Generated Clocks

FPGA案例之衍生時鐘約束

Vivado的XDC設置輸出延時問題

評論