Verilog是一種硬件描述語言(HDL),廣泛應用于數字電路設計和硬件驗證。在Verilog中,模塊是構建電路的基本單元,而模塊端口對應方式則用于描述模塊之間信號傳遞的方式。本文將介紹Verilog中的模塊端口對應方式,并提供示例代碼和詳細解釋,以幫助讀者更好地理解和應用。

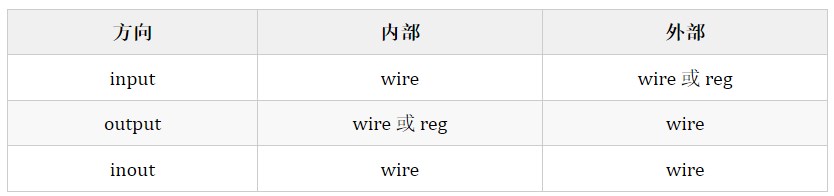

首先,我們來了解一下Verilog中的模塊和模塊端口。一個Verilog模塊被定義為包含一組聲明和語句的代碼塊,類似于C語言中的函數。模塊可以有輸入端口(input)、輸出端口(output)和雙向端口(inout)。端口是模塊與外部環境之間的接口,用于輸入和輸出數據。

Verilog中的模塊端口對應方式有四種:按位置、按名稱、按順序和混合。下面我們將詳細介紹每種對應方式的使用方法和特點。

- 按位置對應方式:

按位置對應方式是最常用的對應方式,也是最簡單直觀的方式。在模塊調用的語句中,按照模塊定義中端口聲明的順序,依次傳遞參數。這種對應方式不需要指定端口名稱,只需保證傳遞的參數按正確的順序進行。

下面是一個按位置對應方式的示例:

module test_module(input A, input B, output C);

// Module implementation

endmodule

module top_module();

wire out_signal;

test_module dut(.A(in_signal_A), .B(in_signal_B), .C(out_signal));

// Module instantiation

endmodule

endmodule

endmodule在這個示例中,test_module模塊有三個端口:A、B和C。在top_module中,我們使用按位置對應方式實例化了test_module,按照模塊定義中端口的順序依次傳遞了參數in_signal_A、in_signal_B和out_signal。

- 按名稱對應方式:

按名稱對應方式是根據端口的名稱來對應參數,可以通過指定參數名來傳遞參數。這種對應方式相對于按位置對應方式更加直觀,不容易出錯。

下面是一個按名稱對應方式的示例:

module test_module(input A, input B, output C);

// Module implementation

endmodule

module top_module();

wire out_signal;

test_module dut(.A(in_signal_A), .B(in_signal_B), .C(out_signal));

// Module instantiation

endmodule

endmodule

endmodule在這個示例中,我們使用按名稱對應方式實例化了test_module。在端口對應的位置,我們通過指定參數名來傳遞參數,例如.A(in_signal_A)、.B(in_signal_B)和.C(out_signal)。

- 按順序對應方式:

按順序對應方式與按位置對應方式類似,區別在于不需要指定參數名,只需按照模塊定義中端口的順序依次傳遞參數。這種對應方式在參數較多或命名較復雜時可以簡化代碼。

下面是一個按順序對應方式的示例:

module test_module(input A, input B, output C);

// Module implementation

endmodule

module top_module();

wire out_signal;

test_module dut(in_signal_A, in_signal_B, out_signal);

// Module instantiation

endmodule

endmodule

endmodule在這個示例中,我們使用按順序對應方式實例化了test_module。在端口對應的位置,我們按照模塊定義中端口的順序依次傳遞了參數in_signal_A、in_signal_B和out_signal。

- 混合對應方式:

混合對應方式是將按位置、按名稱和按順序對應方式混合使用,根據需要靈活選擇。使用混合對應方式可以同時使用不同的對應方式,例如按位置對應部分參數,按名稱對應部分參數,按順序對應剩余參數。

下面是一個混合對應方式的示例:

module test_module(input A, input B, output C);

// Module implementation

endmodule

module top_module();

wire out_signal;

test_module dut(.A(in_signal_A), in_signal_B, .C(out_signal));

// Module instantiation

endmodule

endmodule

endmodule在這個示例中,我們使用混合對應方式實例化了test_module。在端口對應的位置,我們按名稱對應了參數in_signal_A和out_signal,而參數in_signal_B則是按順序對應的。

綜上所述,Verilog中的模塊端口對應方式包括按位置、按名稱、按順序和混合四種方式。每種對應方式都有各自的特點和適用場景,可以根據實際需求選擇最合適的方式。在實際的Verilog設計中,經常需要使用模塊進行層次化設計和模塊重用,而對模塊端口的正確對應方式使用則是確保設計正確和高效的關鍵。

-

模塊

+關注

關注

7文章

2725瀏覽量

47610 -

Verilog

+關注

關注

28文章

1351瀏覽量

110187 -

端口

+關注

關注

4文章

983瀏覽量

32121 -

數字電路

+關注

關注

193文章

1610瀏覽量

80709

發布評論請先 登錄

相關推薦

verilog調用模塊端口對應方式

verilog調用模塊端口對應方式

評論