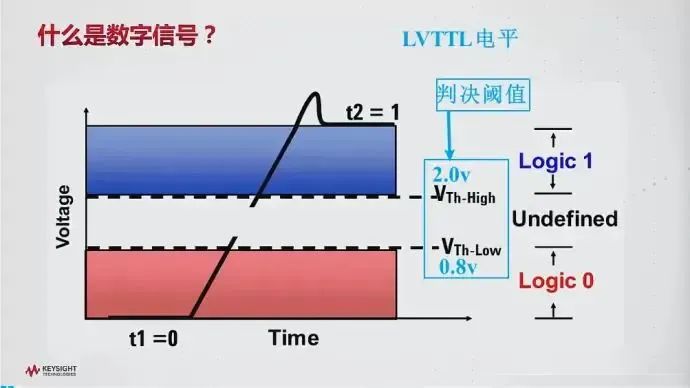

數字信號進入高速狀態時,不再是0-1這樣方方正正的標準形式。

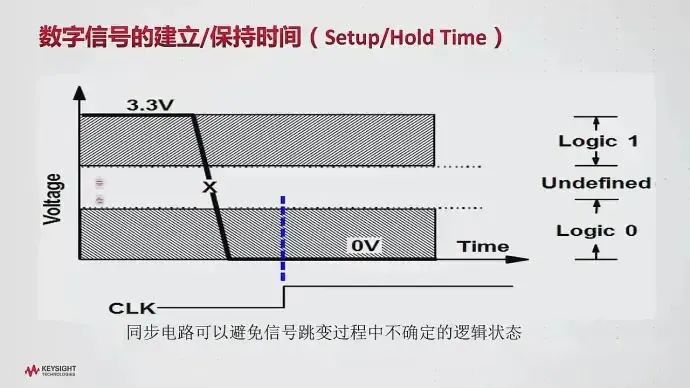

除了電平的影響以外還有時間的影響,采樣的時候與數據時序要有一個基本的要求,采樣與跳變的時間要有一定的時間間隔,以保證在采樣時不采樣到跳變。

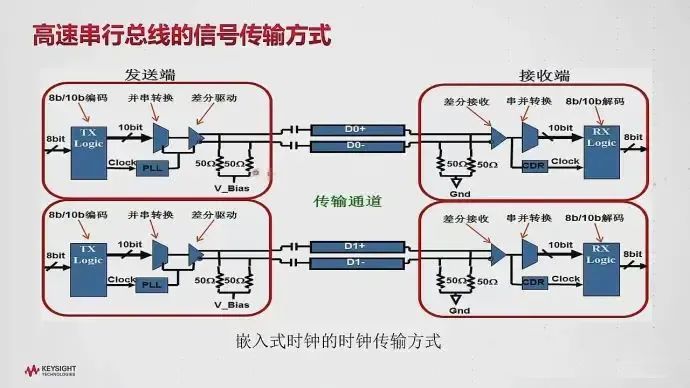

使用串行高速總線,好處:1.省線; 2.不是必要有時鐘總線,布線時不需要考慮線長。

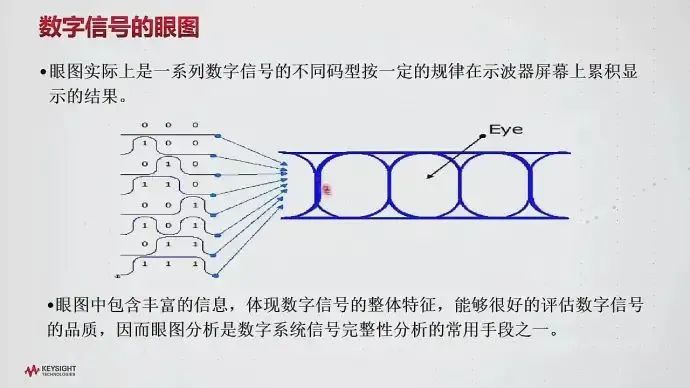

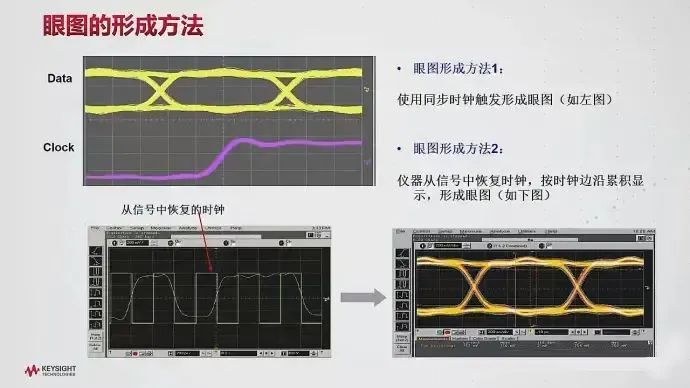

串行總線是通過數據編碼,把時鐘存在數據流中(眼睛越大越好)。

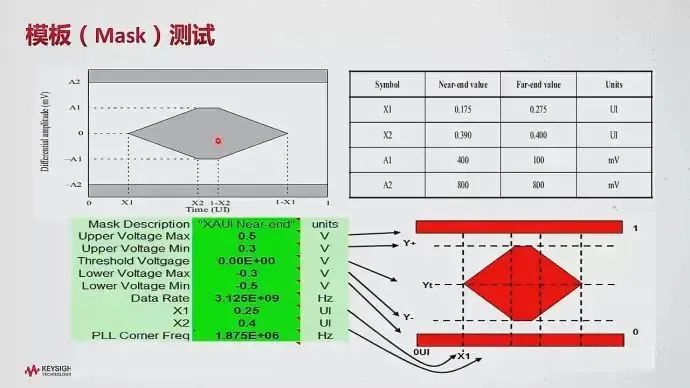

模板測試

眼圖壓模板表示信號完整性不好

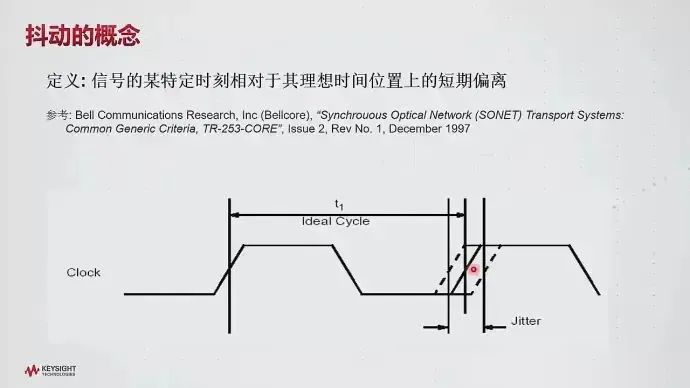

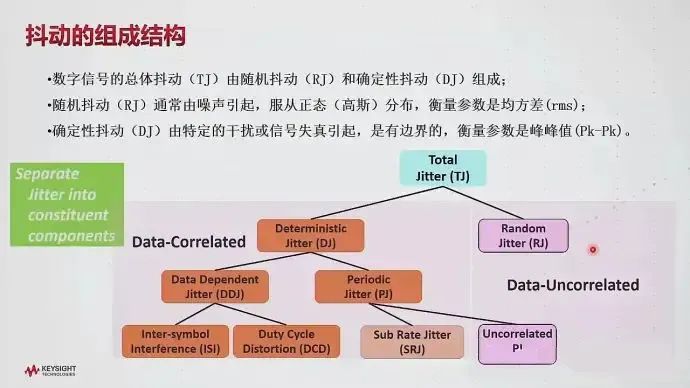

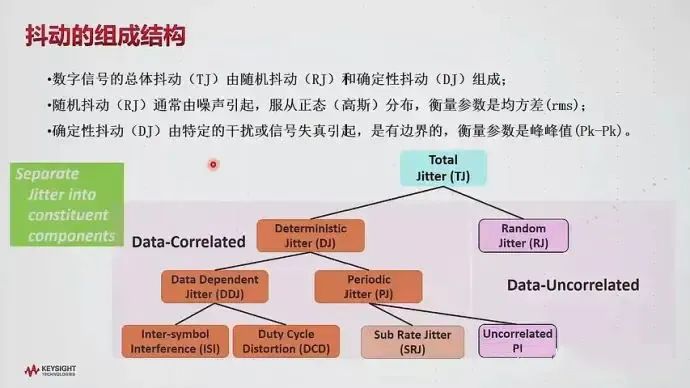

抖動分析模型

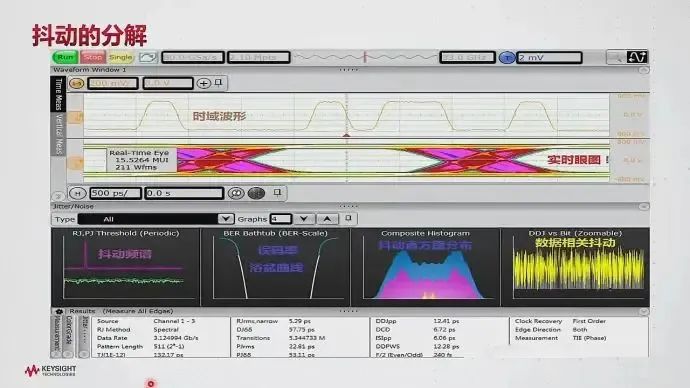

利用示波器上的軟件對抖動分解,分析抖動原因。

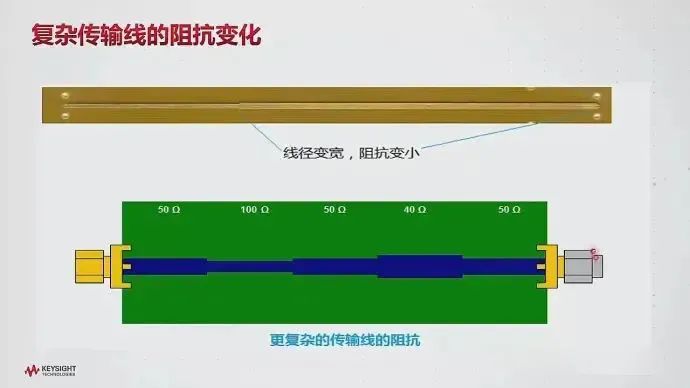

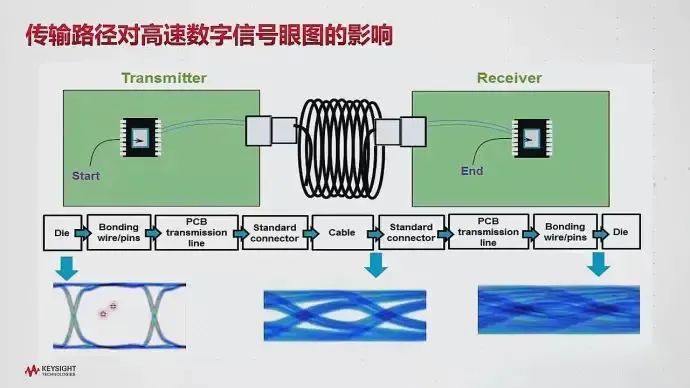

傳輸線阻抗連續(匹配),可以減少反射。

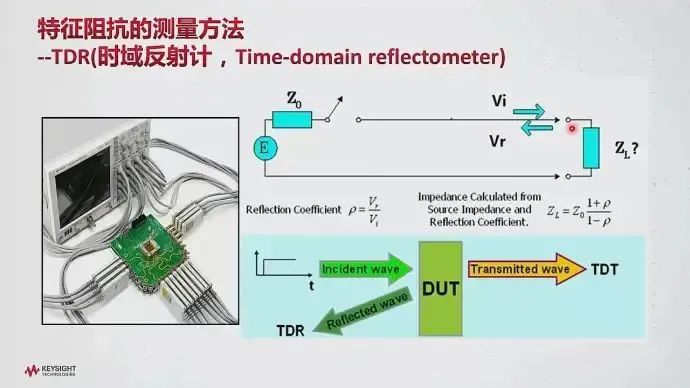

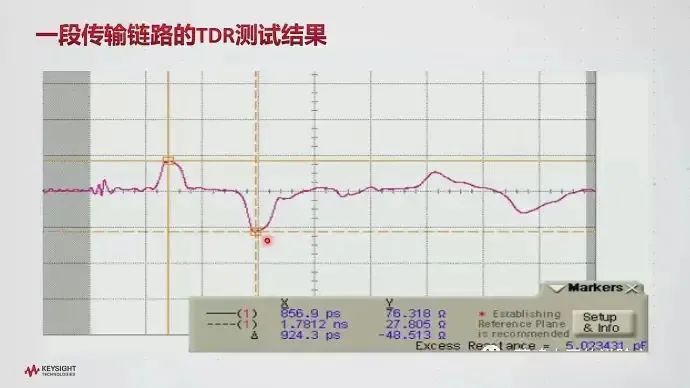

根據反射回來的時間可以判斷離我距離,根據反射回來的電壓和反射系數可以判斷阻抗,一般在峰值點處的的阻抗匹配不好。

阻抗是連續均勻的也不一定最好,要考慮傳輸損耗,所以除了要控制阻抗,也要控制損耗。

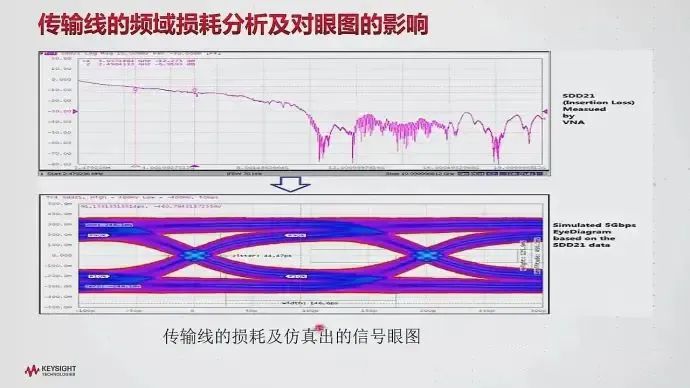

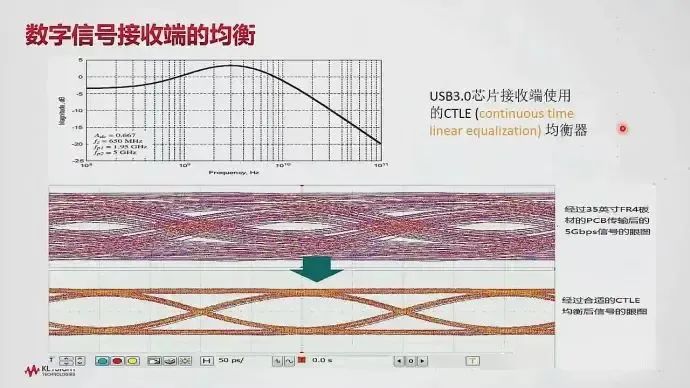

隨著頻率增加損耗增加,根據損耗曲線可以了解傳輸線的質量,可以根據眼圖預知在固定頻率的傳輸效果,或者提前使用信號損耗補償技術(預加重和補償)。

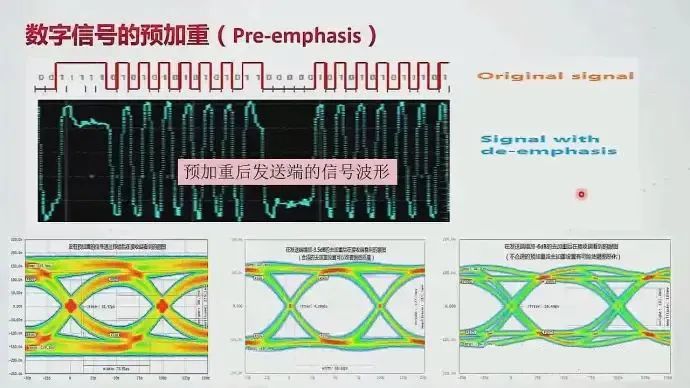

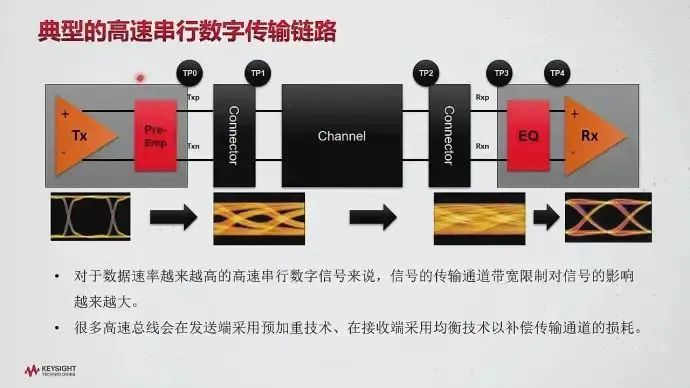

預加重,高頻成分更容易損失,所以在發送的時候把高頻成分預先加重(幅度加大)(增強),但是預加重的值的設置要和電路相匹配,避免過度補償,因此目前常常采用多種預加重。

接收端做補償,叫做均衡(比如CTLE:連續時間線性均衡,還有DFE等均衡方法)。

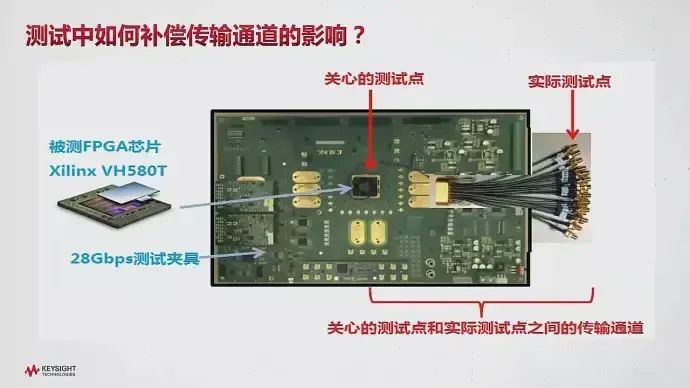

實際測試中,不同管腳由于傳輸通道,也會有損耗,這時就需要補償方法(去嵌):實際先把傳輸通道的S參數求出來,然后在測量中使用軟件處理補償。

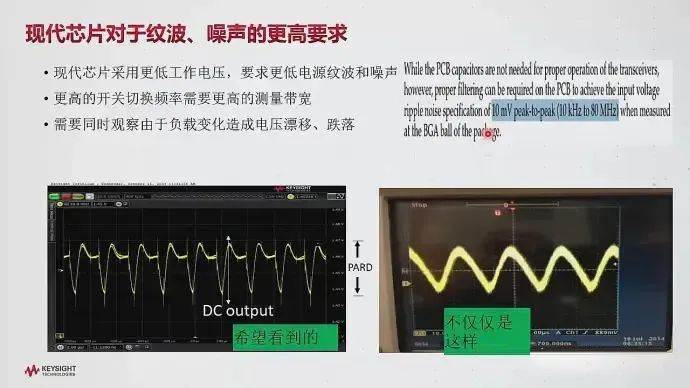

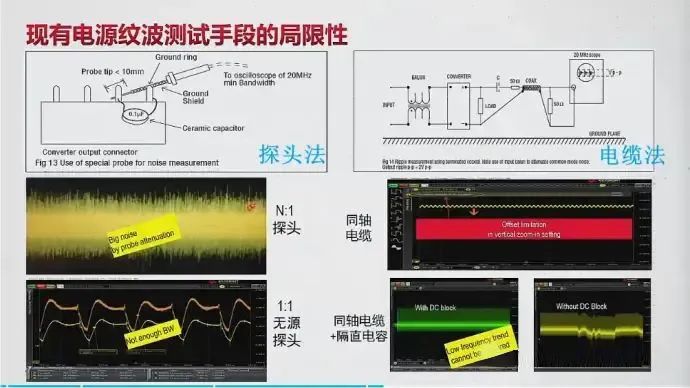

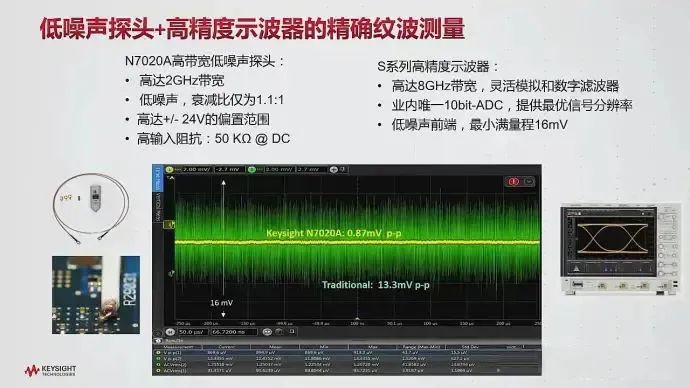

探頭一般都是有衰減的,但是示波器知道,示波器顯示的時候會放大的,但是這種很難測到很低的噪聲(在示波器底噪就很大),用無源的探頭不會衰減,但是他的匹配就很難,一種改進方法是使用同軸電纜,一端擰在示波器上,一端剝開,然后點在或者焊在電路上,會得到比較好的測量效果,但是由于要測的電源都是有直流的,如果要測2.5v或者3.3v上面很小的紋波,要把刻度打到很小,但是現在很多示波器的偏置范圍在小量程下是不足以把信號拉回來的,可以加隔直電容,但是頻率特性就不能很好的說出來了。

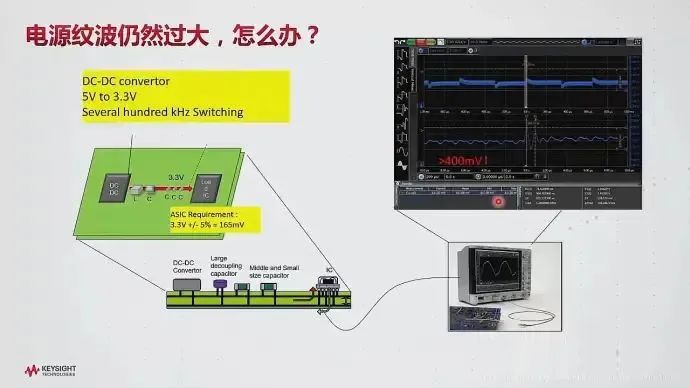

DCDC有幾百KHz的開關頻率,就有幾百KHz的紋波,峰值有400多mV,芯片本身有100多mV。

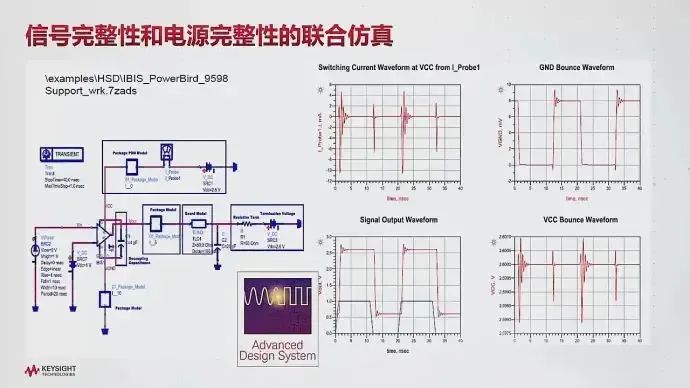

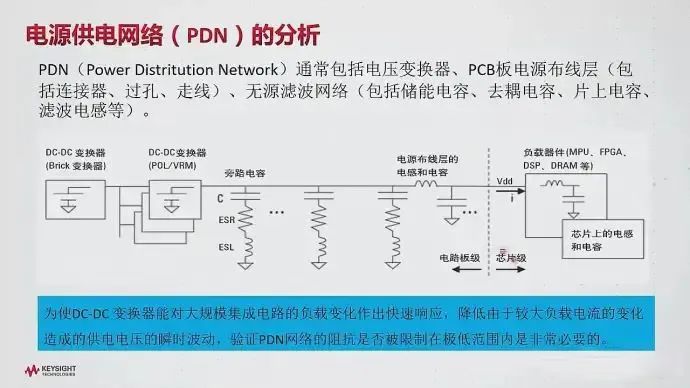

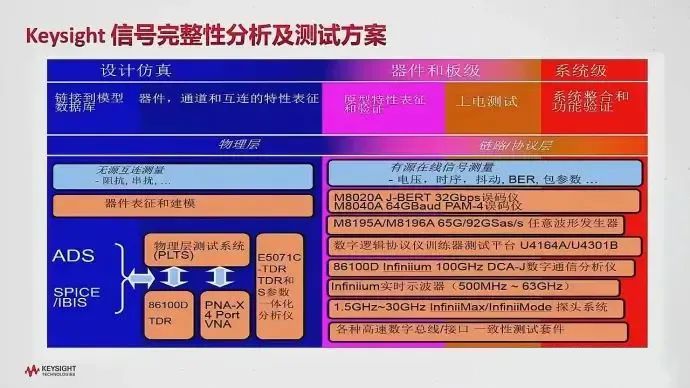

以前的電路芯片模型不支持聯合仿真,只支持信號完整性仿真或電源,不能同時仿真,目前支持電源網絡(低阻抗)的S參數的聯合仿真,通過這種方式盡可能改善電源和信號之間的互相影響。

網絡不能把DCDC產生的紋波給充分的濾掉,可能濾波電容不夠大,或者濾了低頻沒濾高頻,電容有寄生電阻和寄生電感,在低頻的情況下,跟一個電感差不多,沒有濾波的效果,所以要優化濾波的網絡。

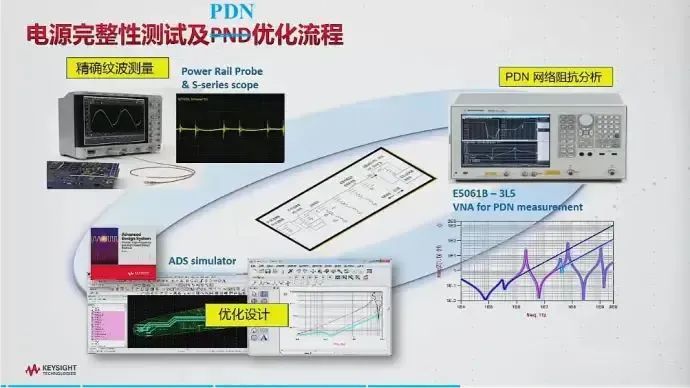

Chrent電源完整性測試和PDN優化流程

1.先用示波器對電源紋波進行測試,如果滿足要求最好,不滿足就進行上面的改進方法,比如換沒有衰減的探頭,用同軸電纜測量等等。

2.還不行就PDN網絡進行分析,使用矢網在不同頻率下測量PDN網絡的阻抗,如果在不同頻率下的阻抗都很低,說明他的濾波效果很好,如果在低頻情況下阻抗很低,但是高頻情況下阻抗很高,那么濾波效果不好,需要在某些頻點進行一些改善。

一般的網絡分析儀的起始頻點都是從幾百K或者幾十M開始,而對于電源分析感興趣的頻點通常都在幾Hz到幾十K有的時候到幾百M,在優化過程中,把現有的PDN網絡導進去,然后設置一個目標,比如幾K赫茲到1M的頻率范圍內,我們的阻抗都要小于0.5Ω,讓仿真軟件自動優化,在哪些位置放電容更有效,節省器件成本和空間。

Chrent答 疑

1.平行布線怎么解決串擾問題?

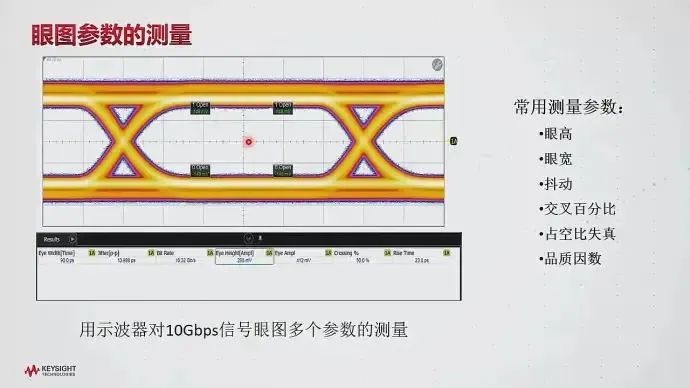

很多高速的走線在傳輸過程中都會產生EMI輻射,因此平行走線會帶來串擾,因此是高速信號研究要解決的一個重要的問題;1. 屏蔽:放在不同的層里,然后用地線隔開;2. 線之間的距離盡量遠一點,從測量的角度來看,可以使用示波器的串擾分析軟件,分析串擾對眼圖的影響(眼高和眼寬)。

2.抖動都是示波器根據自己的算法分析出來的嗎?是不是不同的示波器會有不同的結果?

是的,目前業內多采用雙狄拉克模型的方法對信號的抖動進行分析和分解,確實可能會存在不同的示波器廠家采用的分析和分解的算法有所差異,不同的示波器的底噪聲也是不一樣的,在某些長河可以通過一些手段來提高抖動測量的精度,比如信號中發重復性的碼型,可以對信號進行反復的平均,這樣對碼間干擾的測量和分解精度就會更高。

3.眼圖很好的話是不是說數字信號沒有問題?

眼圖本身是一個定性的分析工具,因此還會進行模板工具進行定量的測試,還會對抖動進行分析和分解,因為產品規范里面除了會定義眼圖模板的測試以外,還會定義信號里面隨機抖動、確定抖動、碼間干擾不能超過多少,因此眼圖可以作為一個快速的定性的判斷手段,但是眼圖并不是唯一的手段。

4.如果無法進行模板測試,還有什么手段可以判斷信號的完整和信號的正確性?

對于一些低速的數字信號,只需要對一些波形的參數,比如幅度、上升沿、下降時間、周期的測量,但是對于一些高速的總線對信號的質量的判斷一般都是對眼圖,模板,抖動,進行判斷和測試的,如果是并行總線根據時鐘一定是能做出時鐘的,如果是串行的話,可能有些示波器沒有時鐘恢復的選件,但是也可以用信號自身出發簡單看一下,但是最好是測試一下。

5.測量高頻信號的時候怎么避免測量造成的干擾,比如探頭衰減的干擾,探頭線長的干擾,用普通無源探頭會有多大影響?

這個實際是是在問怎么選擇合適的探頭,要關注探頭的帶寬,探頭的等效的電阻和電容,以及前端電感長度的電感的影響,以及如何彌補電感的影響,對于探頭前端的選擇可以看現代示波器高級應用。

6.一致性要怎么配合示波器和軟件?

一致性測試專門指某些總線的一致性測試,USB、PCIe、PXI總線,這些通常分為發送端和接收端的測試,發送端的測試主要是示波器,接收端的測試主要是誤碼儀,

示波器(四個)的帶寬,不同的總線的要求不一樣,比如USB3.0要12.5G帶寬,PCIe3.0也要12.5G帶寬,PCIe4.0需要20G以上(或者25G)的帶寬等等,一致性測試軟件(示波器自帶的),探頭或者電纜,連接和測試夾具,每一種總線都有不同的配置。

7.眼圖太差了,如何判斷是哪些問題呢?

首先確定測試方法是正確的,比如使用正確的時鐘進行恢復,對信號疊加的,如果仍然很差,檢查一下發送端到接收端的阻抗是不是連續的,傳輸通道是不是損耗太大了,比如對不同頻點的損耗到底有多大,優化PCB布線或者阻抗等等。

8.預加重對信號的補償和均衡只能通過眼圖來判斷是否合適嗎?

預加重與均衡和測量沒有關系,是在信號里面使用的,示波器是參考均衡器,和規范對比來觀察眼圖,我們是為了看發送端傳輸到接收端之后在經過均衡的波形。

9.關于測試點,由于高速信號中作為測試點的過孔和焊盤會導致阻抗不連續,以及等效電容的問題,該怎么處理?

需要仿真軟件做仿真,同時和PCB流片廠家溝通。

10.LVDS信號的測試(速率200M)

根據信號的上升沿實際上升時間計算,如果上升沿特別的陡,可能需要8G或10幾G的帶寬示波器才能測得準,如果上升沿比較緩,可能1G帶寬就夠了,另外由于LVDS信號是差分的,可能需要差分的探頭進行測試,同時要注意LVDS信號在接收端通過需要100Ω端接一下,同時LVDS有專門的時鐘,用時鐘來進行觸發,看信號的眼圖。

11.串行通信信號時鐘恢復有什么需要注意的?

環路帶寬的選擇,一般用示波器軟件的PRL,她可以跟蹤一定頻率范圍內的信號抖動,如果PRL的環路帶寬是一階的還是二階的,他的環路帶寬是1M的還是2M的還是10M,設置的不對,看到的眼圖和抖動就不一樣了,所以在設置環路帶寬的時候應該參考規范。

12.用同軸電纜測量紋波,示波器內部用AC耦合方式測量,這種方式有什么缺點嗎?

如果示波器使用AC耦合,示波器輸入阻抗通常是1M歐姆,因為有些示波器比如1GHz的可以在1M歐姆和50歐姆之間進行切換的,通常AC耦合時是在1M歐姆情況下的,50歐姆一般是DC耦合,把示波器打到AC耦合時,1M歐姆的阻抗和電纜50歐姆的阻抗不太匹配,如果做低頻紋波的測試影響不大,但是高頻下噪聲可能測不準,1M歐姆的底噪也是比50歐姆要高一些,AC耦合的情況下看不到直流的變化,比如電壓的漂移是看不到的。

13.在紋波測試時,要注意探頭的地環路盡可能的小,一般不要用鱷魚夾那種

它在空間上有很大輻射(相當于天線有很高的電磁干擾),用探頭或者小環路的金屬探針,避免空間的電磁輻射,噪聲(熱噪聲=KTB(K是玻爾茲曼常數,T是溫度,B是帶寬))是和帶寬成正比的一個量,所以全帶寬的底噪聲一定是要設置成相對應的(有標準,沒有特殊說明可以打20M帶寬),也可通過數字濾波來實現。

14.在測試過程中,可能因為帶寬不夠可能產生虛假的信號?

有可能探頭前面的引線太長了,造成了信號的震蕩或者不正確的過充,也可能是示波器帶寬不夠引起不正確過充,有可能引起信號的抖動或者上升沿的哆嗦(高頻分量混到低頻了),上升時間是不是合適判斷一下,更好的方式是用更高的帶寬來測試對比一下,直接就判斷出來了。

-

電源

+關注

關注

184文章

17805瀏覽量

251034 -

信號完整性

+關注

關注

68文章

1412瀏覽量

95546 -

數字信號

+關注

關注

2文章

975瀏覽量

47604

發布評論請先 登錄

相關推薦

聽懂什么是信號完整性

高速信號完整性與電源完整性(內含答疑)

高速信號完整性與電源完整性(內含答疑)

評論