2021 年,JEDEC 宣布發布 JESD79-5 DDR5 SDRAM 標準,標志著行業向 DDR5dual-inline memory modules(DIMM) 的過渡。DDR5 內存帶來了許多關鍵的性能提升,以及新的設計挑戰。計算系統架構師、設計人員和購買人員都想知道 DDR5 與 DDR4 有什么新功能,以及他們如何充分利用新一代內存。

本文內容:

DDR5 與 DDR4 有什么變化?

DDR5 面臨哪些設計挑戰?

DDR5 內存接口芯片組如何利用 DDR5 for DIMM 的優勢?

性能:DDR5 與 DDR4 DRAM 有什么變化?

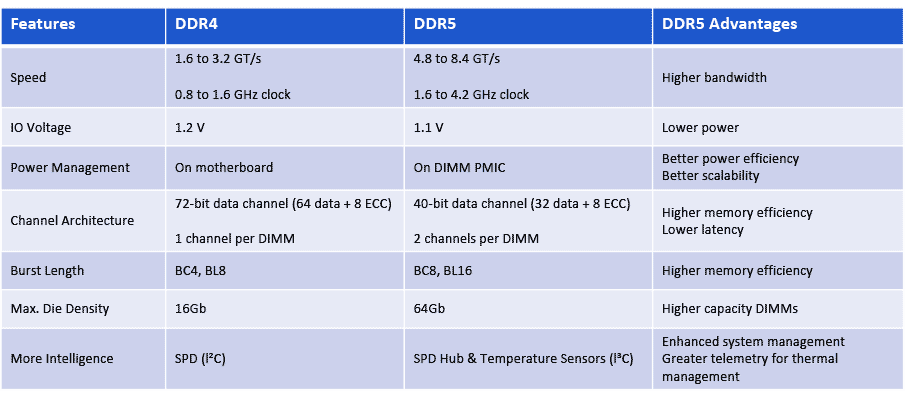

從 DDR4 到 DDR5 DIMM 過渡中的七個最重要的技術指標改進如下表 1 所示。

表 1.DDR5 的變化和相對于 DDR4 DIMM 的優勢

1. DDR5 可擴展至 8.4 GT/s

您永遠無法擁有“足夠”的內存帶寬,而 DDR5 有助于滿足對速度的永不滿足的需求。DDR4 DIMM 在 1.6 GHz 的時鐘速率下最高可達 3.2 千兆傳輸/秒 (GT/s),而初始 DDR5 DIMM 的帶寬增加了 50%,達到 4.8 GT/s。DDR5 中集成了決策反饋均衡 (DFE) 等新功能,可實現更高的 IO 速度和數據速率。

2. 較低的電壓使電源保持在可控范圍內

第二個主要變化是工作電壓 (VDD) 的降低,這有助于抵消以更高速度運行帶來的功耗增加。使用 DDR5(DRAM)時,寄存器時鐘驅動器 (RCD) 電壓從 1.2 V 降至 1.1 V。命令/地址 (CA) 信號從 SSTL 更改為 PODL,其優點是當引腳停放在高電平狀態時不會消耗靜態功耗。

3. DDR5 DIMM 全新電源架構

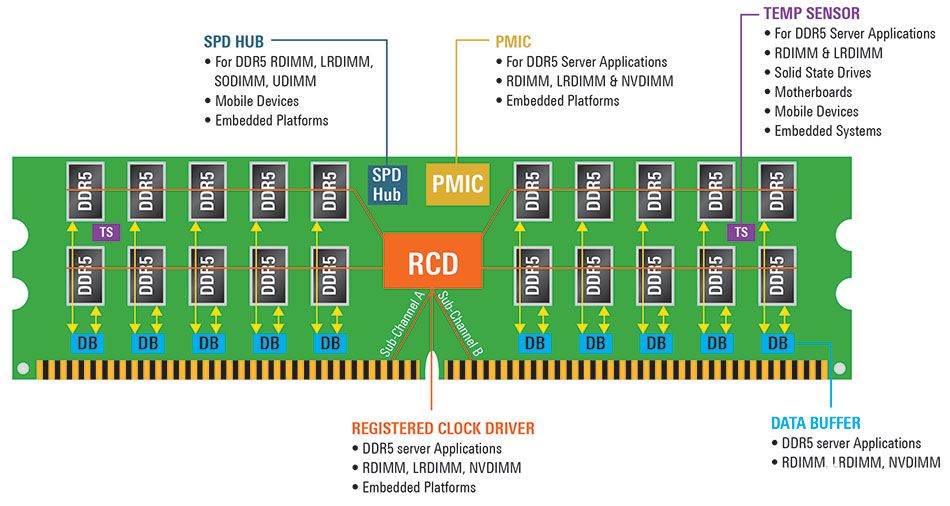

第三個變化,也是一個重要的變化,是電源架構。使用 DDR5 DIMM,電源管理從主板轉移到 DIMM 本身。DDR5 DIMM 將在 DIMM 上配備 12V 電源管理 IC (PMIC),從而實現更好的系統電源負載粒度。PMIC分配1.1 V VDD電源,通過更好的DIMM電源控制,幫助提高信號完整性和噪聲。

4. DDR5 與 DDR4 通道架構

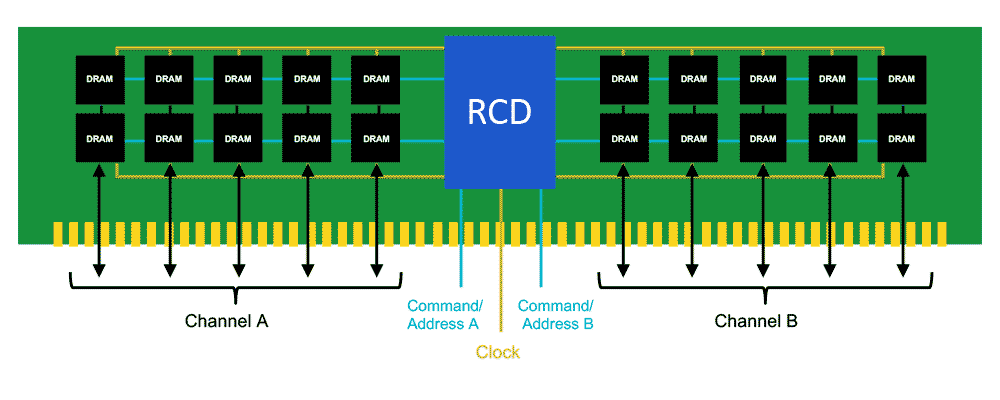

DDR5 的另一個重大變化是新的 DIMM 通道架構,這是我們列表中的第四位。DDR4 DIMM 具有 72 位總線,由 64 個數據位和 8 個 ECC 位組成。使用 DDR5 時,每個 DIMM 將有兩個通道。每個通道的寬度為 40 位:32 個數據位和 8 個 ECC 位。雖然數據寬度相同(總共 64 位),但具有兩個較小的獨立通道可提高內存訪問效率。

在 DDR5 DIMM 體系結構中,DIMM 的左側和右側(每個都由一個獨立的 40 位寬通道提供服務)共享 RCD。在 DDR4 中,RCD 每側提供兩個輸出時鐘。在 DDR5 中,RCD 每側提供四個輸出時鐘。在具有 x4 DRAM 的最高密度 DIMM 中,這允許每組 5 個 DRAM(單列、半通道)接收自己的獨立時鐘。為每個列和半通道提供一個獨立的時鐘可提高信號完整性,有助于解決降低VDD引起的低噪聲容限問題(來自上表的變化#2)。

5. 更長的Burst Length

第五個主要變化是Burst Length。DDR4 burst chop length為 4,burst length為 8。對于 DDR5,burst chop length和burst length將擴展到 8 和 16,以增加突發有效載荷。burst length為 16 (BL16),允許單個burst 訪問 64 字節的數據,這是典型的 CPU cache line大小。它只能使用兩個獨立通道中的一個來執行此操作。這顯著提高了并發性,并且具有兩個通道,具有更高的內存效率。

6. DDR5 支持更高容量的 DRAM

第六個值得強調的變化是 DDR5 對更高容量 DRAM 設備的支持。借助 DDR5 buffer chip DIMMs,服務器或系統設計人員可以在單芯片封裝中使用高達 64 Gb 的密度 DRAM。DDR4 采用單芯片封裝 (SDP) 的最大容量為 16 Gb DRAM。DDR5 支持片上 ECC、錯誤透明模式、封裝后修復以及讀寫 CRC 模式等功能,以支持更高容量的 DRAM。更高容量DRAM設備的影響顯然會轉化為更高容量的 DIMM。因此,雖然 DDR4 DIMM 的容量高達 64 GB(使用 SDP),但基于 DDR5 SDP 的 DIMM 是 DDR5 的四倍,達到 256 GB。

7. 配備 DDR5 的更智能的 DIMM

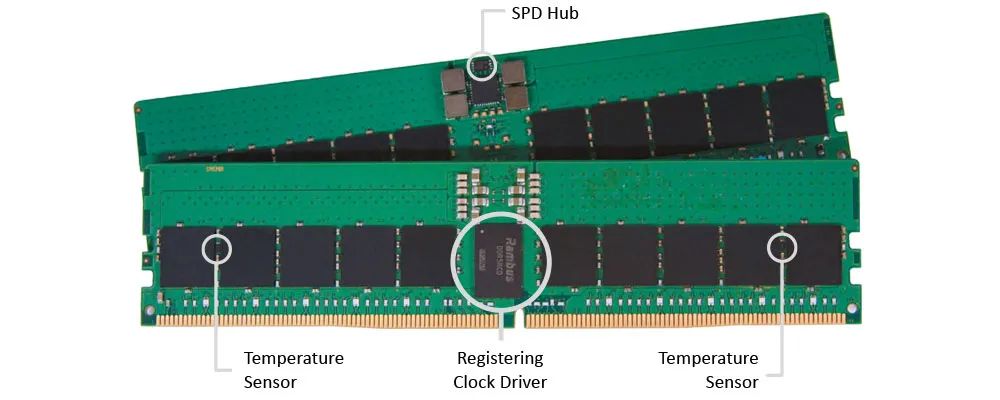

DDR5 服務器 DIMM 芯片組用SPD Hub IC 取代了 DDR4 SPD IC,并增加了兩個溫度傳感器 (TS) IC。SPD Hub具有集成的 TS,它與兩個分立的 TS IC 結合使用,提供來自 RDIMM 的三個熱遙測點。

借助 DDR5,芯片之間的通信總線升級到 I3C,其運行速度比 DDR4 中使用的 I2C 總線快 10 倍。DDR5 SPD Hub處理從模塊到基板管理控制器 (BMC) 的通信。DDR5 SPD 集線器使用更快的 I3C 協議,可縮短初始化時間,并支持更高的輪詢率和實時控制。

從 SPD 集線器傳送到 BMC 的散熱信息可用于管理冷卻風扇速度。現在可以更精細地管理 DRAM 刷新率,以提供更高的性能或更高的保留時間,如果 RDIMM 運行過熱,可以根據需要限制帶寬以降低熱負載。

DDR5 的設計挑戰是什么?

DDR5 的這些變化引入了許多設計考慮因素,以應對更高的速度和更低的電壓,從而引發了新一輪的信號完整性挑戰。設計人員需要確保主板和 DIMM 能夠處理更高的信號速度。在執行系統級仿真時,需要檢查所有DRAM位置的信號完整性。

對于 DDR4 設計,主要的信號完整性挑戰在于雙數據速率 DQ 總線,而對低速命令地址 (CA) 總線的關注較少。對于 DDR5 設計,即使是 CA 總線也需要特別注意信號完整性。在 DDR4 中,考慮使用差分反饋均衡 (DFE) 來改進 DQ 數據通道。但對于 DDR5,RCD 的 CA 總線接收器也需要 DFE 選項,以確保良好的信號接收。

主板上的供電網絡 (PDN) 是另一個考慮因素,包括帶有 PMIC 的 DIMM。考慮到更高的時鐘和數據速率,您需要確保 PDN 能夠處理以更高速度運行的負載、良好的信號完整性以及為 DIMM 提供良好的清潔電源。

從主板到 DIMM 的 DIMM 連接器也必須處理新的時鐘和數據速率。對于系統設計人員來說,在印刷電路板 (PCB) 周圍的時鐘速度和數據速率較高的情況下,必須更加重視系統設計的電磁干擾和兼容性(EMI 和 EMC)。

DDR5 內存接口芯片組如何利用 DDR5 for DIMM 的優勢?

好消息是 DDR5 內存接口芯片提高了從主機內存控制器發送到 DIMM 的命令和地址信號的信號完整性。兩個通道中每個通道的總線都流向 RCD,然后扇出到 DIMM 的兩半。RCD 有效地減少了主機內存控制器看到的 CA 總線上的負載。

包括 SPD Hub 和 TS 在內的擴展芯片組可實現更智能的 DIMM,它可以在 DDR5 的更高數據速率下運行,同時保持在所需的功率和散熱范圍內。

Rambus 提供 DDR5 內存接口芯片組,可幫助設計人員充分利用 DDR5 的優勢,同時應對更高數據、CA 和時鐘速度帶來的信號完整性挑戰。Rambus 是業內第一家提供 DDR5 RCD 至 5600 MT/s 的公司,并不斷提高其 DDR5 解決方案的性能,以滿足不斷增長的市場需求。Rambus DDR5 RCD 現已達到 7200 MT/s 的性能水平。

審核編輯:劉清

-

DRAM

+關注

關注

40文章

2315瀏覽量

183483 -

接收器

+關注

關注

14文章

2470瀏覽量

71907 -

DDR4

+關注

關注

12文章

321瀏覽量

40793 -

RCD

+關注

關注

1文章

105瀏覽量

27573 -

DDR5

+關注

關注

1文章

422瀏覽量

24145

原文標題:DDR5 vs DDR4 DRAM – 優勢和設計挑戰

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DDR5內存普及率不高,是PMIC的鍋?

新一代DDR5內存模組密集發布,支持DDR5 CPU隨后就到!

內存條ddr4和顯卡ddr5

DDR5內存和DDR4內存差異總結

DDR5內存將在明年實現量產

什么是驅動DDR5 有什么新功能

RMBS擴大面向數據中心和PC設備的DDR5內存接口芯片組合

ddr5的主板可以用ddr4內存嗎 幾代CPU才能上DDR5

XMP DDR5 8000內存性能測試詳解

DDR5內存接口芯片組如何利用DDR5 for DIMM的優勢?

DDR5內存接口芯片組如何利用DDR5 for DIMM的優勢?

評論