本土RISC-VCPUIP領軍企業——芯來科技正式發布基于RISC-V指令集的高性能商業處理器CPUIP——UX1000系列,為高性能處理器內核提供了RISC-V CPU IP的國產自主選擇。

在網絡、通信和AI高速發展的時代,下游智能設備的應用對處理器性能和算力需求不斷提升。開放標準的RISC-V指令集架構由于其靈活性和擴展性,近年來生態發展速度非常迅猛,在各類應用場景遍地開花,高性能領域也不斷在突破。 芯來科技此次全新發布的UX1000系列是擁有多譯碼寬度、亂序發射與執行能力的64位高性能應用處理器,主要針對網絡處理、人工智能、自動駕駛、數據中心加速卡、高性能移動設備等應用,進一步滿足了本土當下日益高漲的國產高性能處理器IP需求。

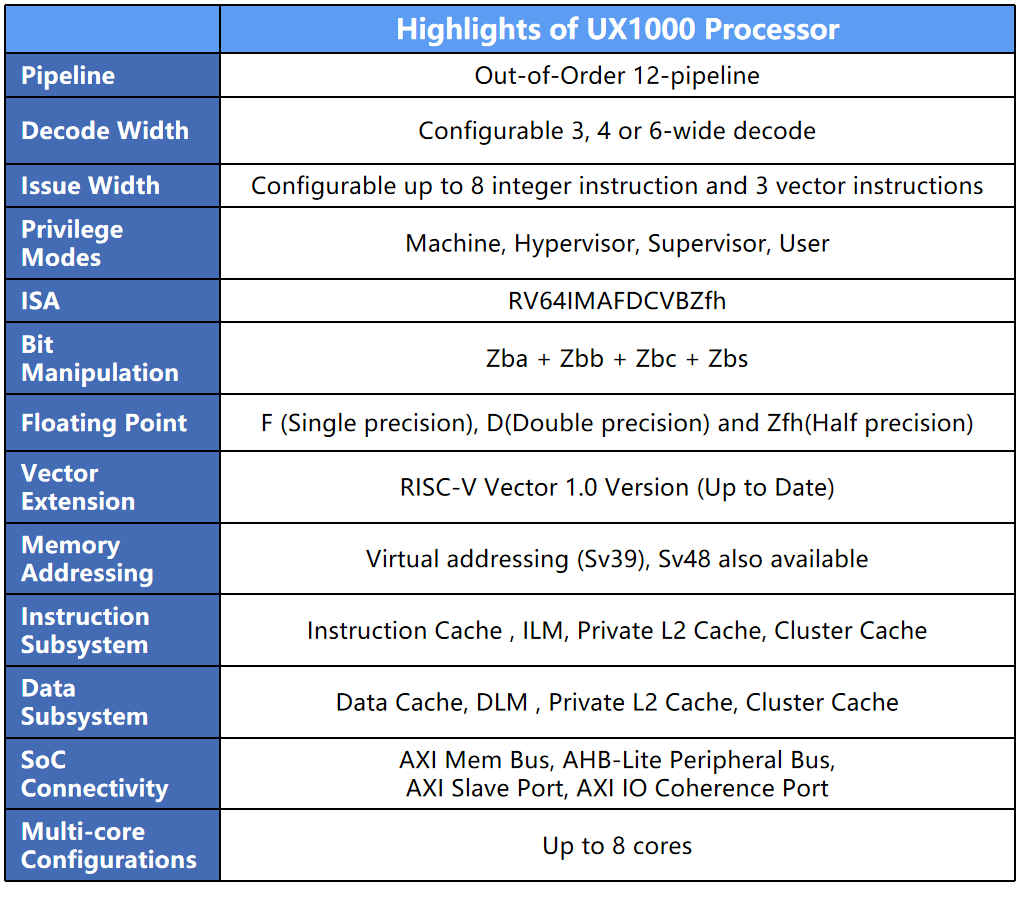

UX1000系列擁有高度可配置的流水線,用戶可根據不同性能需求進行選擇,為系統設計提供了較強的靈活度:

UX1000系列有三種不同的配置分類:UX1030、UX1040和UX1060 UX1030:3譯碼寬度的處理器

擁有較好的性能和較低的面積功耗

UX1040:4譯碼寬度的處理器

擁有較高的性能以及優秀的面積功耗

UX1060:6譯碼寬度的處理器

擁有更高的性能,主要面對高性能應用領域

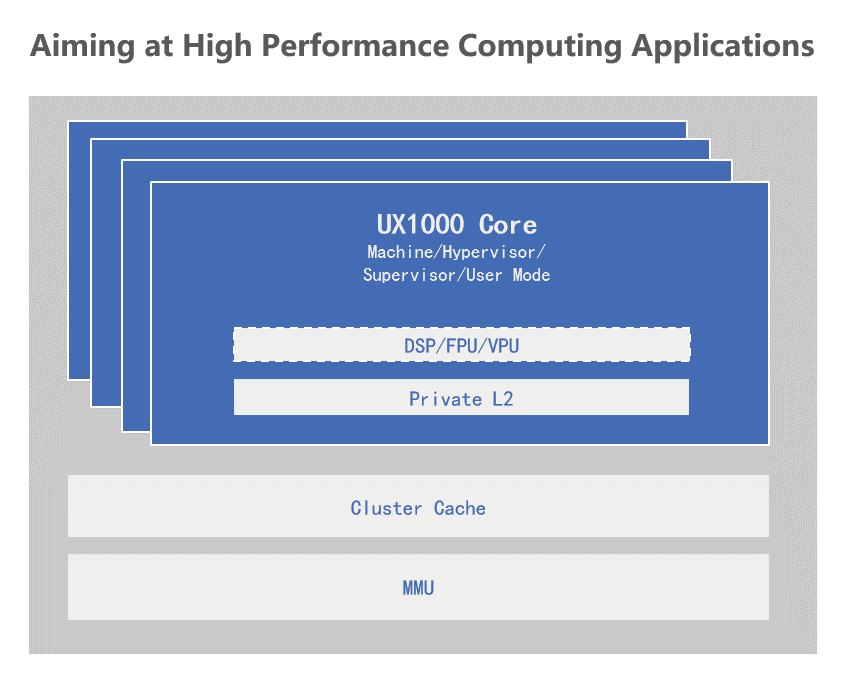

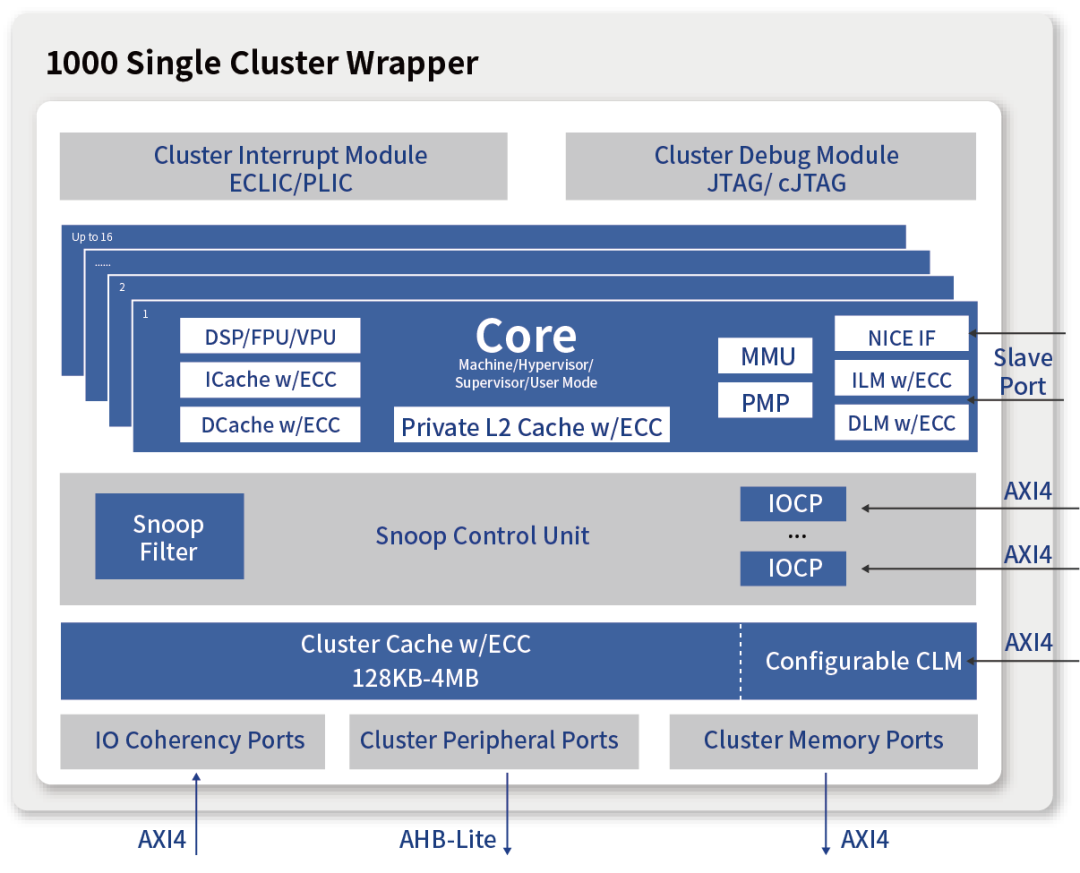

UX1000系列單Cluster支持多種可配特性:

UX1000系列單Cluster可以配置SMP多核,且支持最多3級緩存。

單核特性

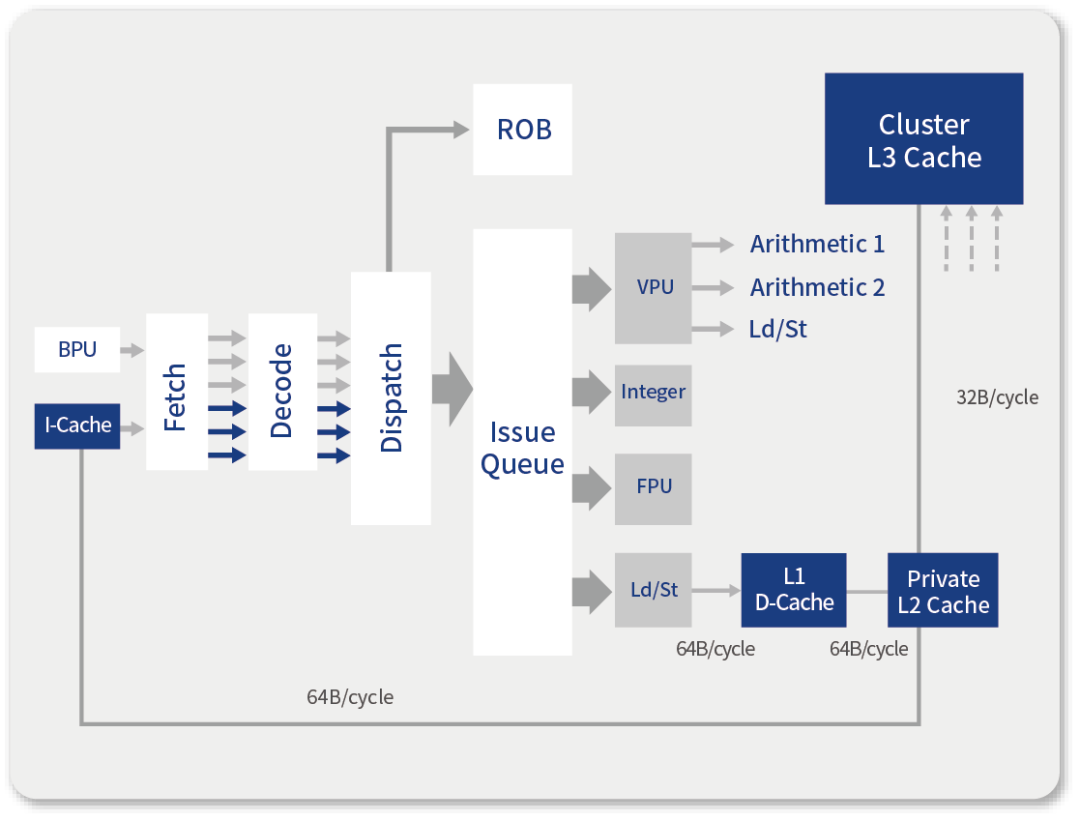

UX1000系列處理器基于RISC-V RV64IMAFDCVBKZfh并嚴格遵循RISC-V標準指令的12級流水線亂序執行處理器;

UX1000具備較強算力,支持每周期最多達10條標量指令和2條矢量指令的發射寬度(Issue Width);

可配置的指令與數據緩存(ICache / DCache)與片上SRAM(ILM / DLM)且支持ECC;

在內存訪問設計上,UX1000支持了私有L2緩存,提供更高效的數據讀取存儲能力;

支持嚴格按照RISC-V Vector1.0標準的VPU矢量計算單元,擁有2條計算流水線單元和1條數據讀寫流水線,可配置128b / 256b的VLEN,支持INT8 / 16 / 32 / 64以及BF16 / F16 / F32 / F64數據類型。

多核可配置特性

支持最多一個Cluster 8核及緩存一致性;

可配置私有L2和Cluster Cache;

可配置IO一致性接口(IOCP),在IOCP接口的幫助下,外部Master(例如NPU、加速器、PCIe、DMA等)可以和Core以及Cluster緩存共享數據讀取,并保持緩存一致性;

Cluster Cache支持SECDED ECC;

支持將Cluster Cache配置成Cluster Local Memory,并且可以支持CLM接口。

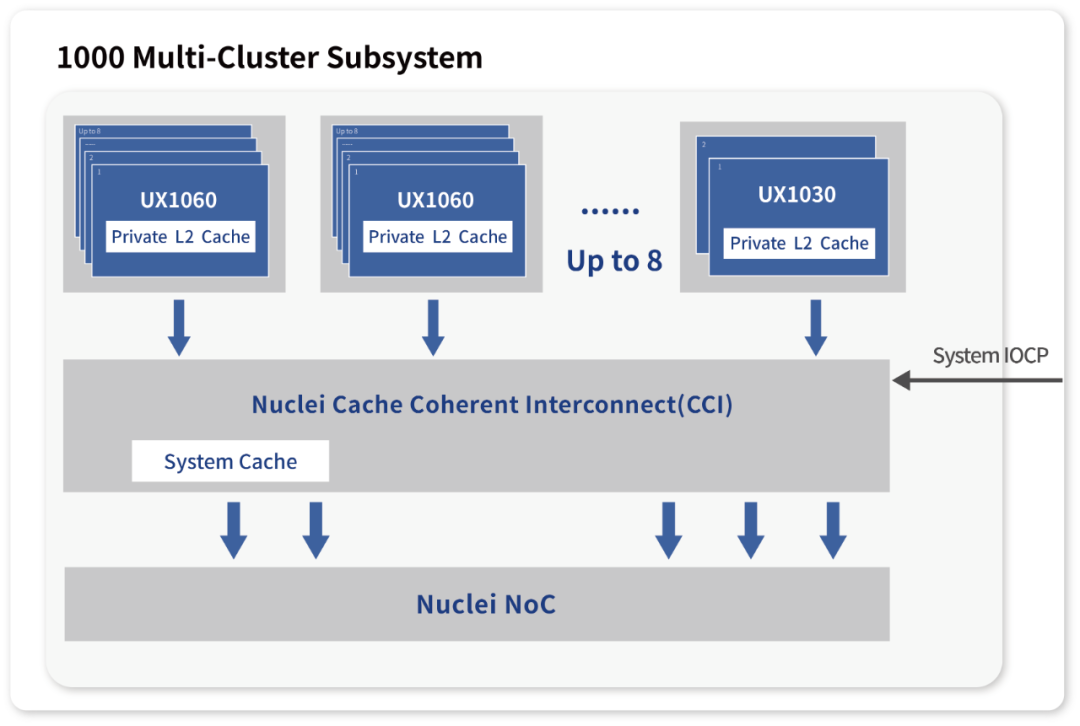

UX1000系列多Cluster可配特性

UX1000系列支持多Cluster配置,為高端SoC提供更強大的CPU主控性能。

每個Cluster支持最多8核,每個核都可以單獨配置私有L2;

Nuclei-CCI:芯來自研的基于Cross-Bar的Coherent總線,應用于Multi-Cluster場景;

Cluster之間支持緩存一致性

異構多Cluster模式(每個Cluster可以靈活配置不同內核)

最多可以支持8個Cluster

支持系統級緩存SystemCache(L3Cache)

Nuclei-NoC:芯來自研的基于Mesh-NoC的Non-Coherent總線 UX1000的多Cluster系統同樣支持IO一致性接口(System-IOCP)

開啟亂序高性能篇章,持續推出更多RISC-VCPUIP產品

合抱之木,生于毫末;九層之臺,起于壘土。芯來科技自成立以來,相繼推出了100、200、300、600、900系列,為本土產業提供了一系列全棧的RISC-V CPU IP解決方案。此次推出的1000系列,進一步開啟了亂序高性能CPU的篇章。未來芯來科技將持續加大投入高性能RISC-V CPU IP研發,進一步充實國產RISC-V CPU IP的產品圖譜,賦能RISC-V生態在更多高性能應用領域落地,促進RISC-V在中國本土半導體設計產業的蓬勃發展!

▲ 芯來RISC-V CPU IP產品線

審核編輯:劉清

-

RISC-V

+關注

關注

45文章

2277瀏覽量

46159 -

芯來科技

+關注

關注

0文章

59瀏覽量

3009

原文標題:芯來科技發布1000系列內核,開啟亂序高性能篇章

文章出處:【微信號:nucleisys,微信公眾號:芯來科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯原推出新一代高性能Vitality架構GPU IP系列

性能更進一步,一體機主板CB4-X12-V0大有可為

英特爾將進一步分離芯片制造和設計業務

RFTOP進一步擴充波導同軸轉換器產品線

iPhone 15在美國市場需求進一步減弱

芯馳科技與IAR宣布進一步擴大合作

Melexis推出全新MLX81123芯片,進一步擴展LIN RGB系列產品線

西門子與微軟進一步擴展戰略合作關系

進一步解讀英偉達 Blackwell 架構、NVlink及GB200 超級芯片

TDK進一步擴充Micronas嵌入式電機控制器系列HVC 5x

瑞芯微RK3576|觸覺智能:開啟科技新篇章

芯來科技推出1000系列,進一步開啟了亂序高性能CPU的篇章

芯來科技推出1000系列,進一步開啟了亂序高性能CPU的篇章

評論