隨著電子技術的進步.FPGA邏輯電路能完成的功能越來越多,同樣也帶來了一個很大的問題,即邏輯電路的規(guī)模越來越大,這意味著RTL代碼到FPGA的映射、布局布線所花費的時間也越來越長。

如果代碼結構不合理,編寫隨意,沒有考慮到FPGA布局布線的可行性以及時序收斂的問題,那么很可能使時序收斂非常困難,更壞的情況是布局布線失敗(即place and route fail)。這種情況在大規(guī)模的設計、大規(guī)模的FPGA上更為常見,因此有必要專門有一個章來講RTL代碼的設計、電路結構的設計、大規(guī)模邏輯電路的技巧以及如何解決此類問題。

布局布線失敗

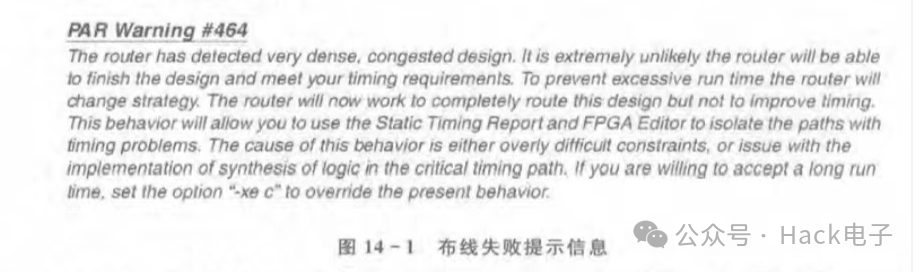

在某些FPGA中,特別是在大規(guī)模的FPGA(XilinxVirtex6以上,AlteraStratixIV以上)中實現(xiàn)大規(guī)模的設計,如果前期沒有對設計的邏輯電路做好結構優(yōu)化,同時不注意代碼風格,那么很可能會帶來一個問題:布局布線失敗。這種現(xiàn)象困擾著設計者因為一個大型的設計從綜合到布局布線通常需要花費十來個小時,有些甚至是一兩天的時間,而這種結果意味著這些時間將被極大地浪費。該現(xiàn)象一般在FPGA工具中會出現(xiàn)如圖14-1所示的信息。

圖14-1 布線失敗提示信息

圖14-1的大體意思是說布線工具(router)檢測到當前是一個非常密集(dense)擁塞(congested)的設計,布線工具有可能沒有辦法實現(xiàn)布線。這里的密集和擁塞是指什么呢?從字面上意思理解就是FPGA布線工具在進行布線的時候,發(fā)現(xiàn)設計的某些部分在布局后器件之間的分布過于密集,連線過于復雜,因此無法完成布線。

這跟PCB的設計有點類似,當PCB的布局不合理或者器件過多的時候,有可能在指定的面積下無法完成布線,只能通過增加PCB面積或者層數(shù)來完成。

那么對于FPGA來說到了設計能夠布局布線階段,這已經(jīng)是一個中期的階段,此時要重新選型不現(xiàn)實;另外如果FPGA本身已經(jīng)是最大規(guī)模,那么更換FPGA更是不可能。這種情況跟時序不收斂要惡劣得多。

因此,在這個時候,設計者通常面臨兩種選擇:

①刪除部分設計需求,除低設計占用的FPGA資源;

②優(yōu)化邏輯電路的實現(xiàn)架構、代碼。

對于第一種選擇,設計變更太大,造成的影響太多,而且降低FPGA資源利用率后也不能保證能夠布線成功第二種選擇是一個比較艱難的選擇,這意味著很可能要對前期已經(jīng)仿真驗證好的代碼進行大量修改和優(yōu)化,在進行布局布線測試的過程中又重新仿真驗證。

這是一個比較麻煩的過程,但是,這也印證了前期設計規(guī)劃的重要性,即要求設計者在前期就能夠預見到該設計可能遇到的問題,在做邏輯電路架構和編碼的時候注意到這種潛在的危險,爭取在概要設計和詳細設計階段就把該類風險考慮進去,編碼的時候養(yǎng)成良好的編碼風格和習慣,最大程度地減少該類事情的出現(xiàn)。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21742瀏覽量

603538 -

邏輯電路

+關注

關注

13文章

494瀏覽量

42631 -

PCB設計

+關注

關注

394文章

4689瀏覽量

85672

原文標題:FPGA布局布線失敗怎么辦(一)

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

FPGA去耦電容如何布局布線

PCB布局布線技術的發(fā)展

布局布線技術的發(fā)展

FPGA的布局布線

FPGA布局布線的可行性 FPGA布局布線失敗怎么辦

FPGA布局布線的可行性 FPGA布局布線失敗怎么辦

評論