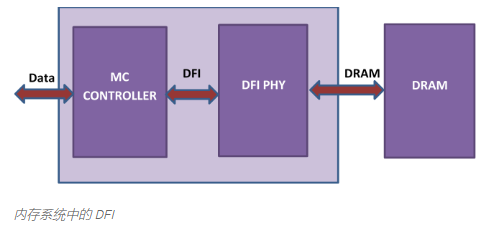

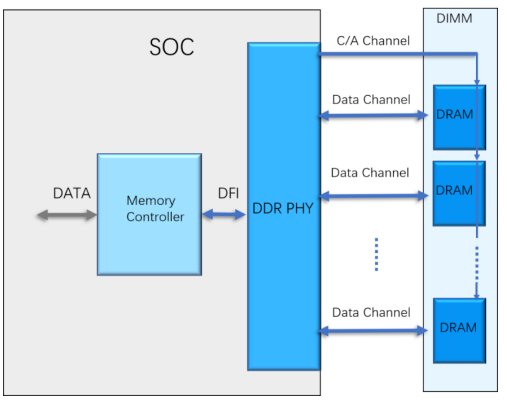

內存子系統是 SoC 中最復雜的系統之一,對芯片的整體性能至關重要。近年來,內存市場呈爆炸式增長,在移動、消費和企業系統中勢頭強勁。這不僅導致內存控制器 (MC) 越來越復雜,還導致將內存子系統連接到外部 DRAM 的 PHY變得非常復雜。

由于 SoC 和 DRAM 之間的數據高速傳輸,因此有必要對內存接口信號進行復雜的training以獲得最佳操作(更好的眼圖)。

MC 和 PHY 的集成是一個重大挑戰,特別是如果兩個IP 塊來自不同的供應商(當然即使同一家供應商也可能是獨立開發的)。關鍵原因是內存協議的快速發展,以及控制器和 PHY 之間的 DFI 接口在 MC-PHY training的要求方面沒有完全指定,或者在某些情況下是模棱兩可的。

為什么 MC-PHY 集成現在不是一個大問題?

隨著 DFI MC-PHY 接口規范的推進,事情正朝著正確的方向發展。對于不熟悉 DFI 的人來說,這是一個行業標準,它定義了任何通用 MC 和 PHY 之間的接口信號和協議。自 2006 年 DFI 1.0 問世以來,該規范穩步發展,涵蓋了 MC-PHY 操作的所有方面。

但這并不是 MC-PHY 集成變得更容易的唯一原因。為了更好地理解這一點,我們需要研究 MC 和 PHY 在training過程中如何相互作用。有兩種基本方法可以trainingmemory信號:

PHY evaluation mode or DFI Training mode- 此模式可由 PHY 或MC 啟動,無論哪一方啟動training,MC 都會設置DRAMgate/read data eye/write/CA training,并定期發出read或write等training命令。PHY 負責確定每個操作正確的編程延遲,但 MC 必須啟用和禁用 DRAM 和 PHY 中的training邏輯,以及生成必要的read/write/mrr命令。因此,DFI Training mode需要MC進行足夠多的配合,并且在早期的 DFI 規范中是強制性的。然而在較新的DFI中,這種DFI Training mode已成為 MC 的可選項。

PHY independent mode– 這是一種 PHY 執行DRAM training的模式,MC 很少參與。PHY 生成所有read/write命令并編程每個操作的延遲,而 MC 耐心等待“done”狀態。

PHY IP 提供商已決定通過在其IP中實現對PHY independent mode的支持來獲得training的所有權,保留基于其PHY架構優化 PHY training算法的控制權。

隨著 PHY 復雜性和DDR速率增加的挑戰,對 PHY independent mode的支持為PHY IP提供商增加了寶貴的差異化優勢。

在PHY-independent mode中,內存控制器的作用是什么?

由于 PHY 在training期間承擔了大部分繁重的工作,因此 MC 只需要關注兩個問題:

何時發出training請求?

將控制權交給 PHY 進行training時,DRAM需要處于什么狀態,當 PHY 將控制權交還給 MC 時,DRAM將處于什么狀態?

因此,MC 將 PHY training的請求作為中斷進行處理,它需要安排一些為實現最佳內存操作所做的許多事情。?

審核編輯:黃飛

-

控制器

+關注

關注

112文章

16361瀏覽量

178071 -

內存

+關注

關注

8文章

3025瀏覽量

74056 -

內存控制器

+關注

關注

0文章

40瀏覽量

8888

原文標題:內存控制器(MC)和DDR phy的集成

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DDR內存無法正常工作怎么解決?

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

TMS320DM646x數字媒體系統DMSoC的DDR2存儲控制器詳細介紹

DDR PHY 與電路板調試

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

使用DFI的DDR-PHY互操作性

完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表

完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表

DDR phy內存控制器的作用是什么?

DDR phy內存控制器的作用是什么?

評論