Altera Interface Planner 用于探索設(shè)備的外設(shè)架構(gòu),并高效地分配接口。通過實時進行擬合和合法性檢查,防止非法引腳分配。此方法消除了復雜的錯誤消息,無需等待完整編譯過程,因此加快了 I/O 設(shè)計過程。本文將介紹 Altera Interface Planner,方便大家使用 Altera Quartus Prime Pro Edition 開發(fā)軟件,高效地設(shè)計引腳布局。

I/O 規(guī)劃中的挑戰(zhàn)

以下為 Altera Interface Planner 的目標環(huán)境:

目標 Quartus Prime:Quartus Prime 專業(yè)版

目標 FPGA:Quartus Prime 專業(yè)版支持的 FPGA 系列

在現(xiàn)代 FPGA 中創(chuàng)建 I/O 分配主要面臨的挑戰(zhàn)包括:日益復雜的 I/O 標準和 FPGA I/O 結(jié)構(gòu) (準確設(shè)計引腳布局需要更多指導步驟)、PCB 開發(fā)與 FPGA 設(shè)計同時進行 (或稍早) 和在設(shè)計周期早期驗證引腳分配。為了應對這些挑戰(zhàn),Quartus Prime 提供了 Pin Planner 和 I/O Assignment Analysis 解決方案。

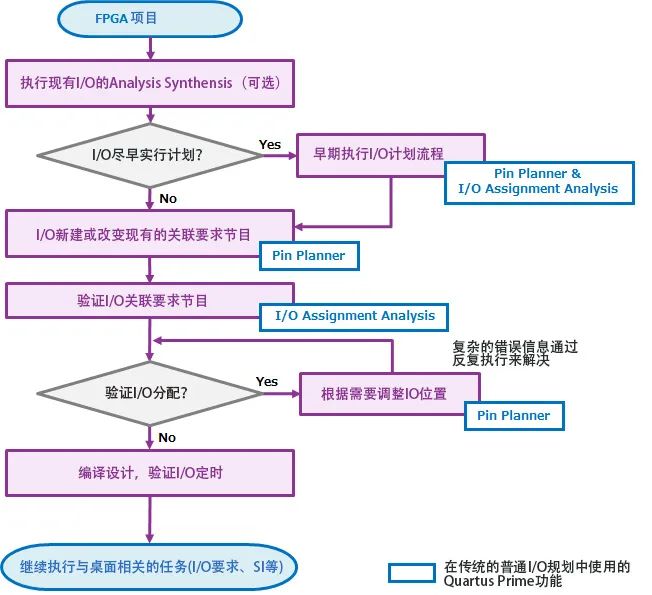

接下來創(chuàng)建 I/O 布局規(guī)劃,在下圖 (圖1) 所示的工作流程中,將分別使用 Pin Planner 和 I/O Assignment Analysis。此流程使用 I/O Assignment Analysis 來分析引腳分配,I/O Assignment Analysis 的準確性取決于設(shè)計的完整性。如果檢測到任何錯誤,需要在 Pin Planner 或其他工具中修復它們,并再次運行 I/O Assignment Analysis。如此循環(huán)往復,直到完成并驗證所有 I/O 分配。

Altera 目前支持市場所需的多種協(xié)議,它還支持許多儲存器接口,每個接口都有自己的放置規(guī)則。設(shè)計包含的接口越多,規(guī)則和限制就越復雜。即使工程師認為自己已經(jīng)正確地放置了一個設(shè)計接口,但只有在完全編譯期間運行 Fitter 或 I/O 分配分析時,才能知道它是否真的正確。如果一個元素因被放置在無效位置而導致不符合要求,則完全編譯所花費的時間就會被浪費。

圖1 傳統(tǒng) I/O 規(guī)劃流程

I/O 布局規(guī)劃工作流程

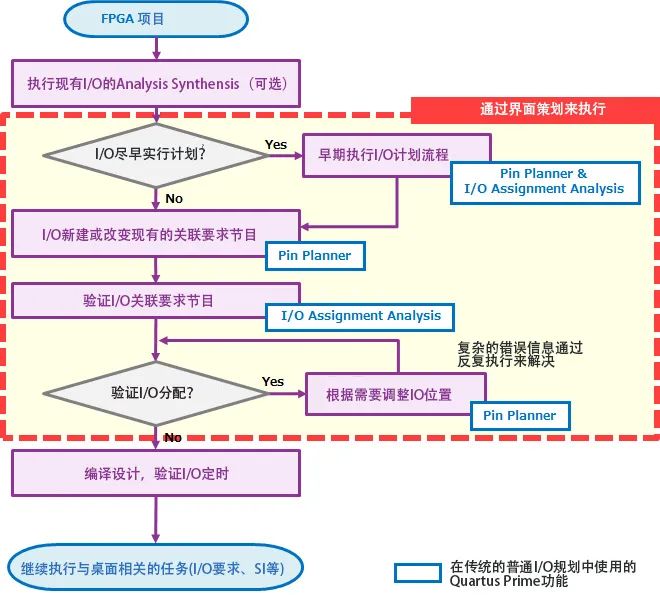

Quartus Prime Pro Edition Interface Planner 是一款引腳布局工具,可根據(jù)引腳布局規(guī)則以圖形方式創(chuàng)建和實時驗證復雜的 I/O 接口分配。下圖 (圖2) 顯示了使用 Interface Planner 時的 I/O 布局規(guī)劃工作流程。

圖2 使用 Interface Planner 的 I/O 規(guī)劃流程

Interface Planner 使用 Fitter 實時驗證引腳分配,因此雖然需要預先進行邏輯綜合 (Synthesis),但設(shè)計不需要完美無缺。要將界面設(shè)計分配給設(shè)備的資源,只需拖放或雙擊平面圖即可。創(chuàng)建的分配計劃將以 TCL 腳本的形式生成并執(zhí)行,并在反映項目后進行編譯。

I/O 布局規(guī)劃工作詳細步驟

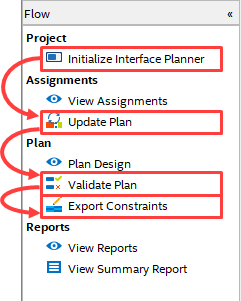

接下來將介紹 Interface Planner 的工作流程詳細步驟,如下圖 (圖3) 所示。請注意,此時用戶應已完成引腳分配。

圖3 Interface Planner 工作流程

一、綜合設(shè)計

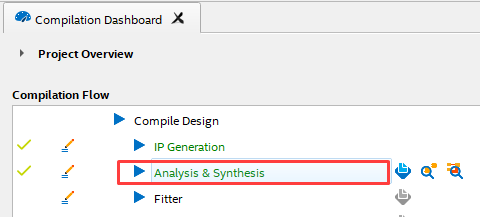

在 Quartus Prime Pro Edition (以下簡稱 Quartus Prime) 中,從 Processing 菜單或 Compilation Dashboard 運行 Analysis & Synthesis,如下圖 (圖4) 所示:

圖4 運行分析與綜合

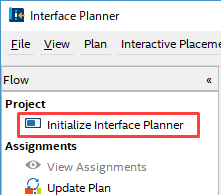

二、啟動并初始化 Interface Planner

點擊 Tools 菜單,啟動 Interface Planner。單擊下圖 (圖5) 所示 Flow 窗格中的 Initialize Interface Planner 以檢查 Fitter 基礎(chǔ)和現(xiàn)有位置分配的有效性。如果存在沖突或違規(guī),錯誤消息將顯示在控制臺窗格中。

圖5 Initialize Interface Planner

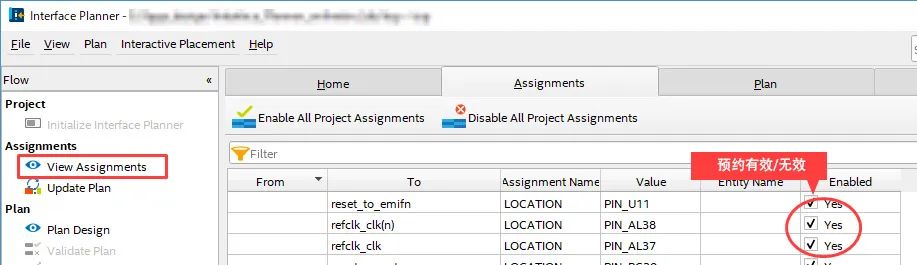

三、檢查導入的任務并更新計劃

單擊 Flow 窗格中的 View Assignments。Assignments 選項卡將變?yōu)榛顒訝顟B(tài)并列出項目中存在的所有分配,如下圖 (圖6) 所示。接下來單擊 Flow 窗格中的 Update Plan,已啟用配置的分配將應用于設(shè)計以進行規(guī)則檢查。

圖6 View Assignments

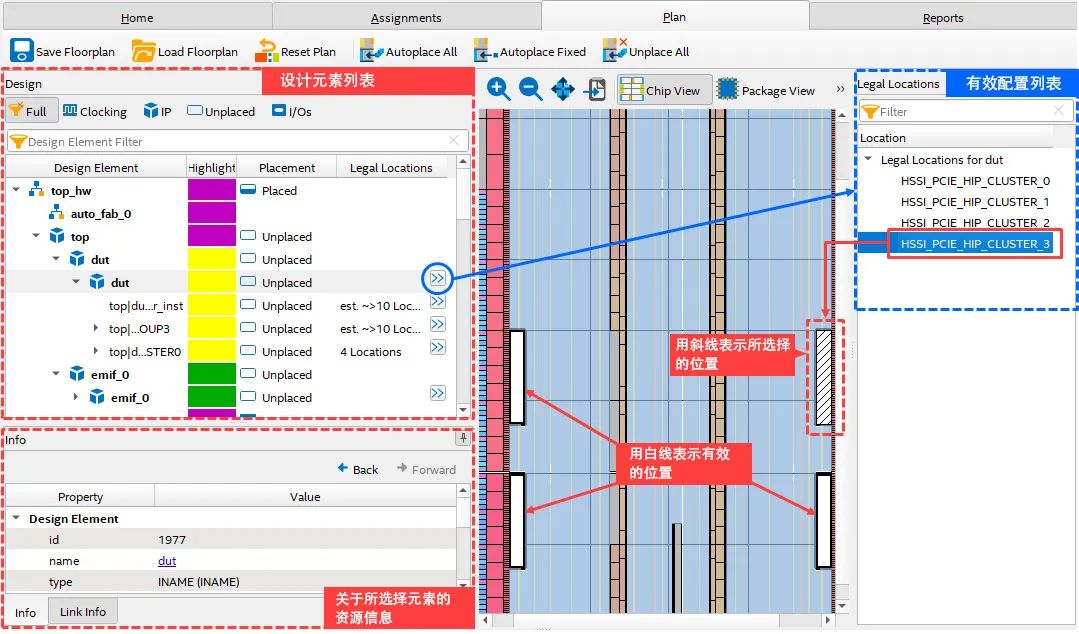

四、放置設(shè)計元素

如下圖 (圖7) 所示,單擊 Flow 窗格中的 Plan Design (Plan 選項卡變?yōu)榛顒訝顟B(tài))。

圖7 Plan Design

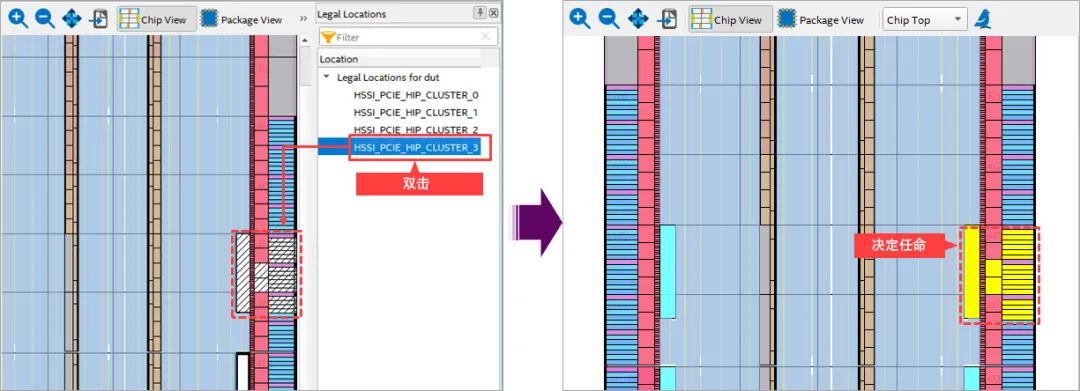

如果單擊 Design 窗格中未分配的設(shè)計元素右側(cè)的按鈕,Legal Locations 窗格中將顯示可分配位置的列表,并且該位置將在 Chip View 中以輪廓顯示。當從 Legal Locations 窗格中指定放置位置時,Chip View 顯示將變成一條對角線。要確認分配位置,請雙擊下圖 (圖8) Legal Locations 窗格中的位置信息。

圖8 確認位置 (Legal Locations 窗格)

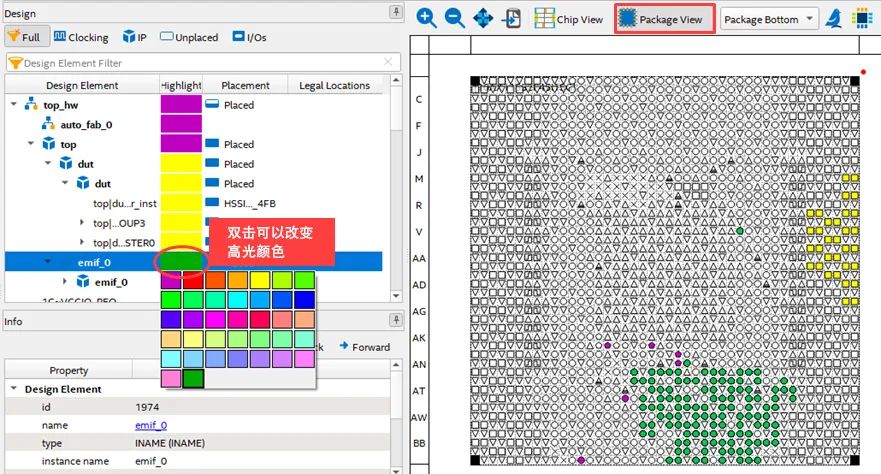

大家還可以切換到如下圖 (圖9) 所示的 Package View 以查看接口中使用的 I/O 引腳,也可以截取計劃的屏幕截圖,以便稍后將其與編譯的設(shè)計進行比較。

圖9 Package View

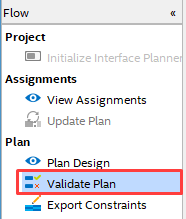

五、驗證 I/O 計劃

完成放置規(guī)范后,單擊下圖 (圖10) Flow 窗格中的 Validate Plan,這將驗證已創(chuàng)建的任務并使其準備好導出。

圖10 Validate Plan

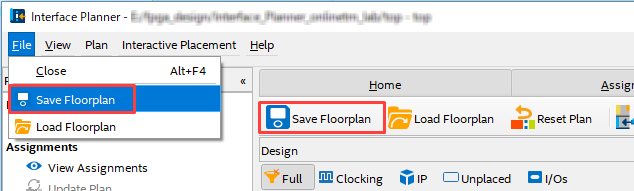

也可以通過選擇下圖 (圖11) 中的 Save Floorplan 來保存當前的布局設(shè)置:

圖11 Save Floorplan

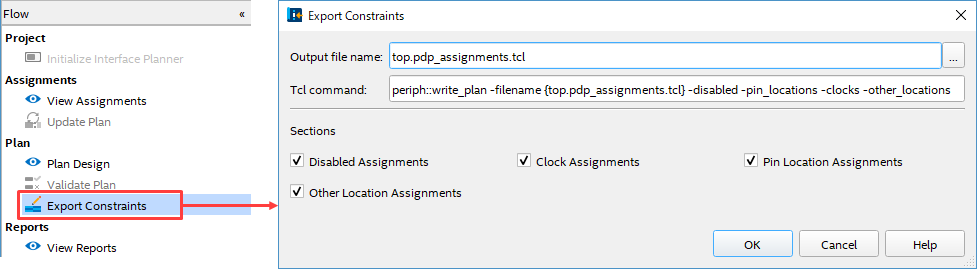

六、導出計劃文件

如下圖 (圖12) 所示,單擊 Flow 窗格中的 Export Constraints 并使用 tcl 腳本保存配置的放置信息:

圖12 Export Constraints

七、導入工程并編譯

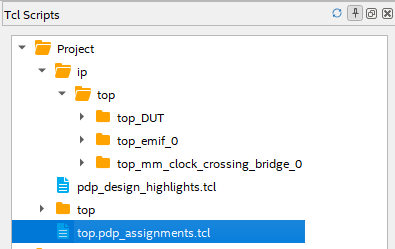

關(guān)閉 Interface Planner 并打開要導入的 Quartus Prime 項目。從 Tools 菜單 > Tcl Script,如下圖 (圖13) 所示,指定導出的 tcl 文件,然后單擊 Run 以應用它。分配信息反映在 Pin Planner 和 Assignment Editor 中,可以輕松查看和最終檢查腳本信息。在運行腳本之前可以使用 Edit 按鈕對其進行編輯。例如 Interface Planner 不會在設(shè)計中導出所有的分配類型,如果只想進行引腳分配而不是內(nèi)部資源分配,則可以通過注釋或刪除它們,從而僅提供腳本的引腳分配部分。

圖13 Tcl Script

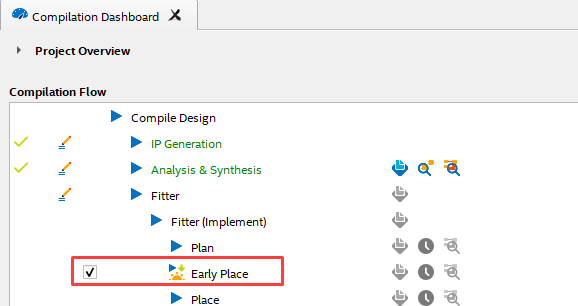

接下來運行編譯。由于 Analysis & Synthesis 階段到 Fitter (Finalize) 階段需要很長時間才能運行,如果只想評估布局,可以在下圖 (圖14) 的 Compile Dashboard 中啟用 Early Place 選項并執(zhí)行 Early Place 編譯。

圖14 Early Place

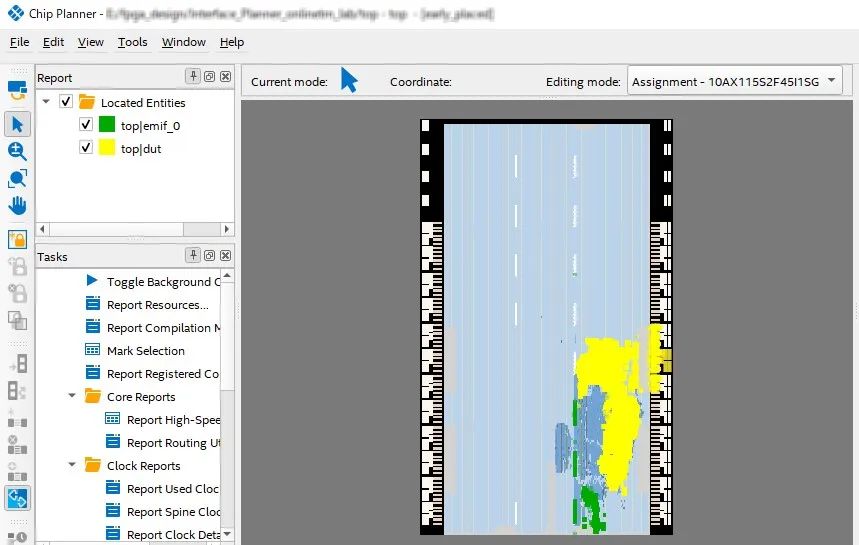

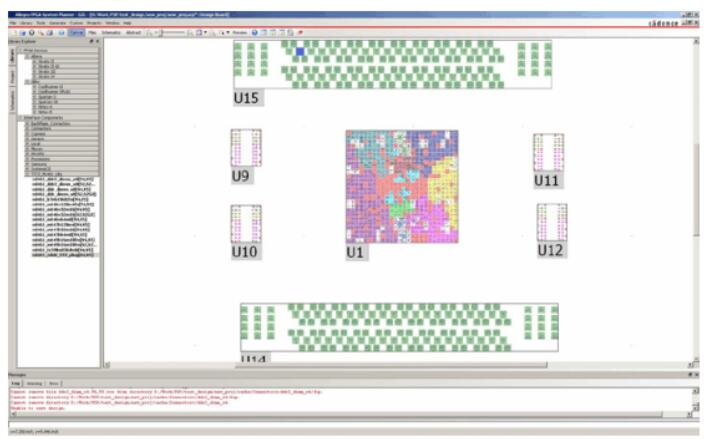

編譯完成后,啟動 Chip Planner (Tools 菜單) 并檢查布局,如下圖 (圖15) 所示:

圖15 啟動 Chip Planner

總結(jié)

Quartus Prime Pro Edition 的 Interface Planner 消除了為 FPGA 創(chuàng)建專業(yè)規(guī)劃的工作量和難度,特別是日益多樣化和復雜 I/O 接口,它可允許僅創(chuàng)建有效的位置分配。通過使用 Altera Interface Planner,可以減少進行位置分配所花費的時間。

審核編輯:劉清

-

pcb

+關(guān)注

關(guān)注

4338文章

23284瀏覽量

403153 -

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

26834 -

Altera

+關(guān)注

關(guān)注

37文章

794瀏覽量

154742 -

TCL

+關(guān)注

關(guān)注

11文章

1772瀏覽量

89260

原文標題:如何使用Altera Interface Planner高效設(shè)計FPGA引腳布局

文章出處:【微信號:駿龍電子,微信公眾號:駿龍電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

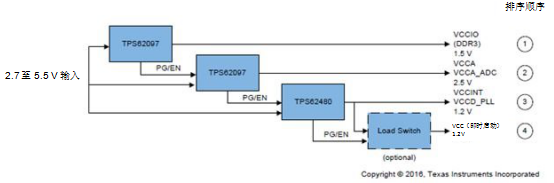

適用于Altera?MAX?10 FPGA的小型高效電源

關(guān)于FPGA system Planner軟件的問題

例說FPGA連載32:PLL例化配置與LED之使用Pin Planner進行引腳分配

在quartus 15.0中如何將PPF文件導入到Pin Planner中

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載49:PWM蜂鳴器驅(qū)動之引腳分配

Altera FPGA/CPLD設(shè)計(高級篇)

altera fpga/cpld設(shè)計

Altera新Cyclone IV FPGA拓展了Cyclo

Altera FPGA的選型及開發(fā)

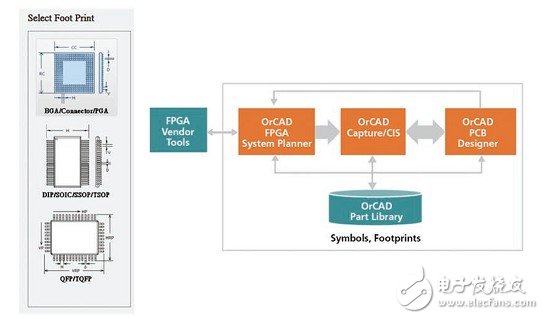

Allegro FPGA System Planner中文介紹

Cadence OrCAD FPGA System Planner為在PCB板的FPGA設(shè)計提供支持

在PCB上設(shè)計大容量引腳FPGA

Altera FPGA CPLD學習筆記

評論