隨著芯片特征尺寸的不斷減小,傳統(tǒng)的平面MOSFET由于短溝道效應(yīng)的限制,難以繼續(xù)按摩爾定律縮小尺寸。因此,引入了FinFET,有效地解決了這個問題。FinFET成為 14 nm、10 nm 和 7 nm 工藝節(jié)點的主流的柵極設(shè)計。

? ? ?

? ? ?

短溝道效應(yīng)

在MOSFET中,當溝道長度縮短到接近晶體管源極和漏極之間距離時,會出現(xiàn)閾值電壓降低,溝道長度變化,熱載流子效應(yīng)等不利情況。在22nm以下短溝道效應(yīng)更加嚴重,因此傳統(tǒng)的MOSFET已無法勝任需求。

FinFET是什么

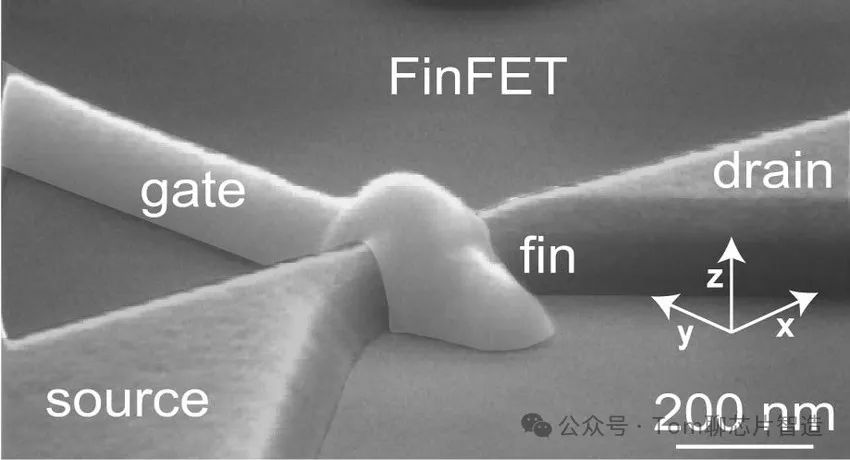

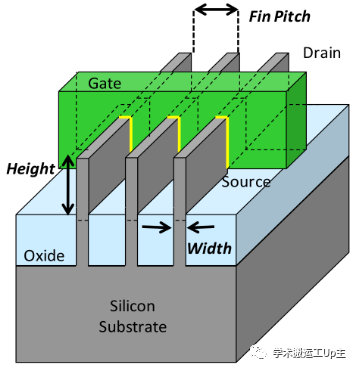

FinFET(Fin Field-Effect Transistor,鰭式場效應(yīng)晶體管),是MOSFET設(shè)計的一次重大進步。其柵極放置在溝道的兩側(cè)、三側(cè)、四側(cè)或纏繞在溝道上,形成雙柵甚至多柵結(jié)構(gòu)。如下圖:  ?

?

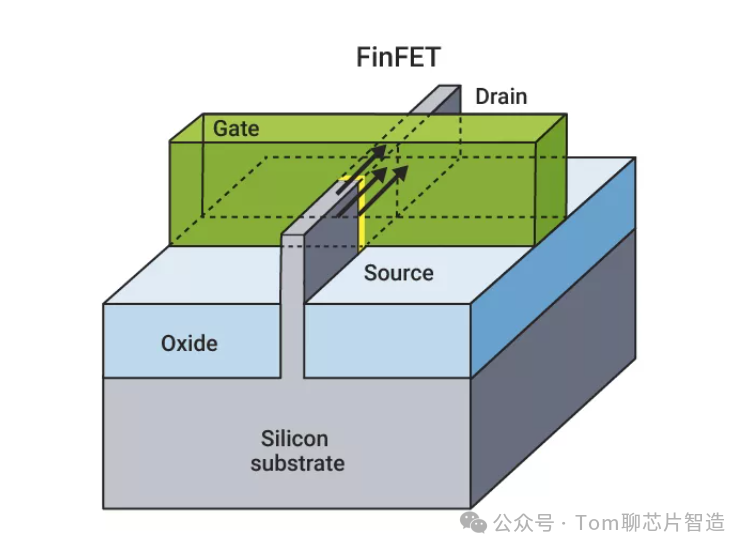

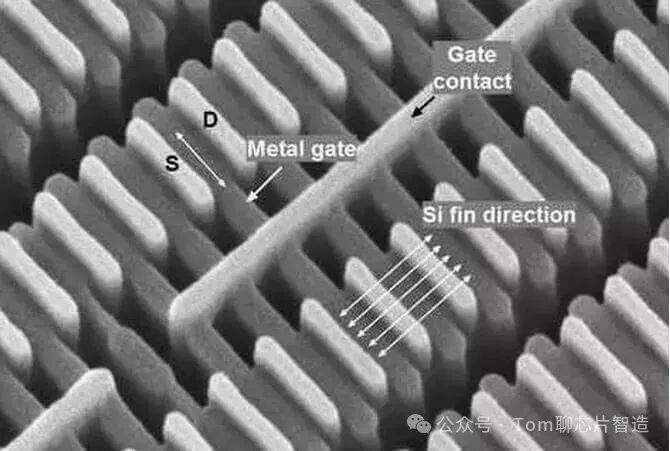

其中,鰭(Fin)位于硅基底上方的細長豎直結(jié)構(gòu)。這個鰭形成了晶體管的溝道區(qū)域,電流會在這個區(qū)域流動。而鰭的高縱橫比增加了柵極控制溝道的表面積,可以更精確地控制電流。

源極(Source)和漏極(Drain):圖中標出的源極和漏極分別位于鰭的兩端。源極與漏極是晶體管的主要電極,其中源極是電流的入口,漏極是電流的出口。

柵極(Gate):覆蓋在鰭的側(cè)面和頂部的是柵極材料,柵極可以通過電壓來控制溝道中的電流。

氧化層(Oxide):柵極與鰭之間的氧化層起到絕緣的作用,防止電流直接從柵極流入溝道。在傳統(tǒng)的MOSFET中,這一層通常是二氧化硅(SiO2),而在FinFET設(shè)計中,這一層可以是高介電常數(shù)材料,以提高柵極電容,同時降低柵漏電流。

硅基底(Silicon Substrate):整個FinFET結(jié)構(gòu)構(gòu)建在硅基底之上。

?

?

傳統(tǒng)MOSFET是平面工藝,而FinFET 是3D工藝,相對于傳統(tǒng)MOSFET來說,其柵極從三個面控制溝道,這使它在柵極和溝道之間形成的表面積更大,可以更精確更緊密地控制電流并減少泄漏,并具有更快的開關(guān)速度。

審核編輯:劉清

-

MOSFET

+關(guān)注

關(guān)注

147文章

7164瀏覽量

213287 -

摩爾定律

+關(guān)注

關(guān)注

4文章

634瀏覽量

79029 -

晶體管

+關(guān)注

關(guān)注

77文章

9693瀏覽量

138189 -

漏電流

+關(guān)注

關(guān)注

0文章

262瀏覽量

17024 -

FinFET

+關(guān)注

關(guān)注

12文章

248瀏覽量

90230

原文標題:22nm以下制程為什么要引入FinFET?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

聯(lián)電宣布22nm技術(shù)就緒

22nm平面工藝流程介紹

22nm技術(shù)節(jié)點的FinFET制造工藝流程

[轉(zhuǎn)]臺積電借16nm FinFET Plus及InFO WLP 通吃英特爾蘋果

FinFET(鰭型MOSFET)簡介

請問FinFET在系統(tǒng)級意味著什么?

FD-SOI元件與FinFET接近實用化的不斷發(fā)布

什么是FinFET?FinFET的工作原理是什么?

FinFET是什么?22nm以下制程為什么要引入FinFET呢?

FinFET是什么?22nm以下制程為什么要引入FinFET呢?

評論