ARM Cortex-M0+是2012年3月14日ARM公司發布的一款低功耗效率、能效最高的ARM處理器,可用于存在設計約束的嵌入式應用。它具有最小的硅面積和極少的代碼量,從而使開發人員能夠以16和8位的價位實現32位性能。處理器的低門數使其能夠部署在需要簡單功能的應用中。

作為ARM Cortex-M處理器系列的最新成員,32位Cortex-M0+處理器采用了低成本90納米低功耗(LP)工藝,耗電量僅9μA/MHz,約為主流8位或16位處理器的1/3,卻能提供更高的性能。這類低功耗和高性能的結合為仍在使用8位或16位架構的用戶提供了一個轉型開發32位器件的理想機會,從而在不犧牲功耗和面積的情況下,提高日常設備的智能化程度。該款經過優化的Cortex-M0+處理器可針對家用電器、白色商品、醫療監控、電子測量、照明設備以及功耗與汽車控制器件等各種廣泛應用的智能傳感器與智能控制系統,提供超低功耗、低成本微控制器(MCU)。

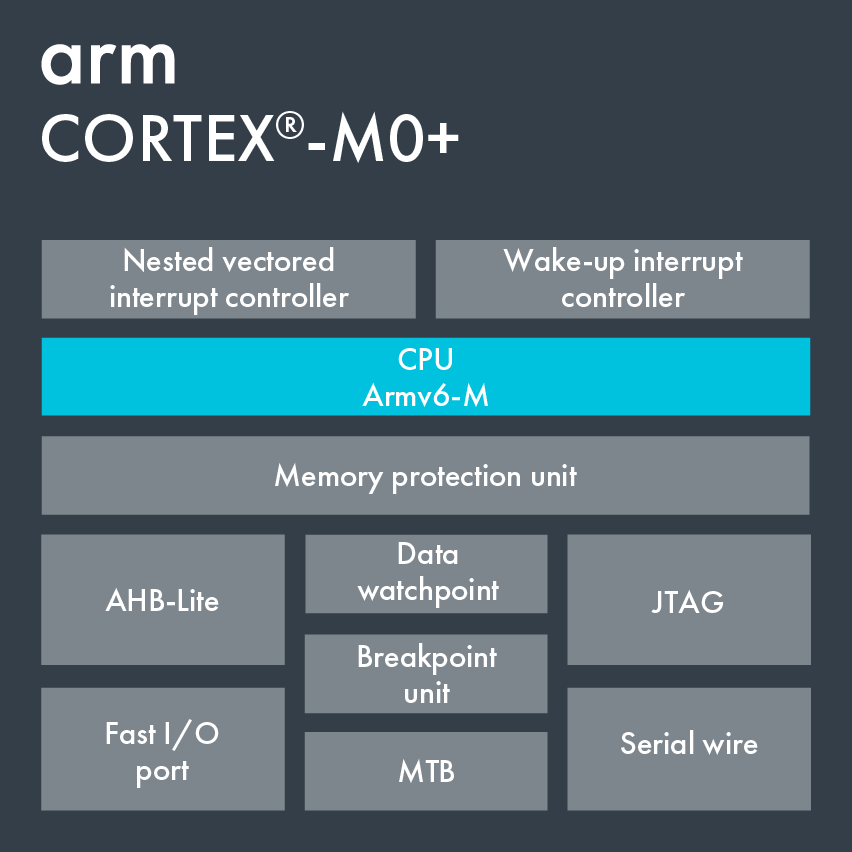

Cortex-M0+集成了存儲器保護單元(MPU)、單周期I/O接口和微跟蹤緩存(MTB)。ARM Cortex-M0+框圖如圖1-1所示。

圖1-1 ARM Cortex-M0+框圖

ARM Cortex-M0+內核具有以下關鍵特征。

·ARMv6-M架構。

·AHB-lite總線接口,馮·諾依曼總線架構,帶可選單周期I/O接口。

·Thumb/Thumb-2子集指令支持。

·2段流水線。

·可選8區域MPU,帶子區域和背景區域。

·不可屏蔽中斷+1到32個物理中斷。

·喚醒中斷控制器。

·硬件單周期(32×32)乘法。

·多種休眠模式,帶集成式等待中斷(WFI)、等待事件(WFE)以及退出時睡眠功能、睡眠和深度睡眠信號。

·根據實現方式提供多種保留模式。

·JTAG和串行線調試端口,具有多達4個斷點和2個觀察點。

·可選微跟蹤緩存。

ARM Cortex-M0+ MCU的關鍵優勢如下。

·小尺寸內核使其能夠用作小設備中的單核心,或在需要特定硬件隔離或任務劃分時,用作額外的嵌入式配套內核。

·Cortex-M0+內核不會影響基于I/O、模擬和非易失性存儲器的典型MCU的各元件之間的取舍。因此在劃分MCU產品組合時,總線大小(8、16或32位)不再相關。

·M0+微控制器在入門級應用中廣泛使用,并帶來了巨大優勢。它們滿足計算性能要求,其基本架構允許M0+ MCU在開關門數量最少的應用中達到超低功耗性能。Cortex-M0內核可減少噪聲發射,并滿足使用最佳時鐘速度的性能要求。

·內核的動態功率為5到50μW/MHz,取決于所采用的技術。但是,內核并不能代表設備的整體功耗,并且不是要考慮的唯一因素。

·Thumb指令集是Cortex-M系列的子集。它可以重復使用任何經驗證的Cortex-M產品軟件塊,以此來簡化產品組合的可擴展性。

·存儲器保護單元(MPU)管理CPU對存儲器的訪問,確保任務不會意外破壞其他激活任務所使用的存儲器或資源。MPU通常由RTOS控制。若程序訪問的存儲器位置被MPU禁止,則RTOS可檢測到它并采取行動。內核可基于執行的進程,動態更新MPU區的設置。MPU為可選,并可以進行旁路。

-

內核

+關注

關注

3文章

1377瀏覽量

40338 -

Cortex

+關注

關注

2文章

202瀏覽量

46530

發布評論請先 登錄

相關推薦

實際項目開發中為何選擇ARM? Cortex?-M4 內核的HK32MCU?

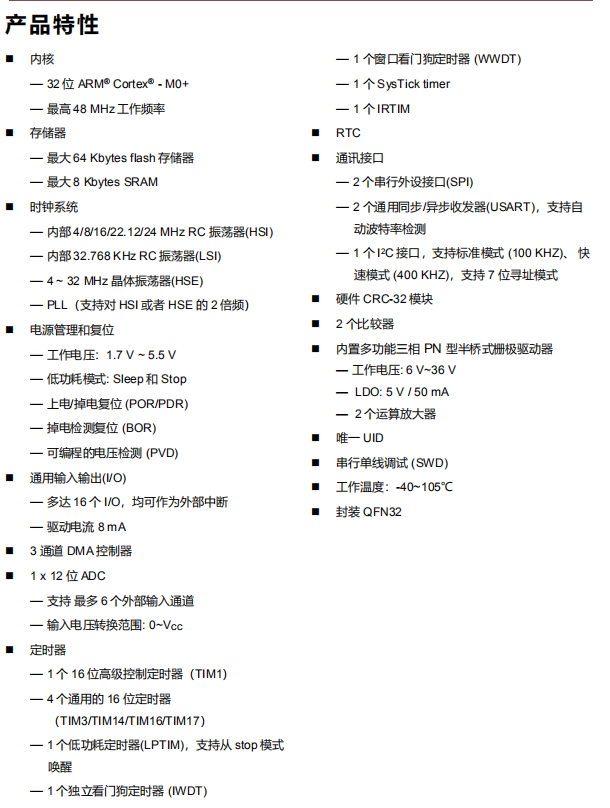

PY32C613單片機 QFN20封裝 32位M0+內核 一元不到 超高性價比

基于 ARM Cortex M0+內核BAT32A237芯片

電機專用32位MCU PY32MD310,Arm? Cortex-M0+內核

XL32F003單片機 M0+內核 主頻48M,64 K flash加8K SRAM存儲器

賽元微新推出了大資源高工規的32位M0+內核MCU—SC32F12系列

中微半導推出基于Arm Cortex-M0的CMS32M67電機控制系列微控制器

兆易創新推出GD32F5系列Cortex-M33內核MCU

Cortex-M85內核單片機如何快速上手

Cortex-M0+內核介紹

Cortex-M0+內核介紹

評論