3 月 28 日-29 日,2024 國際集成電路展覽會暨研討會(IIC Shanghai)在上海成功舉行。此次盛會匯聚了集成電路產業的眾多領軍人物,共同探尋和把握集成電路產業的發展脈絡。

在 29 日舉行的 2024 中國 IC 領袖峰會上,Cadence 數字產品資深高級總監劉淼發表了題為《當汽車電子遇見 3D-IC》的精彩演講;而在同期舉行的主題技術論壇上,Cadence 資深技術支持總監王輝、Cadence 資深產品技術銷售經理萬理也分別發表了題為《Cadence Optimity——利用 AI 應對系統級分析挑戰》和《Cadence AI——芯片級到系統級的全棧式智能 EDA 解決方案》的精彩演講。

當汽車電子遇見 3D-IC

在 2024 中國 IC 領袖峰會上,劉淼闡述了汽車電子與 3D-IC 結合的未來趨勢,深入剖析了當前電子世界的主要驅動力,并分享了 Cadence 的創新解決方案。他表示:“創新是我們的基因,我們 30% 的投資用于研發,這也支撐了 Cadence 在過去三年推出了 20 個重量級的新產品。”

劉淼認為,在技術驅動因素對多個行業的影響下,半導體行業正經歷前所未有的快速增長。盡管 2023 年全球半導體市場有所下滑,但隨后強勁復蘇,預計在今年將有超過 10% 的增長率。其中,汽車電子技術的進步將對行業的發展起到重要推動作用。

1

Cadence 的策略是確保客戶成功

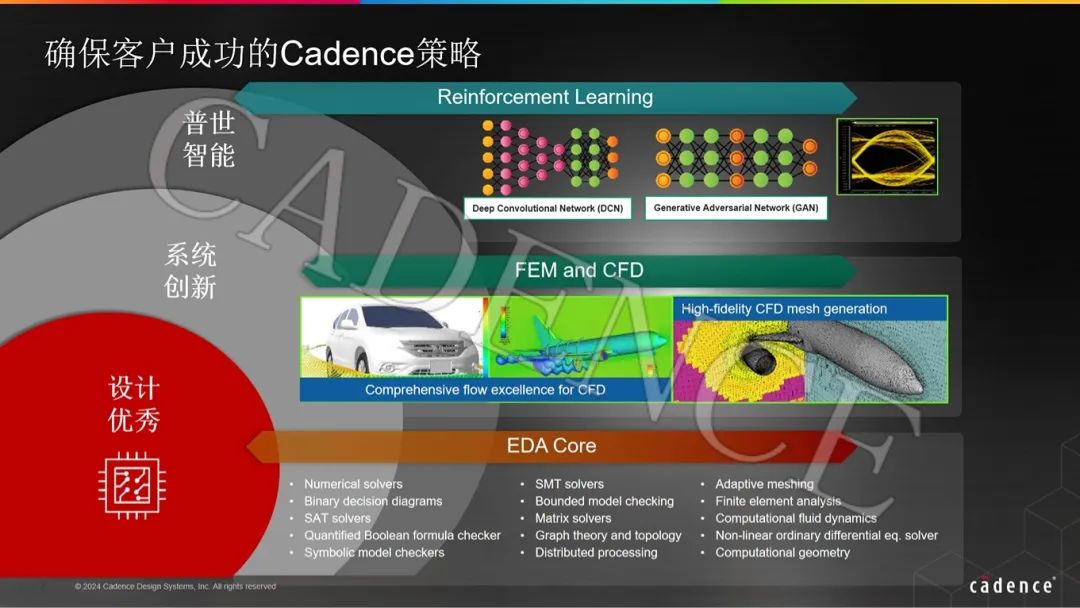

在介紹 Cadence 策略時,劉淼強調了三個同心圓概念:硅圈、系統圈和數據圈。三個圈相互關聯,緊密結合,共同推動芯片、系統和數據的發展。

例如自動駕駛,既依賴導航和場景等海量數據,還需要高效安全的系統,包含硬件、軟件和復雜的芯片,而硬件由越來越多、越來越復雜的芯片組成。

35 年來,Cadence 在 EDA 領域的優勢主要體現在計算軟件——計算機科學加數學,包括實現計算的硬件。無論是硅 EDA 和 IP、大數據系統設計和分析,還是人工智能(AI),Cadence 都展現了強大實力。

他指出,如今人工智能已成為一種新的流行,而作為矩陣乘法的神經網絡推理,利用反向傳播訓練神經網絡能實現非線性共軛梯度優化,如 Cadence 的 Innovus。Cadence 的豐富經驗不僅可用于硅,還可以用于所有系統和 AI,甚至是將 EDA 計算軟件用于生物模擬。

2

汽車電子挑戰和 Cadence 設計流程

劉淼表示,電動汽車已經成為中國出口最強勁的引擎,而汽車電子是電動汽車最重要的組成部分之一,為了滿足電動汽車越來越高的要求,汽車電子也不得不面對越來越復雜的挑戰。這些挑戰來源于安全、可靠和質量三個方面的要求,例如,更先進的工藝節點,更多的安全島機制,更及時的通訊速度,更長的使用壽命,和更大規模的數據計算。

作為汽車電子數字解決方案驅動者,Cadence 與車規芯片廠商、新勢力塑造者、創新創業者合作,為他們提供服務、軟件、硬件和 IP。

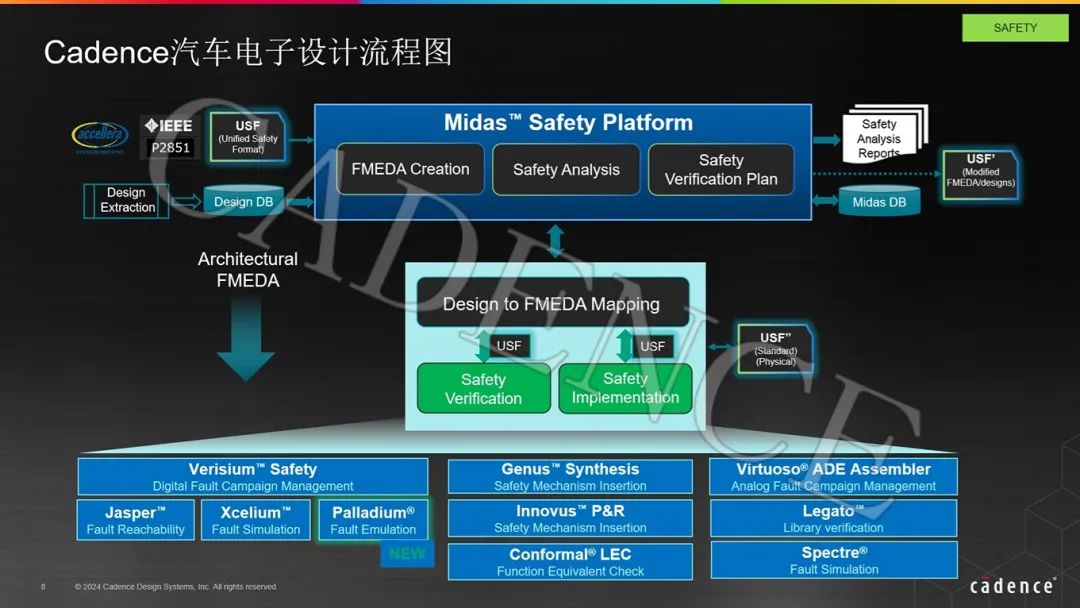

Cadence 的安全意圖格式 USF(統一安全格式)是一種與功能安全數據互操作性框架 IEEE P2815 保持一致的格式。USF 貫穿不同設計階段和產品,確保在整個設計流程中體現安全意圖。從預先編寫的 USF 文件或 Mida 的 FMEDA 分析開始,能夠將 USF 結果交付給相應的驗證、實施、混合信號/模擬設計流程,還可以在不同設計團隊間輕松交換。

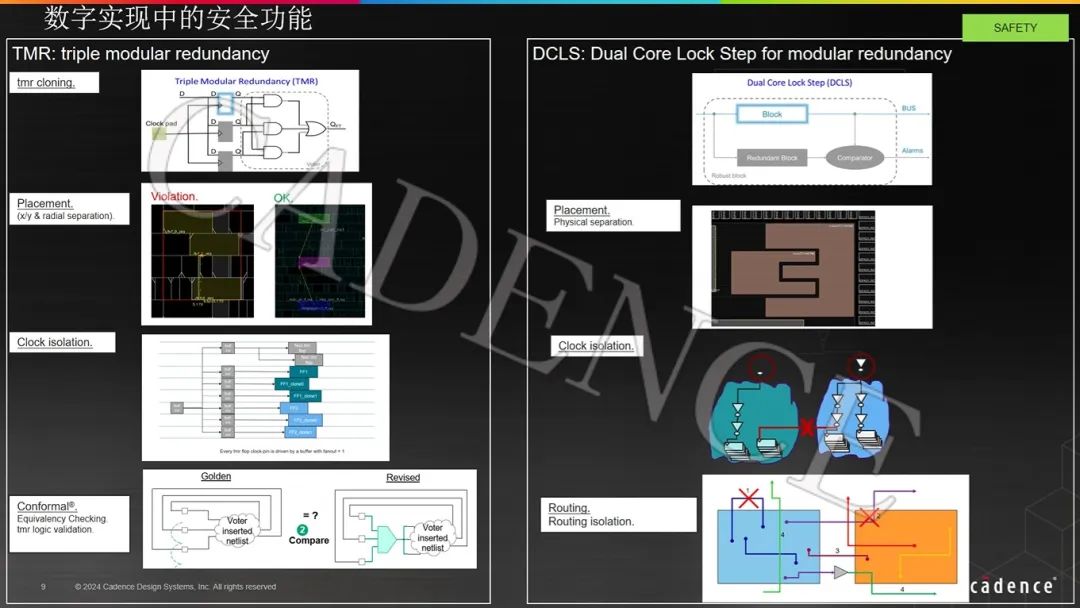

劉淼也做了小小的技術普及,比如數字實現中的安全功能的兩個基本應用:TMR 和 DCLS。TMR 通過克隆原始觸發器為具有投票邏輯的三元組提供投票機制,以檢測和糾正可能的邏輯值錯誤,增強系統容錯能力并提高可靠性。DCLS 則通過雙時鐘鎖定步進方式確保模塊級冗余設計,進一步提高系統可靠性。Cadence 完整的 USF 物理實現流程有助于實現車規數字設計。

劉淼還介紹了由中國研發團隊實現的任意邊界的 DCLS 布局與隔離和檢查,這一全新的技術,不光服務了中國的客戶,還支撐了 Cadence 在歐洲和北美的車規芯片客戶。

Cadnece 在 2023 年推出的最新的帶著機器學習加持的 Voltus Insight 電源完整性分析方案。這個全新的分析方案可以和實現工具 Innovus 完美地結合起來,讓用戶基本無感的,在實現過程中修復絕大部分的壓降違例,從而極大提高汽車電子的可靠性,減少 ECO 時間,降低設計成本。

3

后摩爾和超越摩爾時代的 3D-IC

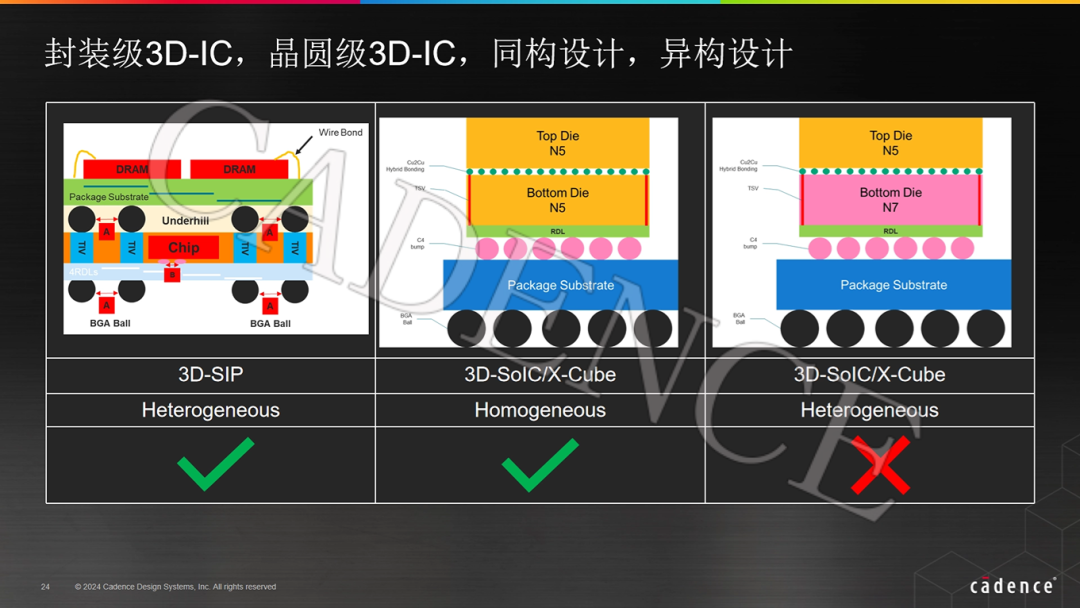

劉淼還從封裝級 3D-IC 和晶圓級 3D-IC、同構設計與異構設計、3D-IC 路線圖和挑戰、鍵合密度、2.5D 到 3D 等角度強調了后摩爾時代 3D-IC 的重要性。他指出,隨著摩爾定律逐漸失效,晶圓級 3D-IC已成為行業的焦點。Cadence既支持封裝級、晶圓級 3D-IC,也支持同構和異構設計。從 2.5D 到 3D,其銅-銅鍵合密度提升了 1000 倍,而傳輸距離卻降低了接近 50 倍,這一先進性,將極大地豐富系統公司從系統方面提升芯片性能的手段。

所以,Cadence 在晶圓級 3D-IC 上取得了長足進展,推出了基于 3D 混合布局的邏輯流內存、適用于同質和非同質芯片組的強大的 3D Mixed Placer。為應對 2.5D 到 3D-IC 的挑戰,Cadence 推出了業界首個集成的高容量統一的 Integrity 3D-IC 平臺,可在單個統一駕駛艙中進行 3D 設計規劃、實施和系統分析。

劉淼最后表示,Cadence 的智能系統設計戰略是以計算軟件為核心開發的 AI 和算法解決方案,正在擴展到新的系統域。Cadence 還致力于在核心 EDA 和關鍵 IP 上執行這一戰略,并支持云端廣泛應用,以實現普適性和可擴展性。

利用 AI 應對系統級分析挑戰

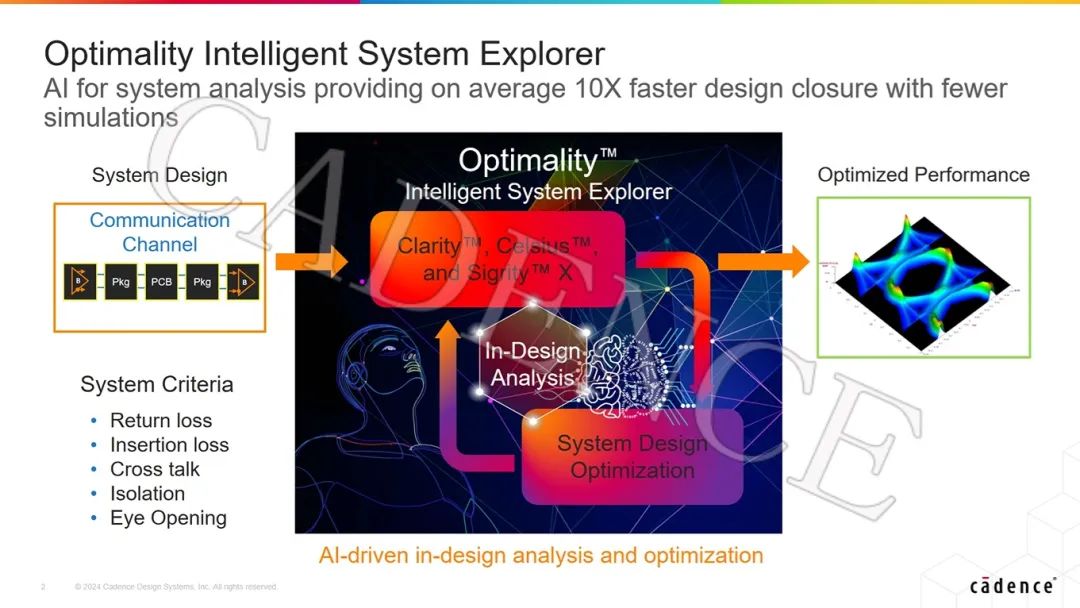

在 Chiplet 與先進封裝技術研討會上,Cadence 資深技術支持總監王輝分享了如何利用 AI 技術應對系統級分析挑戰,介紹了 Cadence 的 OptimalityExplorer智能系統優化助力系統設計突破與創新的能力。

1

應對不斷增加的復雜性和規模挑戰

王輝指出,隨著系統設計復雜性和規模不斷增加,傳統設計優化方法已難以滿足需求,需要用AI技術來應對挑戰。OptimalityExplorer 能加速實現最佳系統級設計性能,為設計師提供強大支持,實現平均 10 倍的設計收斂速度。

他解釋道,作為智能系統資源管理器,OptimalityExplorer 不僅具備快速確定最佳電氣性能的能力,還能探索完整設計空間,避免次優局部極小值和極大值,將生產力平均提高 10 倍以上。

OptimalityExplorer 可擴展解決方案采用AI驅動的多物理優化技術,涵蓋模擬、優化和簽核等多個方面;突破性算法 Cadence Cerebrus 系統級探索涵蓋芯片、封裝、板和外殼,能夠更全面考慮系統設計的各個方面,實現更優異的性能。

2

AI 新技術為實際設計賦能

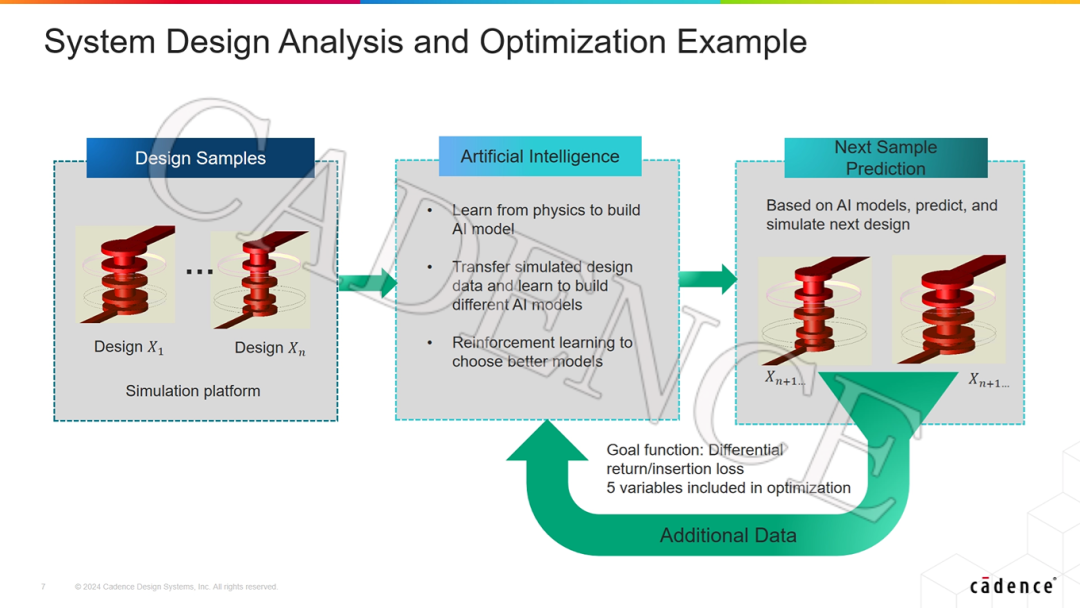

談到 AI 新技術,王輝強調了Optimality Explorer的強化學習優化能力。與傳統設計優化方法相比,它利用強化學習技術預測下一個樣本,能更高效地找到最優解。這種“現在到未來”的方案可以使設計師更快獲得滿意的設計結果。

OptimalityExplorer 采用突破性的機器學習(ML)算法,以實現最小采樣、強化學習技術、全局最優解決方案和首過成功。在提高設計生產力方面,吞吐量提高了 100 倍,實現了大規模并行化和線性可擴展性,且支持云就緒。其應用可擴展到電路圖、3D 工作臺、3D 布局等多物理場,適用于所有設計階段。

3

實例展現 OptimalityExplorer 強大能力

王輝通過實例展示了 OptimalityExplorer 在實際設計中的應用。從 AI 算法啟動設計樣本,利用模擬引擎進行分析;由 ML 模型基于初始數據點制定回歸模型,優化設計參數并啟動新案例。新模擬結果進一步完善了 ML 模型,提高了決策質量,效率提升了 10 倍,接近或優于人類驅動流程。

目前,OptimalityExplorer 已成功應用于多個系統設計分析與優化實例,如 112Gbps PAM4 通道優化、高維天線優化、三頻微帶天線參數優化、FPC 差分對參數優化以及 SI/PI 和 RF/天線應用優化,均提升了迭代收斂速度,并顯著提高了性能。

王輝表示,多位行業專家已對 Cadence 的 Optimality Explorer 贊賞有加,認為 Optimality Explorer 和 Clarity3D Solver 等工具幫助他們更快地找到最佳參數配置,加速了產品上市。

他最后表示,通過使用 OptimalityExplorer 等先進工具,設計師能夠更好地應對系統級分析挑戰,推動系統設計的不斷創新與進步。

芯片級到系統級全棧式智能 EDA 解決方案

在 EDA 與 IC 設計論壇上,萬理分享了芯片級到系統級全棧式智能 EDA 解決方案以及如何通過 AI 驅動的優化,實現系統設計的革命性突破。

1

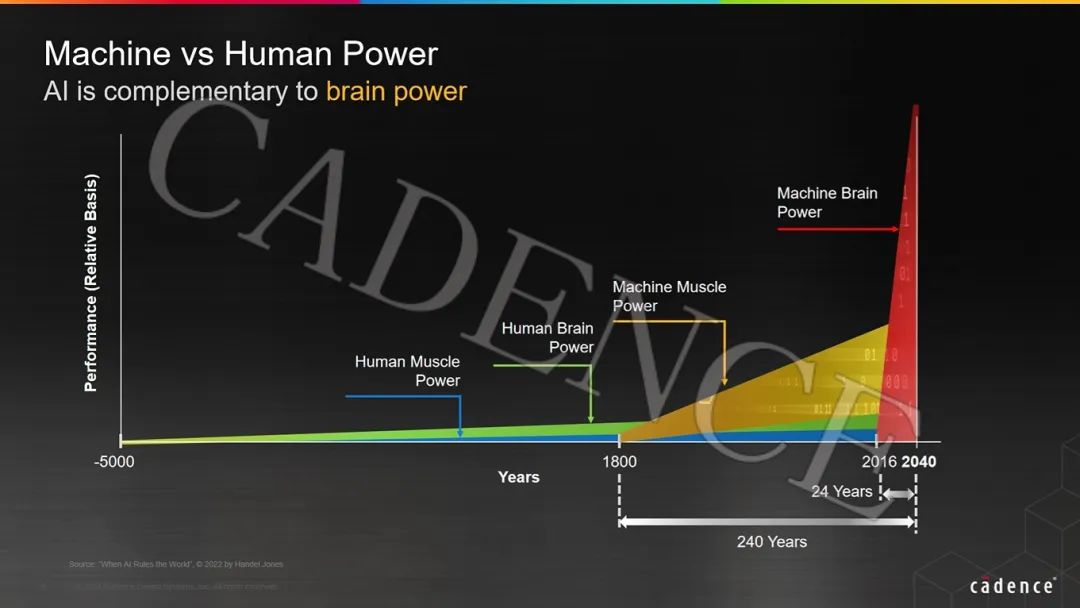

人工智能正在改變設計面貌

萬理表示,智能系統時代面臨更多挑戰,工藝演進使芯片復雜度不斷增加,傳統設計理念和方法已無法有效應對。利用 AI 驅動的優化能夠實現強化學習、卷積神經網絡、大型語言模型等;模擬與分析能夠涵蓋邏輯、電路、SI/PI、CFD、Bio 等多個應用,而計算硬件則適用于 CPU、GPU、FPGA、定制等多種類型設計。

他指出,AI 不僅是人力的補充,從手動電路設計到今天的自動化 RTL 設計重用,每次突破效率都提升了 10 倍;2030 年將再提升 10 倍以上。

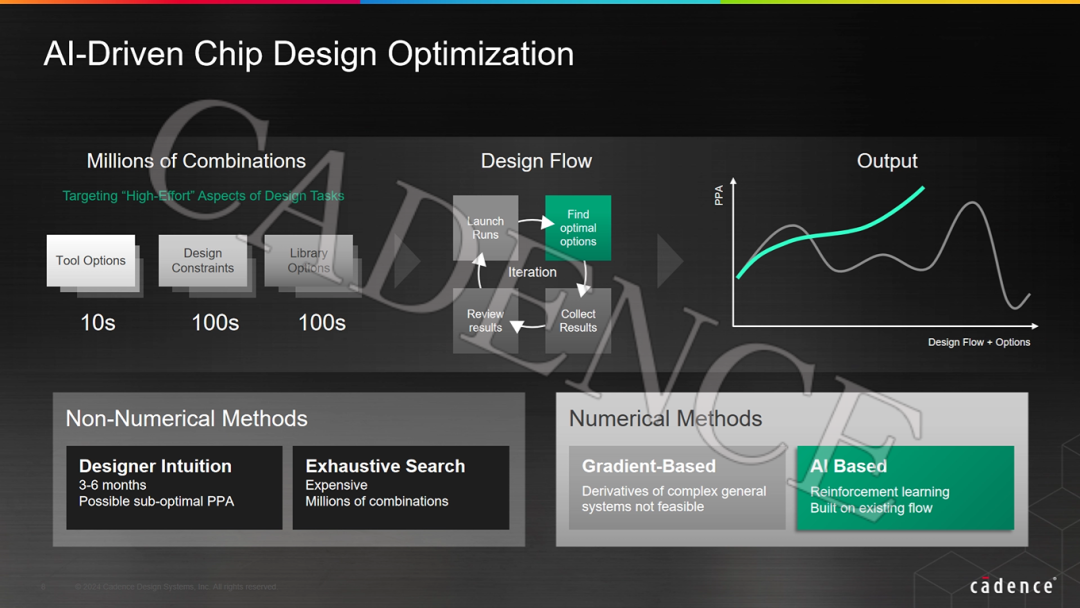

他解釋說,手動芯片設計優化要從數以百萬計的組合中輸出,憑借非數值方法和設計師直覺需要 3-6 個月才能達到次優 PPA。AI 可以實現基于現有流程的強化學習,提高電子產品的生產力和質量,并不斷改進結果,縮短獲得成果的時間。

2

Cadence AI 解決方案為系統設計賦能

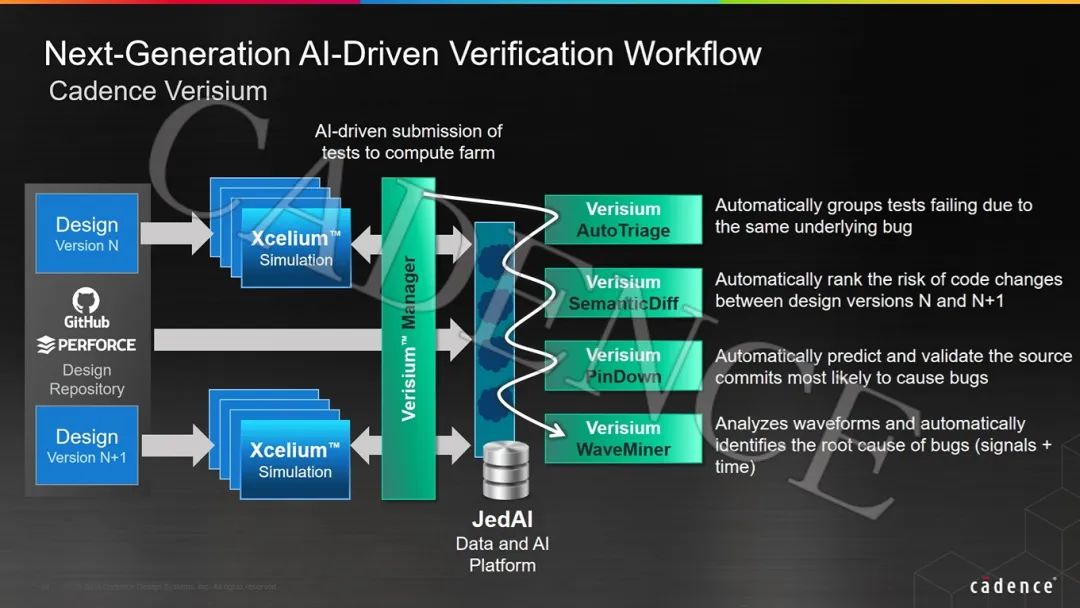

Cadence 率先推出了業界首個芯片級到系統級全棧式AI解決方案 Cadence.AI,包括 Cadence Joint Enterprise Data 和 AI(JedAI)Platform 大數據管理、Cadence Cerebrus Intelligent Chip Explorer 數字物理實現、Virtuoso Studio 模擬開發設計、Verisium AI-Driven Verification Platform 驗證、Allegro X AI Technology 系統設計以及Optimality Intelligent System Explorer 系統優化等六大平臺。

萬理說,Cadence.AI 生成式 AI 技術、JedAI Platform 和一系列 AI 增強工具都在為系統設計提供強大支持,有助于個人和團隊實現 IP 和 SoC 創建,滿足 AI 驅動的驗證、調試、實施和 PPA 優化的生產力需求。

Cadence 的 Joint Enterprise Data 和 AI Platform 可以管理芯片設計數據模型,實現自動選型、智能芯片瀏覽和芯片設計重構。Cadence 下一代 AI 驅動的驗證工作流程 Cadence Verisium 可實現失敗測試分組等識別錯誤原因等功能。

Virtuoso Studio 可以進行 AI 驅動的自定義設計,實現電路優化和布局生成。而采用 Allegro X AI 的 AI 驅動的 PCB 設計可將數天的手動流程轉縮短到數小時,效率提高 10 倍以上。

OptimityAI 驅動的系統分析平臺可將汽車 PCB 驗證效率提高 30 倍,改善 DDR4 BGA 封裝插入損耗多達 134%,112G PAM4 SerDes 隔離性能提高 1260%;而 AI 驅動的 3D-IC 可優化 Chiplet 和封裝設計。

萬理最后總結道,Cadence.AI 以前所未有的方式定義了 EDA 2.0,引領半導體設計的未來,讓工程師專注于更具創新性的工作,極大地提升工程團隊的生產效率,讓系統設計更加高效、智能和可持續。

審核編輯:劉清

-

集成電路

+關注

關注

5388文章

11547瀏覽量

361804 -

汽車電子

+關注

關注

3026文章

7955瀏覽量

167029 -

Cadence

+關注

關注

65文章

921瀏覽量

142128 -

芯片設計

+關注

關注

15文章

1019瀏覽量

54895 -

自動駕駛

+關注

關注

784文章

13812瀏覽量

166448

原文標題:IIC Shanghai 2024 | Cadence 引領 AI 浪潮,探索芯片設計智能之路

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cadence如何應對AI芯片設計挑戰

【書籍評測活動NO.51】具身智能機器人系統 | 了解AI的下一個浪潮!

浪潮信息AI存儲性能測試的領先之道

《AI for Science:人工智能驅動科學創新》第一章人工智能驅動的科學創新學習心得

涂鴉引領云開發AI浪潮,實用給力的三大開發者工具全新發布!

中國科技企業競相加碼人工智能領域投資,引領未來科技浪潮

蘋果布局未來AI戰略,Apple Intelligence引領智能新紀元

后摩智能引領AI芯片革命,推出邊端大模型AI芯片M30

人工智能如何踏上精益轉型之路,引領未來新篇章

Meta與蘋果洽談AI整合,探索更廣泛合作前景

聚焦AI技術引領,智象未來全面賦能圖片及視頻內容生產

Cadence引領AI浪潮,探索芯片設計智能之路

Cadence引領AI浪潮,探索芯片設計智能之路

評論