一、W25N01G的常規(guī)描述

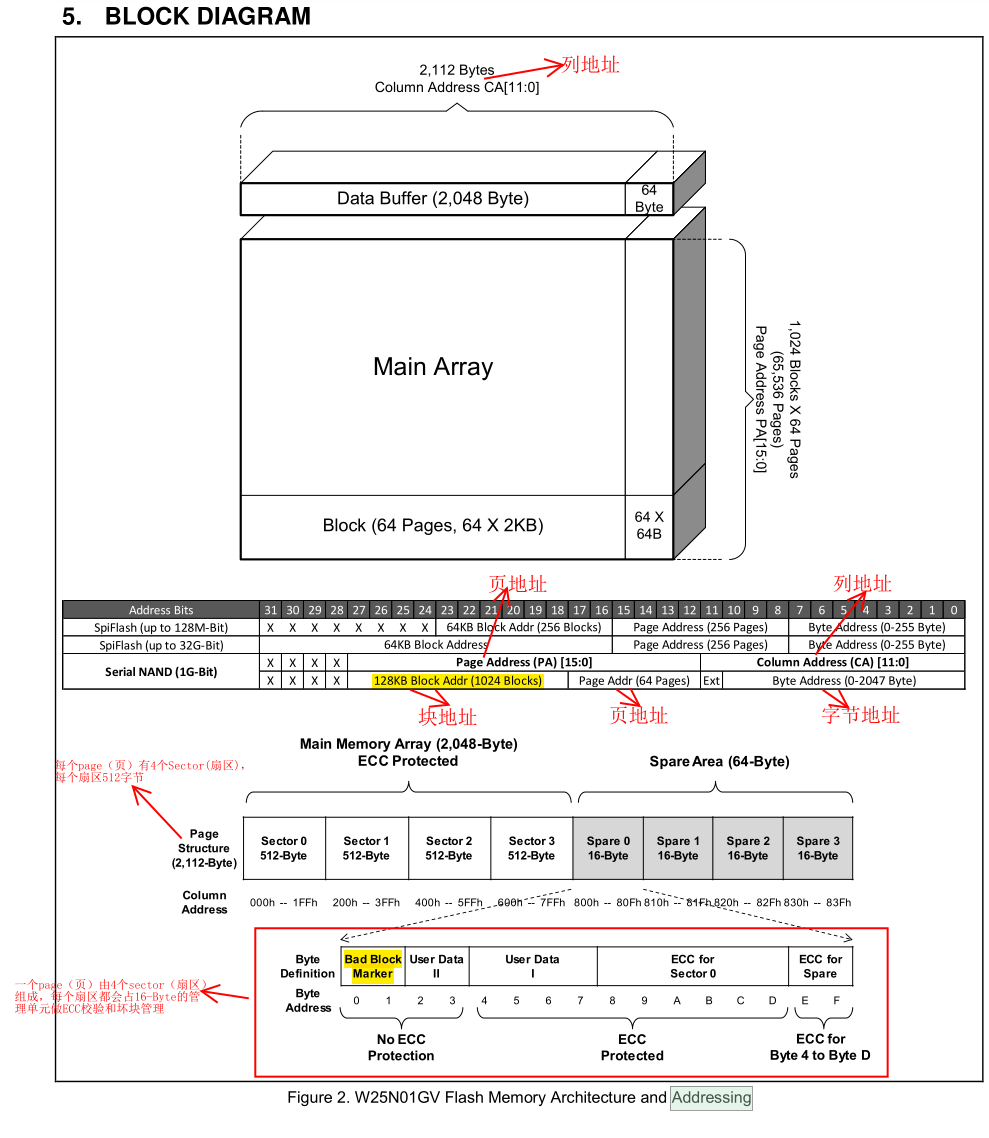

W25N01GV 有65536個page(頁),每頁有2048個字節(jié)(2KB)

可以按照64頁(64頁為1個block)進(jìn)行擦除,也就是128KB

1個block (塊) 有64個頁,每個block的大小為:64頁*2KB=128KB

W25N01GV有1024個block (塊)

W25N01GV有1G個bit,1Gbit/8=256MB

65536個page*2KB=131072KB 131,072/1024=128MB

1024個block*128KB=131072KB 131,072/1024=128MB

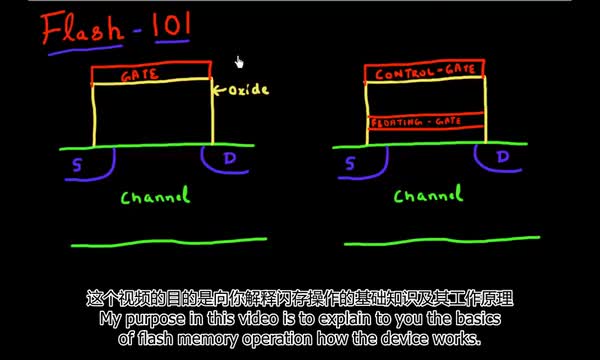

W25N01GV是SPI Nand Flash,而好多開發(fā)板上掛載的flash是nor flash,比如W25Q64、W25Q128、W25Q256等都是SPI Nor Flash

W25N01GV閃存結(jié)構(gòu)與尋址:

二、W25N10G的寫保護(hù)

使用非易失性存儲器的應(yīng)用程序必須考慮噪聲和其他可能損害數(shù)據(jù)完整性的不利系統(tǒng)條件的可能性。為了解決這個問題,W25N01GV提供了幾種保護(hù)數(shù)據(jù)免受無意寫入的方法。

當(dāng)VCC低于閾值時,設(shè)備復(fù)位

寫入啟用/禁用指令,并在擦除或程序后自動寫入禁用

使用保護(hù)寄存器(SR-1)的軟件和硬件(/WP引腳)寫保護(hù)

保護(hù)寄存器(SR-1)的寫保護(hù)鎖定,直到下次上電

使用保護(hù)寄存器(SR-1)對存儲器陣列進(jìn)行一次性程序(OTP)寫保護(hù)

當(dāng)WP-E設(shè)置為1時,使用/WP引腳進(jìn)行硬件寫保護(hù)

在上電或下電時,當(dāng)VCC低于VCC(min)時,(參見“上電-下電時間”)要求”),所有操作都被禁用,沒有指令被識別。在上電期間,后VCC電壓超過 VCC(min)且tVSL已過,所有程序和擦除相關(guān)指令進(jìn)一步禁用,延時為tPUW。這包括寫啟用,程序執(zhí)行,塊擦除和寫狀態(tài)寄存器指令。請注意,芯片選擇引腳(/CS)必須在上電時跟蹤VCC供電電平,直到達(dá)到VCC最小電平和tVSL延時,并且還必須在下電時跟蹤VCC供電電平,以防止不利的命令序列。如果需要上拉電阻上/CS可以用來完成這一點。

上電后,設(shè)備自動被置于狀態(tài)寄存器寫入禁用狀態(tài)使能閂鎖(WEL)設(shè)置為0。寫使能指令必須在程序執(zhí)行塊之前發(fā)出清除或壞塊管理指令將被接受。在完成一個程序或擦除指令后,寫使能鎖存(WEL)自動清除為0的寫禁用狀態(tài)。

軟件控制的寫保護(hù)使用寫狀態(tài)寄存器指令和設(shè)置

狀態(tài)寄存器保護(hù)(SRPO,SRP1)和塊保護(hù)(TB,BP[3:0]位。這些設(shè)置允許將一部分或整個內(nèi)存陣列配置為只讀。與寫保護(hù)(NP)引腳一起使用,可以在硬件控制下啟用或禁用對狀態(tài)寄存器的更改。看到保護(hù)注冊部分以獲取更多信息。

使用寫狀態(tài)寄存器指令,設(shè)置狀態(tài)寄存器保護(hù)(SRPO,SRP1)和塊保護(hù)(TB,BP[3:0]位,便于軟件控制的寫保護(hù)。這些設(shè)置允許將一部分或整個內(nèi)存數(shù)組配置為只讀。與Write Protect(/WP)管腳一起使用時,狀態(tài)寄存器的改變可以在硬件控制下啟用或禁用。有關(guān)更多信息,請參閱保護(hù)注冊部分。

保護(hù)寄存器(SR-1)中的WP-E位用于啟用硬件保護(hù)。當(dāng)WP-E設(shè)置為1時,將系統(tǒng)中的/WP設(shè)置為低將阻塞對W25N01GV的任何寫/程序/擦除命令設(shè)備將變?yōu)橹蛔x。當(dāng)WP-E設(shè)置為1時,Quad SPI操作也被禁用。

三、保護(hù)、配置和狀態(tài)寄存器

W25N01GV提供了三個狀態(tài)寄存器:保護(hù)寄存器(SR-1)、配置寄存器(SR-2)和狀態(tài)寄存器(SR-3)。每個寄存器分別通過讀狀態(tài)寄存器和寫狀態(tài)寄存器命令結(jié)合1字節(jié)寄存器地址進(jìn)行訪問。

讀狀態(tài)寄存器指令(05h/0Fh)可用于提供閃存陣列的可用性狀態(tài)、設(shè)備是否寫啟用或禁用、寫保護(hù)狀態(tài)、讀模式、保護(hù)寄存器/0TP區(qū)鎖狀態(tài)、擦除程序結(jié)果、ECC使用/狀態(tài)。寫狀態(tài)寄存器指令可用于配置設(shè)備寫保護(hù)特性、軟件!硬件寫保護(hù)、讀模式、啟用禁用ECC、保護(hù)寄存器/OTF區(qū)鎖。對狀態(tài)寄存器的寫訪問由非易失性狀態(tài)寄存器保護(hù)位(SRP0、SRP1)的狀態(tài)、寫使能指令控制,當(dāng)WP-e設(shè)置為1時,NP引腳控制。

01

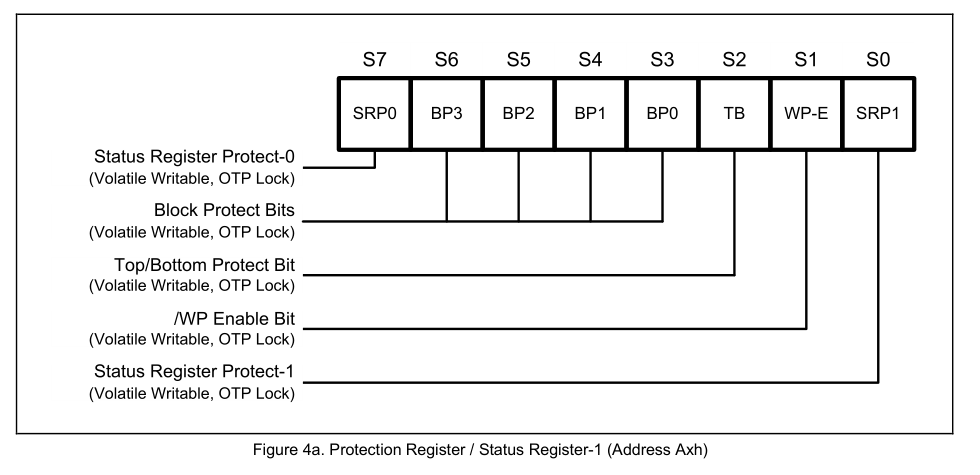

保護(hù)寄存器/狀態(tài)寄存器-1

SRP1:Status Register Protect-1 狀態(tài)保護(hù)寄存器1

WP-E:/P Enable Bit /P管腳使能

TB: Top/Bottom Protect Bit 頂層、底層保護(hù)位

BP0、BP1、BP2、BP3:Block Protect Bits 塊保護(hù)

SRP0:StatusRegisterProtect-0 狀態(tài)寄存器保護(hù)

02

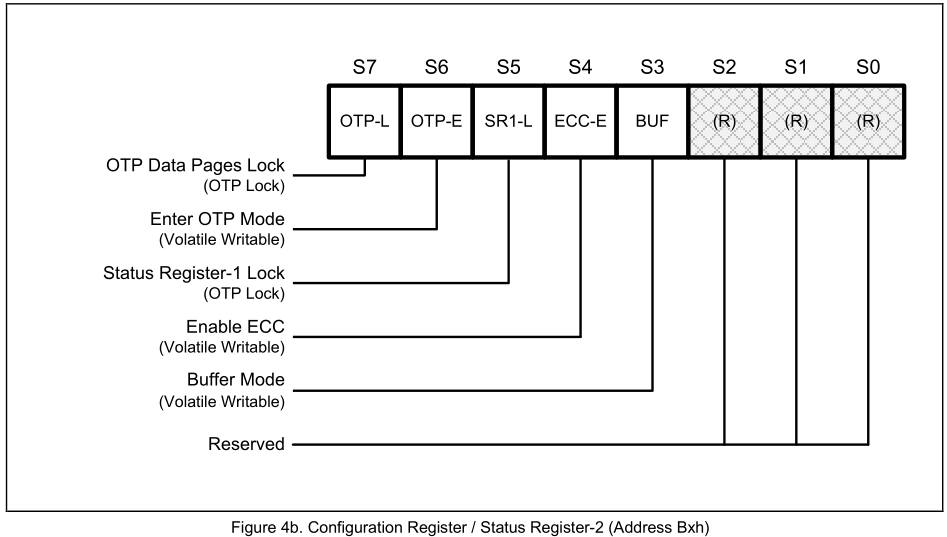

配置寄存器/狀態(tài)寄存器2

BUF:Buffer Mode 此位非常重要,牽扯到flash類型和數(shù)據(jù)讀寫方式

ECC-E: Enable ECC 使能ECC

SR1-L:Status Register-1 Lock 狀態(tài)寄存器1鎖存,也就是7.1中描述的狀態(tài)寄存器1

OTP-E:Enter OTP Mode 進(jìn)入OTP模式

OTP-L:OTP Data Pages Lock OPT數(shù)據(jù)頁鎖存

03

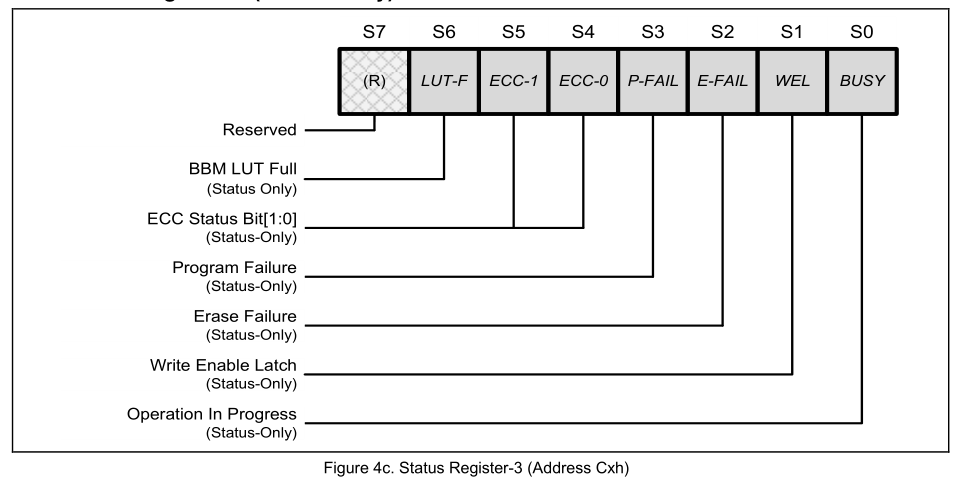

狀態(tài)寄存器-3(僅用于狀態(tài))

-

閃存

+關(guān)注

關(guān)注

16文章

1823瀏覽量

115498 -

閃存芯片

+關(guān)注

關(guān)注

1文章

128瀏覽量

19779 -

安全存儲器

+關(guān)注

關(guān)注

0文章

11瀏覽量

7519

發(fā)布評論請先 登錄

相關(guān)推薦

安全閃存鑄就高安全性智能卡

一文搞懂UPS主要內(nèi)容

一文搞懂開關(guān)電源波紋的產(chǎn)生

MCUBoot寫入閃存之前將AES密鑰存儲在哪里?

長江存儲計劃量產(chǎn)64層3D NAND閃存芯片 閃存市場將迎來一波沖擊

一文詳解閃存的限制有哪些

長江存儲64層閃存存儲密度全球第一

長江存儲將提高NAND閃存芯片的出貨量

閃存芯片分類及決定因素

強(qiáng)化閃存存儲,實現(xiàn)終極數(shù)據(jù)安全性

一文搞懂配線架相關(guān)知識

評論