本模塊實現輸入與輸出位寬相同數據加法,并對結果進行四舍五入截位,對標matlab round函數。

`timescale 1ns/1ns module data_in_width_out_width_add_round # ( parameter DATA_WIDTH = 16 ) ( // 系統接口 input i_clk_sys , input i_rst , // 數據輸入 input signed [DATA_WIDTH-1:0] i_din_a , input i_din_a_vld , input signed [DATA_WIDTH-1:0] i_din_b , input i_din_b_vld , // 數據輸出 output signed [DATA_WIDTH-1:0] o_dout , output o_dout_vld ); /****************************************************************************/ /* parameter /****************************************************************************/ /****************************************************************************/ /* signal /****************************************************************************/ logic signed [DATA_WIDTH-1+1:0] din_add_result ; logic din_add_result_vld ; logic signed [DATA_WIDTH-1+2:0] din_add_result_round ; logic signed [DATA_WIDTH-1:0] din_add_result_truncate ; logic din_add_result_vld_1dly ; logic din_add_result_vld_2dly ; /****************************************************************************/ /* process /****************************************************************************/ always @(posedge i_clk_sys or posedge i_rst) // 數據加法 begin if (i_rst) begin din_add_result <= {{DATA_WIDTH+1}{1'b0}}; end else begin din_add_result <= i_din_a + i_din_b; end end always @(posedge i_clk_sys) begin din_add_result_vld <= i_din_a_vld && i_din_b_vld; end always @(posedge i_clk_sys) // 數據四舍五入,根據要舍棄的位寬加不同的值 begin if (din_add_result[DATA_WIDTH] == 1'b0) // 每次加法先擴充一個符號位,再對小數點位置進行 加減 0.5 begin din_add_result_round <= {din_add_result[DATA_WIDTH],din_add_result + 1'b1}; end else // 4'b1000}; +4bit 1是為了modelsim仿真,modelsim仿真規定小數至少3位 begin din_add_result_round <= {din_add_result[DATA_WIDTH],din_add_result - 1'b1}; end end always @(posedge i_clk_sys or posedge i_rst) // 數據截位 begin if (i_rst) begin din_add_result_truncate <= {DATA_WIDTH{1'b0}}; end else if (din_add_result_round[DATA_WIDTH+1] == din_add_result_round[DATA_WIDTH]) begin // 如果數據沒有溢出,舍棄最后一位,賦值; 先補充符號位,再取表示起始bit為1,包含bit1并往上升DATA_WIDTH-1位 din_add_result_truncate <= {din_add_result_round[DATA_WIDTH+1],din_add_result_round[1+ :(DATA_WIDTH-1)]}; end else if (din_add_result_round[DATA_WIDTH+1] == 1'b0 && din_add_result_round[DATA_WIDTH] == 1'b1) begin // 如果正數溢出了,就給一個設置的位寬bit正數最大值,'h7fff din_add_result_truncate <= {1'b0,{(DATA_WIDTH-1){1'b1}}}; end else if (din_add_result_round[DATA_WIDTH+1] == 1'b1 && din_add_result_round[DATA_WIDTH] == 1'b0) begin // 如果負數溢出了,就給一個設置的位寬bit負數最大值,'h8000 din_add_result_truncate <= {1'b1,{(DATA_WIDTH-1){1'b0}}}; end end always @(posedge i_clk_sys) // 數據有效流水打拍 begin din_add_result_vld_1dly <= din_add_result_vld; din_add_result_vld_2dly <= din_add_result_vld_1dly; o_dout <= din_add_result_truncate; o_dout_vld <= din_add_result_vld_2dly; end endmodule

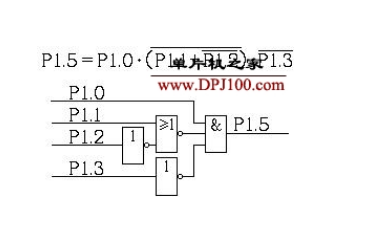

代碼中如果直接截位,數據的輸出將會產生直流,所以需要對數據的符號位進行判斷,并進行處理。簡單的思路如下:

1.數據先進行加法。

2.對加法后的結果,進行判斷,正數+0.5,負數-0.5,此操作用于去除直流。

3.再對去除直流后的結果,進行需要的截位取值,例如16bit+16bit=17bit,而最終的輸出結果,如果要16bit,那就去掉末位,也可以只要15bit,去掉末2bit,只要bit15-bit2。

上述代碼是簡單的例子處理,輸入進來的兩種數據同位寬,輸出也用同位寬輸出。后續可以改進。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21759瀏覽量

604273 -

matlab

+關注

關注

185文章

2979瀏覽量

230647

原文標題:FPGA加法截位處理

文章出處:【微信號:pdh的FPGA,微信公眾號:pdh的FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么研究浮點加法運算,對FPGA實現方法很有必要?

處理等方面受到了限制,由于FPGA中關于浮點數的運算只能自行設計,因此,研究浮點加法運算的FPGA實現方法很有必要。

發表于 07-05 06:21

如何利用FPGA實現高速流水線浮點加法器研究?

處理等方面受到了限制,為什么研究浮點加法運算的FPGA實現方法很有必要? 因為FPGA中關于浮點數的運算只能自行設計 。

發表于 08-15 08:00

32位處理器的開發與8位處理器的開發有哪些明顯的不同?

32位處理器的開發與8位處理器的開發有哪些明顯的不同?開發一個32位的嵌入式系統需要哪些工具和環境呢?32位嵌入式系統的開發過程中存在哪些技術難點?有什么方法去應對呢?

發表于 04-19 08:11

求一種在FPGA上實現單精度浮點加法運算的方法

介紹一種在FPGA上實現的單精度浮點加法運算器,運算器算法的實現考慮了FPGA器件本身的特點,算法處理流程的拆分和模塊的拆分,便于流水設計的

發表于 04-29 06:27

Intel 64位處理器,Intel 64位處理器結構原理

Intel 64位處理器,Intel 64位處理器結構原理

現在人們廣泛使用的是由32位微處理器構成的計算系統,但是32位的計算和操作系統不能支持

發表于 03-26 15:07

?3323次閱讀

FPGA信號截位策略研究

在FPGA中,隨著信號處理的層次加深,對信號進行乘、累加、濾波等運算后,可能輸入時僅為8位位寬的信號會擴展成幾十位位寬,位寬越寬,占用的硬件資源就越多,但位寬超過一定范圍后,位寬的增寬并不會對處理

發表于 11-18 12:37

?2022次閱讀

單片機位處理指令的使用方法

1.位處理指令的一般性說明

在分類時將位傳送歸入傳送指令類,條件轉移歸入程序控制類。其余位操作歸為位處理指令。

位邏輯運算以C為目標,/ b i t表示取(b i t)的非值運算,但不影響原值。

發表于 04-10 16:22

?2634次閱讀

為什么研究浮點加法運算,對FPGA實現方法很有必要?

,浮點加法器是現代信號處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。 但多數FPGA不支持浮點

FPGA加法截位處理方法介紹

FPGA加法截位處理方法介紹

評論