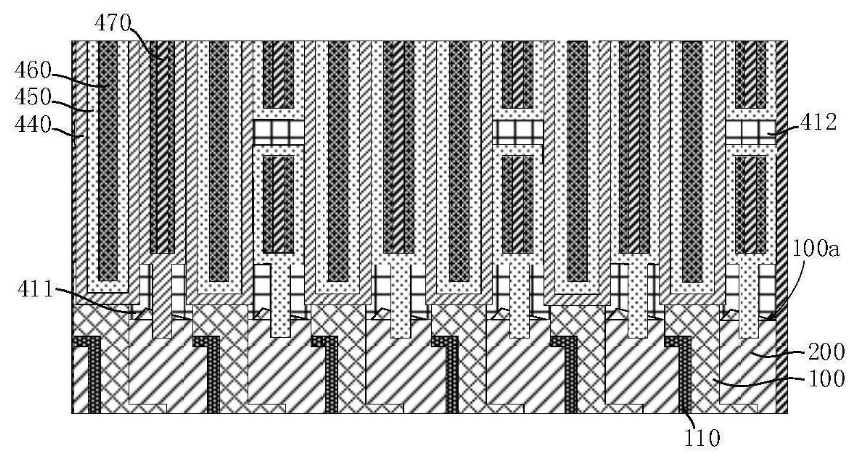

據悉,中芯國際集成電路制造(上海)有限公司近期獲得一項關于“半導體結構及其形成方法”的專利,專利號為CN111370488B,于2024年4月16日正式生效,其申請日期是2018年12月26日。

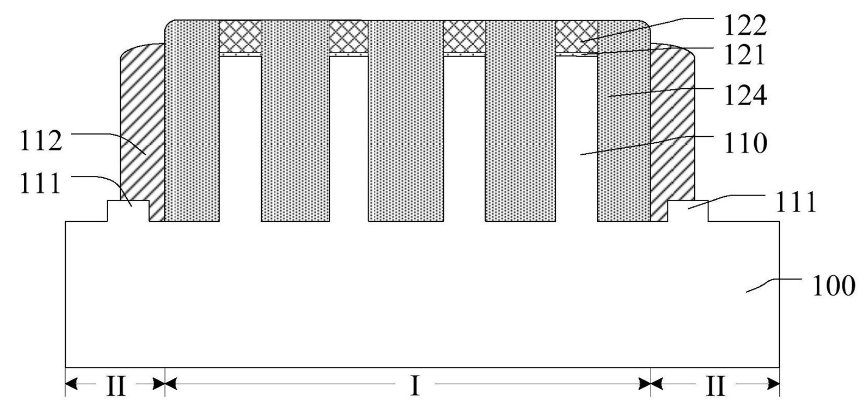

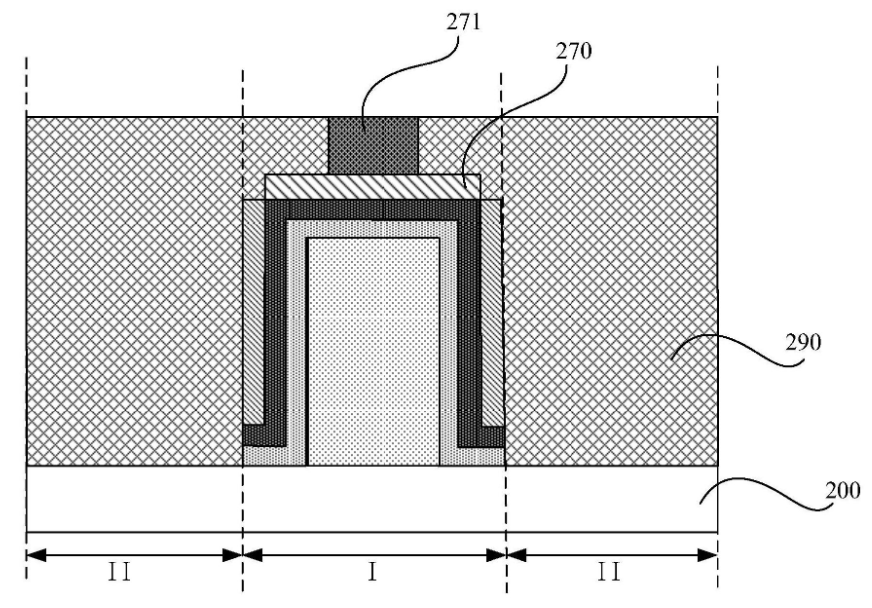

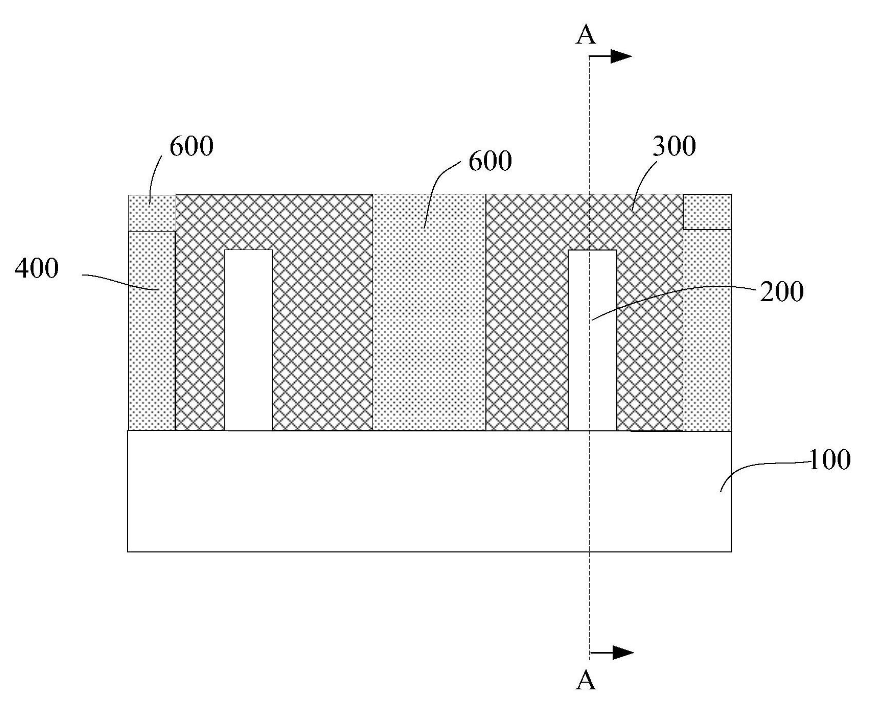

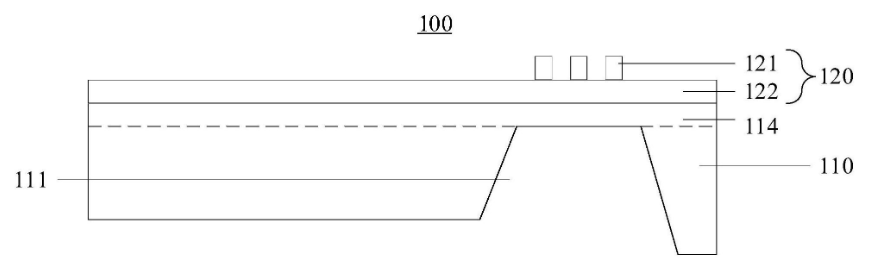

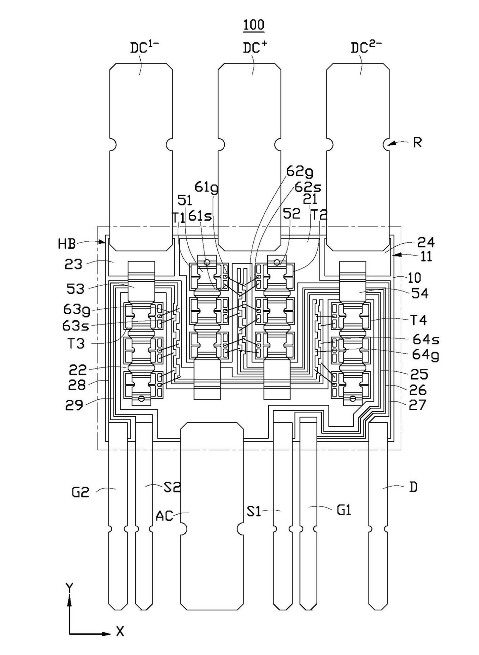

該半導體結構及其形成方法主要包含以下步驟:首先,需制備基底,其中含有器件區及位于兩側的隔離區;之后進行基底圖案化,制作出襯底及突出于襯底的鰭部;接著,在器件區兩側形成突出于隔離區襯底的第一偽鰭部;最后,在鰭部與第一偽鰭部暴露的襯底上形成隔離層,并覆蓋鰭部部分側壁。通過這種方式,第一偽鰭部的設計能提高各鰭部周邊區域的圖形密度均勻性,進而改善器件區隔離層的厚度均勻性,同時降低鰭部彎曲或傾斜的可能性,進一步提升半導體結構的電氣性能。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

集成電路

+關注

關注

5388文章

11547瀏覽量

361838 -

半導體

+關注

關注

334文章

27367瀏覽量

218775 -

中芯國際

+關注

關注

27文章

1418瀏覽量

65355

發布評論請先 登錄

相關推薦

華進半導體榮獲中國專利優秀獎

近日,國家知識產權局正式發布第二十五屆中國專利獎評選通知,華進半導體一項名為“CN202010426007.5一種晶圓級芯片結構多芯片堆疊互連結構及制備

中國半導體專利申請激增,萬年芯134項專利深耕行業

,及外界對中國微電子行業施加重大限制的背景下,半導體專利逆向增長的趨勢體現了我國科技實力的提升,其中萬年芯微電子擁有134項國內專利,成為國內半導體行業優勢企業。

p型半導體是怎么形成的

p型半導體(也稱為空穴半導體)的形成是一個涉及半導體材料摻雜和物理性質變化的過程。以下是對p型半導體形成過程的詳細解析,包括其定義、摻雜原理

AMEYA360:士蘭微“MEMS器件及其制造方法”專利獲授權

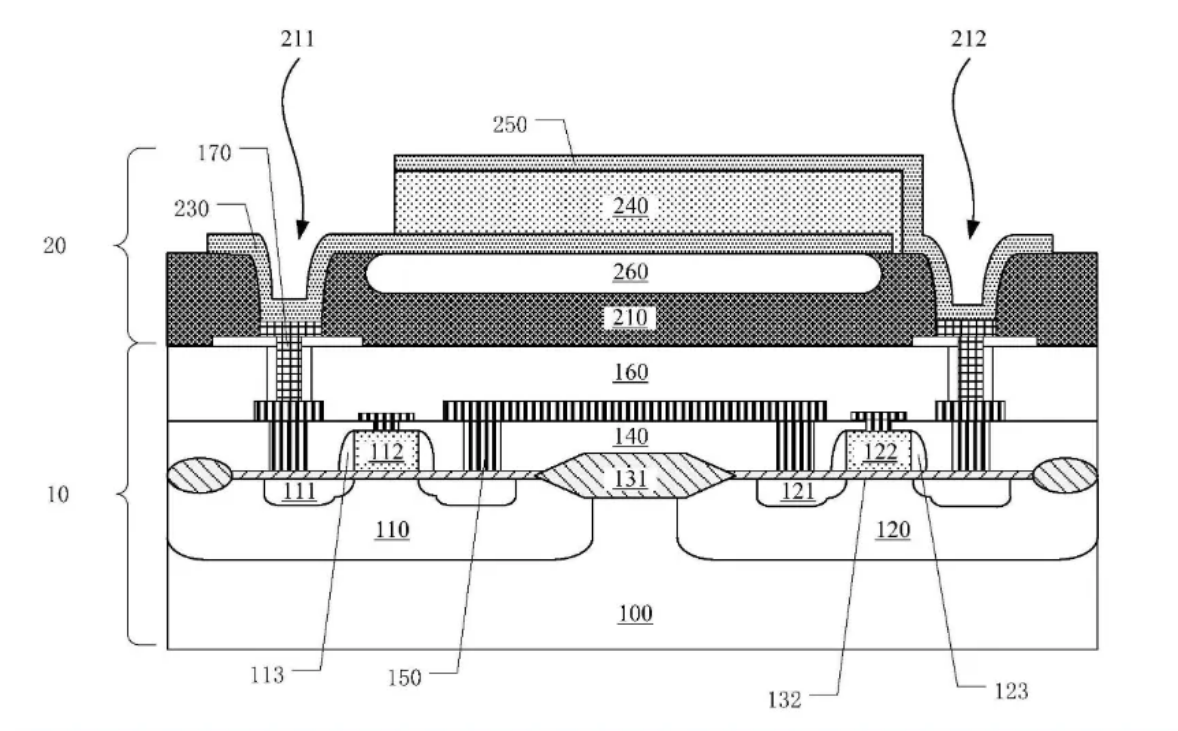

申請公開了一種MEMS器件及其制造方法。該制造方法包括:形成CMOS電路;以及在CMOS電路上形成MEMS模塊,CMOS電路與MEMS模塊連

KOWIN存儲芯璀璨亮相南京國際半導體大會

2024世界半導體大會暨南京國際半導體博覽會于6月5-7日在南京國際博覽中心4號館舉辦,現場云集300+家行業領軍企業,開展EDA/IP核產業發展高峰論壇、2024人工智能創新應用

發表于 06-12 17:14

?347次閱讀

中芯國際獲非易失性存儲裝置及其制作方法專利

該專利涉及一種新型非易失性存儲裝置及其制作工藝。具體而言,其步驟如下:首先,制備包含器件區與非器件區的基底;接著,在基底上依次沉積第一電極材料層及絕緣材料層;然后,在絕緣材料層上形成犧牲層,該層覆蓋非器件區并露出器件區;

華虹宏力半導體獲半導體器件專利

該發明涉及一種半導體器件,包含底座,又劃分為第一和第二園區,一個位于另兩個鄰側之間;兩個子漏區,坐落于底座的第一園區;虛擬結構,位于兩子漏區間的底座上;源區,位于底座的第二園區;柵極結構,位于第一和第二園區之間的底座上。

中芯國際專利獲新型半導體器件

該發明提出一種制備半導體器件的新方法,首先需要在基板上制備劃分明確且排列整齊的鰭部;之后在基板上構建覆于鰭部之上的偽柵結構;再制備并在偽柵結構上方安裝一層第一層間介電層,此層上表面比偽

半導體芯片結構分析

。它們主要包括晶體管(三極管)、存儲單元、二極管、電阻、連線、引腳等。

隨著電子產品越來越“小而精,微薄”,半導體芯片和器件尺寸也日益微小,越來越微細,因此對于分析微納芯片結構的精度要求也越來越高,在芯片

發表于 01-02 17:08

中芯國際獲“半導體結構及其形成方法”專利?

中芯國際獲“半導體結構及其形成方法”專利?

評論