編寫能夠被綜合工具識(shí)別的狀態(tài)機(jī),首先需要理解狀態(tài)機(jī)的基本概念和分類。狀態(tài)機(jī)(FSM)是表示有限個(gè)狀態(tài)以及在這些狀態(tài)之間轉(zhuǎn)換的邏輯結(jié)構(gòu)。在FPGA的設(shè)計(jì)中,狀態(tài)機(jī)的設(shè)計(jì)思想至關(guān)重要,因?yàn)樗軌蚴沟肍PGA在并行處理的基礎(chǔ)上實(shí)現(xiàn)與CPU類似的串行處理效果,同時(shí)具有高效的順序控制模型、容易利用EDA工具進(jìn)行優(yōu)化設(shè)計(jì)等特性。

首先,你需要根據(jù)設(shè)計(jì)需求選擇摩爾(Moore)型或米勒(Mealy)型狀態(tài)機(jī)。Moore型狀態(tài)機(jī)的狀態(tài)變化僅與當(dāng)前狀態(tài)有關(guān),而Mealy型狀態(tài)機(jī)的狀態(tài)變化還依賴于輸入信號(hào)。

狀態(tài)機(jī)實(shí)現(xiàn)

首先,定義一個(gè)模塊,包括時(shí)鐘、復(fù)位信號(hào)以及輸入輸出端口。并使用參數(shù)來(lái)定義狀態(tài),例如使用獨(dú)熱碼(one-hot)進(jìn)行狀態(tài)編碼。

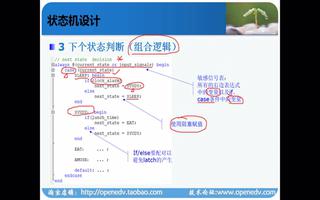

module moore_state_machine ( input wire clk, // 時(shí)鐘信號(hào) input wire rst_n, // 復(fù)位信號(hào) inputwireA_in,//輸入信號(hào) outputregB_out//輸出信號(hào) ) parameters0=4'b0000;//狀態(tài)0 parameters1=4'b0010;//狀態(tài)1 //其他狀態(tài)...然后,使用always @(posedge clk or negedge rst_n)語(yǔ)句來(lái)描述時(shí)鐘邊沿或復(fù)位邊沿觸發(fā)的狀態(tài)轉(zhuǎn)移邏輯,常包含三個(gè)部分:下一個(gè)狀態(tài)的邏輯電路、存儲(chǔ)當(dāng)前狀態(tài)的時(shí)序邏輯電路、輸出組合邏輯電路。

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= s0; // 復(fù)位到初始狀態(tài)

end else begin

????//?根據(jù)輸入和當(dāng)前狀態(tài)計(jì)算下一個(gè)狀態(tài)

case (state)

s0: begin

????????if?(A_in?==?1)?state?<=?s1;?//?當(dāng)輸入為1時(shí),轉(zhuǎn)移到s1

// 其他條件...

end

// 其他狀態(tài)轉(zhuǎn)移...

endcase

end

end

最后再根據(jù)當(dāng)前狀態(tài)計(jì)算輸出信號(hào)。

assignB_out=...;//根據(jù)state計(jì)算輸出表達(dá)式與Moore型狀態(tài)機(jī)類似,定義模塊并包含必要的輸入輸出端口,同樣使用參數(shù)定義狀態(tài)。Mealy型狀態(tài)機(jī)的輸出是在輸入信號(hào)變化后立即發(fā)生變化的。因此,需要在always @(posedge clk or negedge rst_n)語(yǔ)句中同時(shí)考慮輸入的變化,并且最后需要根據(jù)當(dāng)前狀態(tài)和輸入計(jì)算輸出信號(hào)。

另外,在實(shí)際進(jìn)行狀態(tài)機(jī)的編程過(guò)程中,需要繪制狀態(tài)轉(zhuǎn)換圖,明確每個(gè)狀態(tài)之間的轉(zhuǎn)換條件和結(jié)果狀態(tài),再根據(jù)繪制的狀態(tài)轉(zhuǎn)換圖,編寫verilog實(shí)現(xiàn)代碼。

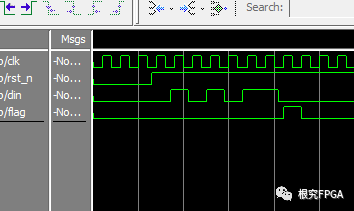

為了測(cè)試狀態(tài)機(jī)的正確性,還需要編寫相應(yīng)的testbench代碼,提供輸入信號(hào)并觀察輸出結(jié)果是否符合預(yù)期。最后在EDA工具中對(duì)代碼進(jìn)行編譯、布局布線,上板驗(yàn)證狀態(tài)機(jī)設(shè)計(jì)的正確性。

如何選擇狀態(tài)機(jī)類型

盡管這兩種類型的狀態(tài)機(jī)都廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)、雷達(dá)通信系統(tǒng)等領(lǐng)域,但它們各自的特點(diǎn)決定了它們?cè)谔囟☉?yīng)用場(chǎng)景下的適用性。因此需要根據(jù)項(xiàng)目的具體需求、對(duì)響應(yīng)速度的要求、是否需要根據(jù)輸入信號(hào)調(diào)整輸出以及對(duì)狀態(tài)數(shù)的需求等因素綜合考慮:

時(shí)序與響應(yīng)速度:Moore型狀態(tài)機(jī)的時(shí)序更好,但其響應(yīng)要慢一拍;而Mealy型狀態(tài)機(jī)的響應(yīng)最快,但在時(shí)序上要差一些。這意味著如果項(xiàng)目對(duì)電路的響應(yīng)速度有較高要求,可能會(huì)傾向于選擇Mealy型狀態(tài)機(jī)。

輸出邏輯:Moore型狀態(tài)機(jī)的輸出只與當(dāng)前狀態(tài)有關(guān),而Mealy型狀態(tài)機(jī)的輸出不僅與當(dāng)前狀態(tài)有關(guān),還與輸入信號(hào)有關(guān)。這表明如果需要根據(jù)不同的輸入信號(hào)來(lái)調(diào)整輸出,Mealy型狀態(tài)機(jī)可能是更合適的選擇。

狀態(tài)數(shù)需求:實(shí)現(xiàn)同等功能時(shí),Moore型狀態(tài)機(jī)需要的狀態(tài)數(shù)更多,因?yàn)镸ealy型狀態(tài)機(jī)可以根據(jù)狀態(tài)和輸入結(jié)合來(lái)看需不需要執(zhí)行相應(yīng)動(dòng)作,從而減少一些狀態(tài)。因此,如果項(xiàng)目允許,且對(duì)狀態(tài)數(shù)的要求不是特別高,使用Mealy型狀態(tài)機(jī)會(huì)更加高效。

設(shè)計(jì)原則與要求:在設(shè)計(jì)狀態(tài)機(jī)時(shí),需要考慮安全性、穩(wěn)定性、速度、面積以及設(shè)計(jì)的清晰度等因素。選擇Moore型或Mealy型狀態(tài)機(jī)應(yīng)基于這些綜合因素進(jìn)行權(quán)衡。

審核編輯:劉清

-

EDA工具

+關(guān)注

關(guān)注

4文章

268瀏覽量

32411 -

Verilog

+關(guān)注

關(guān)注

28文章

1363瀏覽量

111340 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

493瀏覽量

27950 -

fsm

+關(guān)注

關(guān)注

0文章

35瀏覽量

12919 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

460瀏覽量

28962

原文標(biāo)題:如何在Verilog中實(shí)現(xiàn)Moore型和Mealy型狀態(tài)機(jī)?

文章出處:【微信號(hào):雷達(dá)通信電子戰(zhàn),微信公眾號(hào):雷達(dá)通信電子戰(zhàn)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA工程師:如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)?

Verilog狀態(tài)機(jī)+設(shè)計(jì)實(shí)例

有限狀態(tài)機(jī)有什么類型?

MOORE型有限狀態(tài)機(jī)的幾種設(shè)計(jì)方法是什么

有限狀態(tài)機(jī)的硬件描述語(yǔ)言設(shè)計(jì)方法

狀態(tài)機(jī)和組合邏輯的冒險(xiǎn)競(jìng)爭(zhēng)淺析

正點(diǎn)原子開拓者FPGA視頻:狀態(tài)機(jī)

FPGA之狀態(tài)機(jī)的功能簡(jiǎn)述與學(xué)習(xí)建議

數(shù)字設(shè)計(jì)FPGA應(yīng)用:時(shí)鐘同步狀態(tài)機(jī)設(shè)計(jì)方法構(gòu)建序列發(fā)生器

FPGA之狀態(tài)機(jī)練習(xí):設(shè)計(jì)思路(4)

什么是狀態(tài)機(jī) 狀態(tài)機(jī)的描述三種方法

Verilog設(shè)計(jì)過(guò)程中狀態(tài)機(jī)的設(shè)計(jì)方法

序列檢測(cè)一定要用狀態(tài)機(jī)嗎?

評(píng)論