在Vivado下,有兩種方式管理IP。一種是創(chuàng)建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應(yīng)的IP會被自動添加到當前工程中;另一種是利用Manage IP,創(chuàng)建獨立的IP工程,缺省情況下,IP工程的名字為magaged_ip_project。在這個工程中生成所需要的IP,之后把IP添加到FPGA工程中。Xilinx推薦使用第二種方法,尤其是設(shè)計中調(diào)用的IP較多時或者采用團隊設(shè)計時。Tcl作為腳本語言,在FPGA設(shè)計中被越來越廣泛地使用。借助Tcl可以完成很多圖形界面操作所不能完成的工作,從而,可提高設(shè)計效率和設(shè)計自動化程度。Vivado對Tcl具有很好的支持,專門設(shè)置了Tcl Shell(純腳本模式)和Tcl Console(圖形界面模式)用于Tcl腳本的輸入和執(zhí)行。本文介紹了如何利用Tcl腳本在Manage IP方式下實現(xiàn)對IP的高效管理。

Manage IP的特點:

(1)Vivado在Manage IP模式下只顯示IP Catalog,便于直觀地定制IP;

(2)IP工程目錄獨立于FPGA工程目錄,可獨立管理并便于IP復(fù)用;

(3)對IP采用OOC(Out-of-Context)的綜合方式,生成相應(yīng)的DCP文件,添加到FPGA工程中,無需再次綜合;

與ISE Core Generator的不同之處:

(1)ISE Core Generator不同IP的生成文件會在同一目錄下,而Vivado下每個IP有獨立的文件夾,該文件夾下包含了IP所有相關(guān)文件,這為IP復(fù)用提供了便利;

(2)ISE Core Generator生成的IP定制文件為.xco,Vivado生成IP的定制文件為.xci;

(3)ISE Core Generator生成的網(wǎng)表文件為.ngc,Vivado生成的網(wǎng)表文件為.dcp,DCP不僅包含網(wǎng)表文件還包含約束文件;

(4)ISE Core Generator不支持Tcl腳本,Vivado則支持Tcl腳本;

Vivado下IP生成文件:

(1)用于綜合的RTL文件和約束文件;

(2)實例化模板文件;

(3)行為級仿真文件;

(4)綜合后的網(wǎng)表文件DCP;

(5)用于第三方綜合工具的Stub文件;

(6)例子工程;

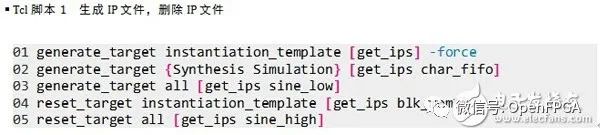

生成文件是可以定制的,這可通過generate_target命令完成,同時,生成的文件也可以通過reset_target被清除掉,如Tcl腳本 1所示。

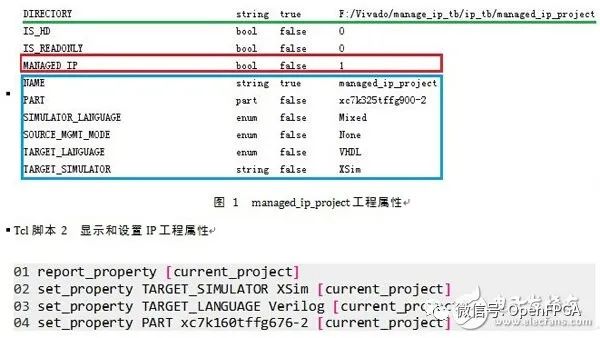

Vivado下每個對象都有自己的屬性,這些屬性可通過report_property顯示。managed_ip_project的屬性如圖 1所示。圖中綠色線條標記了該工程所在目錄;紅色方框MANAGED_IP屬性值為1,表明該工程為IP工程;藍色方框是我們創(chuàng)建或修改IP工程設(shè)置時最常用的一些屬性。Tcl腳本 2中第1行語句用于顯示IP工程屬性,第2~4行語句用于設(shè)置仿真工具、目標語言和芯片型號。set_property命令的第一個參數(shù)為屬性名,第二個參數(shù)為屬性值,第三個參數(shù)為屬性所屬對象。

采用Vivado Manage IP創(chuàng)建IP工程后,可能會遇到以下情況:(1)軟件版本升級,例如Vivado由2013.4升級至2014.2;(2)芯片型號改變,例如芯片型號由XC7K325TFFG676-2變?yōu)閄C7K160TFFG676-2;(3)A項目中的一些IP在B項目中也被使用,且這些IP參數(shù)配置完全相同。上述三種情況均可通過Tcl命令完成。

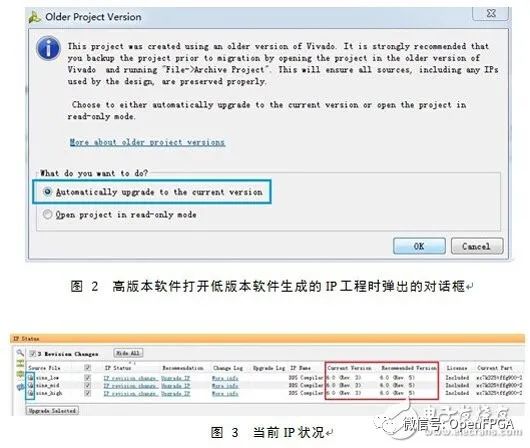

第一種情況:軟件版本升級

假如用Vivado 2013.4創(chuàng)建的IP工程,當軟件版本升級至2014.2時,需要將IP重新生成。此時,若用Vivado 2014.2打開該工程會彈出如圖 2所示的對話框。選擇圖中藍色方框標記的選項打開工程,通過report_ip_status命令顯示當前IP狀況,如圖 3所示。

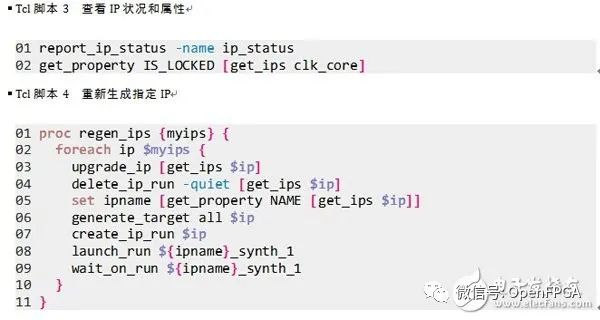

圖 3中藍色方框顯示了IP處于鎖定狀態(tài),可通過get_property查看IS_LOCKED屬性確定;紅色方框顯示了IP當前版本號和建議升級到的新版本號。相應(yīng)的Tcl腳本如Tcl腳本 3所示。對處于鎖定狀態(tài)的IP可選擇升級,這可通過Tcl腳本 4完成指定IP的升級。Tcl腳本 4可內(nèi)嵌到Vivado中作為用戶常用命令。

第二種情況:芯片型號改變

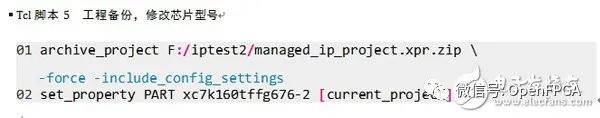

若芯片型號改變,首先要對舊型號芯片對應(yīng)的工程做備份處理,這可通過archive_project命令完成;然后修改芯片型號。相應(yīng)的Tcl腳本如Tcl腳本 5所示。完成這些操作之后,會發(fā)現(xiàn)IP處于鎖定狀態(tài),此時可通過Tcl腳本 4對IP升級。

第三種情況:A項目中的一些IP在B項目中也被使用,且這些IP參數(shù)配置完全相同

在這種情況下,可將A項目中的IP導(dǎo)入到B項目的IP工程中,這可通過import_ip命令完成,如Tcl腳本 6所示。Import_ip的第一個參數(shù)為原始IP所在目錄,第二個參數(shù)為該IP的新名字,缺省情況下與原始IP名一致。導(dǎo)入之后,可通過Tcl腳本 4重新生成IP。

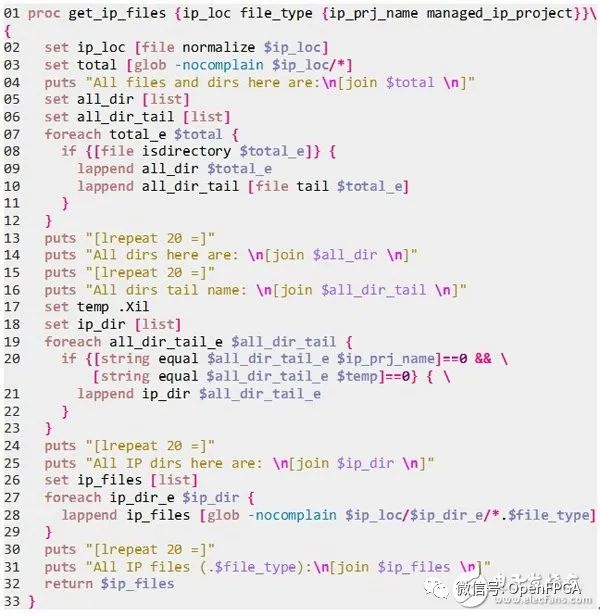

如前所述,Vivado下生成的IP都有獨立的文件目錄,在添加IP到Vivado FPGA工程中時,若采用圖形界面方式就需要一個一個地瀏覽到IP所在文件目錄,找到.xci文件,然后添加到工程中,如果調(diào)用的IP較多,顯然這種方式不夠高效。此時可用Tcl腳本 7所示的Tcl命令找到所有IP相關(guān)文件,文件類型可以是xci或dcp。該命令會返回完整的文件路徑,如Tcl腳本 6中的文件路徑。然后通過add_files命令將其添加到當前工程中。

此外,有些IP會有例子工程,這些例子工程帶有完整的測試激勵,可對IP進行仿真,以理解IP的輸入/輸出時序,也可單獨生成bit文件。可通過open_example_project命令打開例子工程,如Tcl腳本 8所示。

與ISE Core Generator相比,Vivado Manage IP對IP的管理更加便捷,加之Vivado對Tcl腳本的支持,利用Tcl腳本可實現(xiàn)對IP更高效的管理,進一步加強FPGA設(shè)計自動化的程度。

審核編輯:黃飛

-

FPGA

+關(guān)注

關(guān)注

1638文章

21860瀏覽量

609841 -

TCL

+關(guān)注

關(guān)注

11文章

1772瀏覽量

89295 -

Vivado

+關(guān)注

關(guān)注

19文章

820瀏覽量

67555

原文標題:在Vivado下利用Tcl實現(xiàn)IP的高效管理

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

在Vivado圖形化界面IDE中運行和調(diào)試Tcl命令

介紹IP數(shù)據(jù)報的格式及IP相關(guān)功能在Lwip中的實現(xiàn)方式

利用面向?qū)ο蠹夹g(shù)進行可配置的FFT IP設(shè)計與實現(xiàn)

利用FFT IP Core實現(xiàn)FFT算法

在LabVIEW中利用TCP_IP協(xié)議實現(xiàn)網(wǎng)絡(luò)通信_labview程序案例

在LabWindowsCVI 中利用TCP_IP協(xié)議_labview程序案例

在Vivado下利用Tcl腳本對綜合后的網(wǎng)表進行編輯過程

評論