易靈思提供了相關(guān)時(shí)序約束的PPT,內(nèi)容非常全面,但是我們還是發(fā)現(xiàn)很多客戶在使用Efinity時(shí),時(shí)序約束存在很多問題。

添加約束

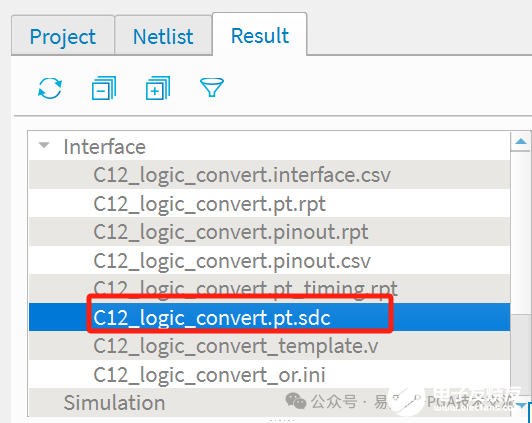

添加約束的目的是為了告訴FPGA你的設(shè)計(jì)指標(biāo)及運(yùn)行情況。在上面的生成約束之后,在Resultàxx.sdc中提供約束參考(請(qǐng)注意該文件不能直接添加到工程中,需要熱復(fù)制到別的指定目錄或者新建自己的SDC文件添加到工程)。

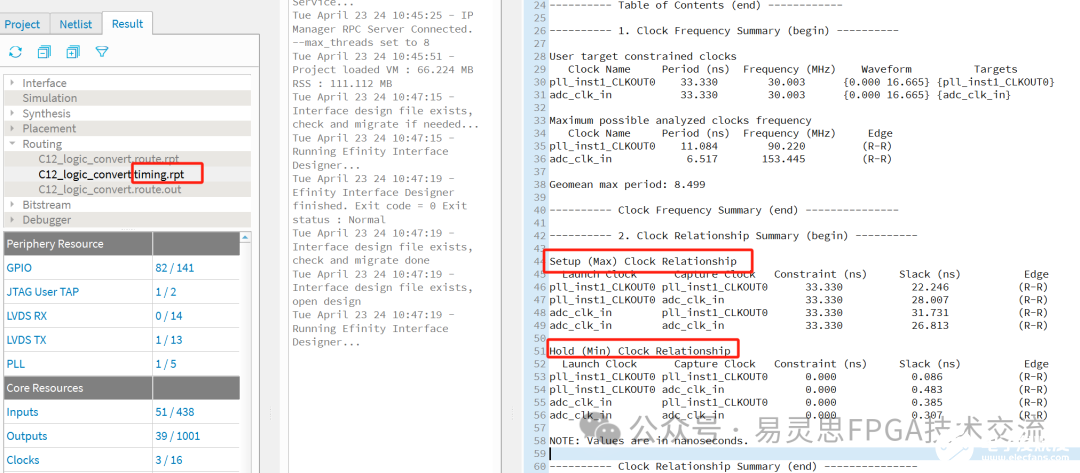

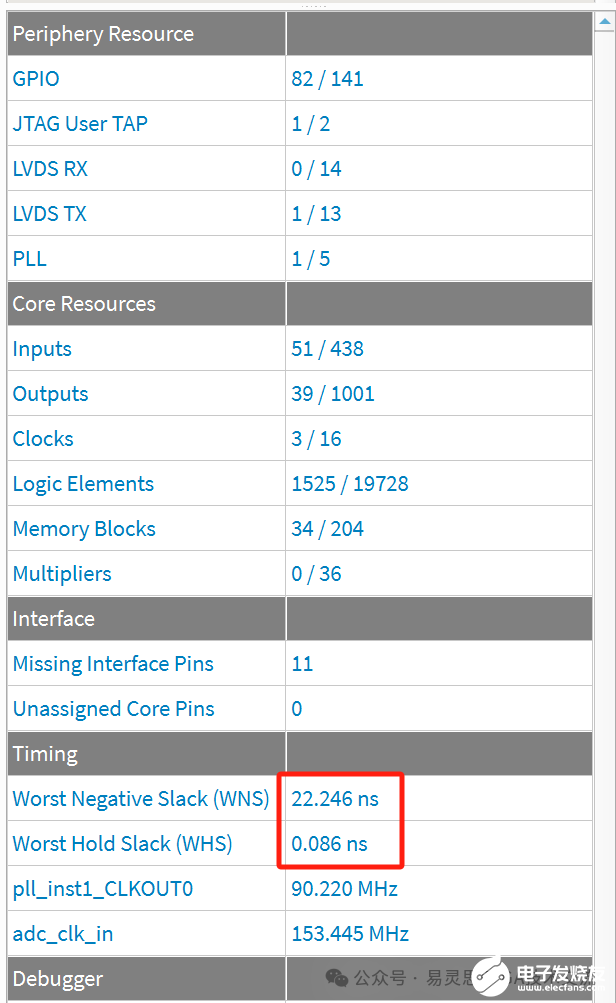

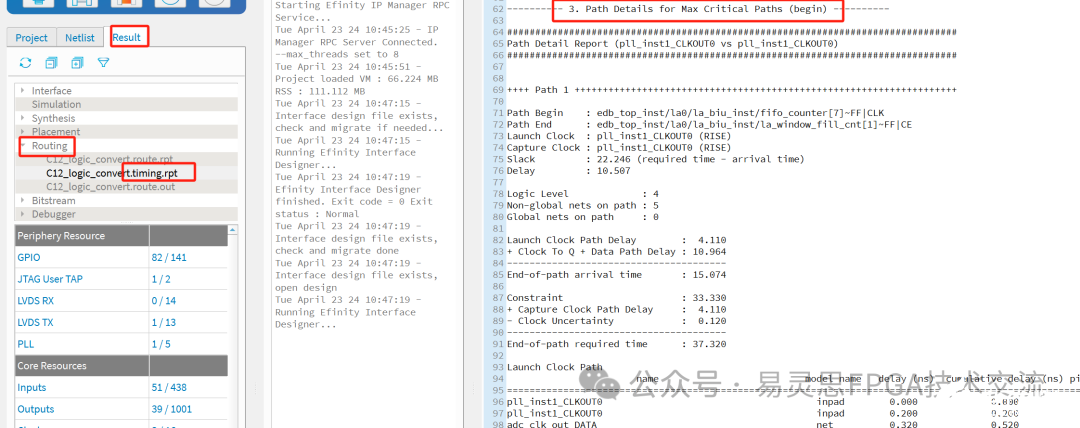

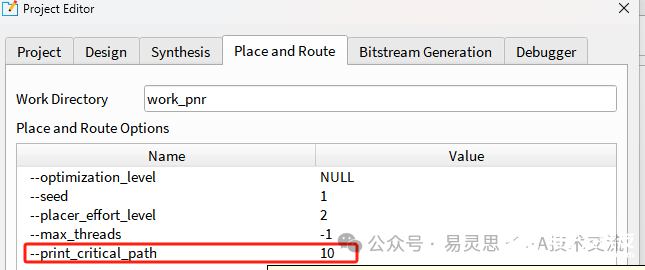

編譯完成之后可以查看時(shí)序報(bào)告,也可以通過routingàxx.timing.rpt來查看路徑詳細(xì)延時(shí)信息,如果想查看更可以通過指令來打印或者通過print_critical_path來控制打印的路徑數(shù)量 。

時(shí)鐘約束

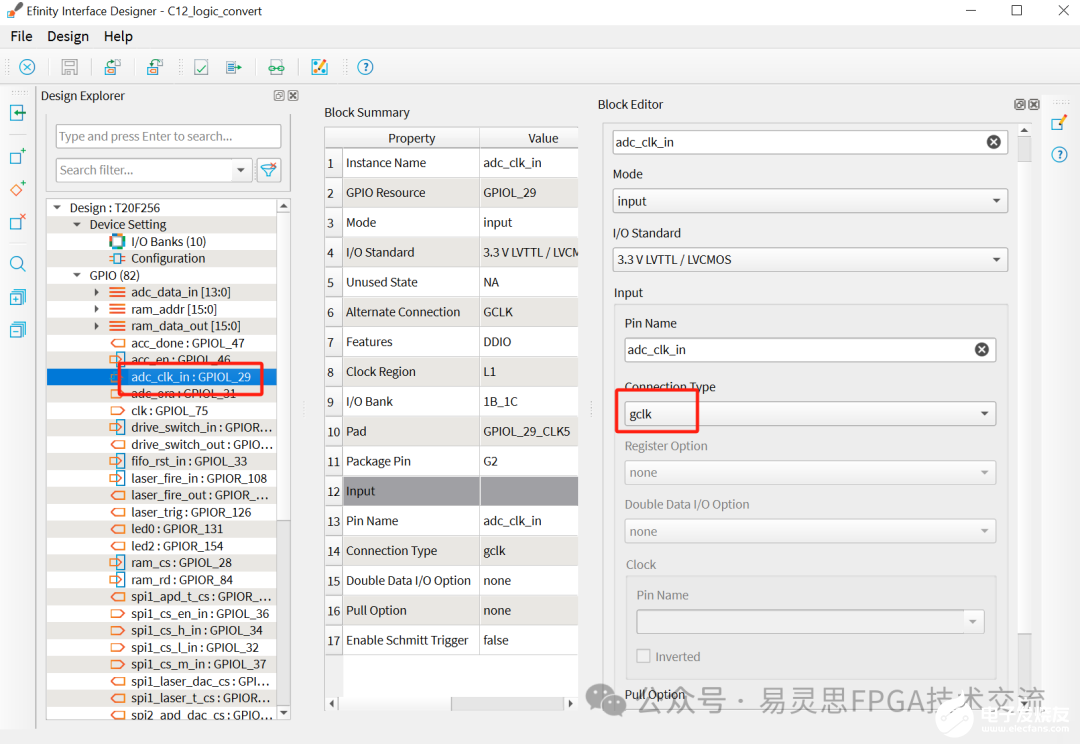

(1)通過IO輸入的gclk。

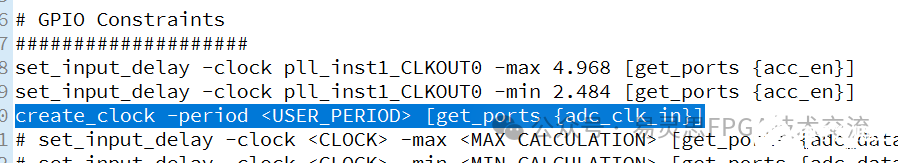

如下圖,因?yàn)闀r(shí)鐘是通過外部IO輸入的,所以FPGA并不知道這個(gè)時(shí)鐘頻率是多少。打開.pt.sdc可以看到提供相關(guān)約束參考。

我們只需要補(bǔ)充相關(guān)的時(shí)鐘周期即可以使用。

比如,我們要約束adc_clk_in為100M:

create_clock-period10.000[get_ports{adc_clk_in}]

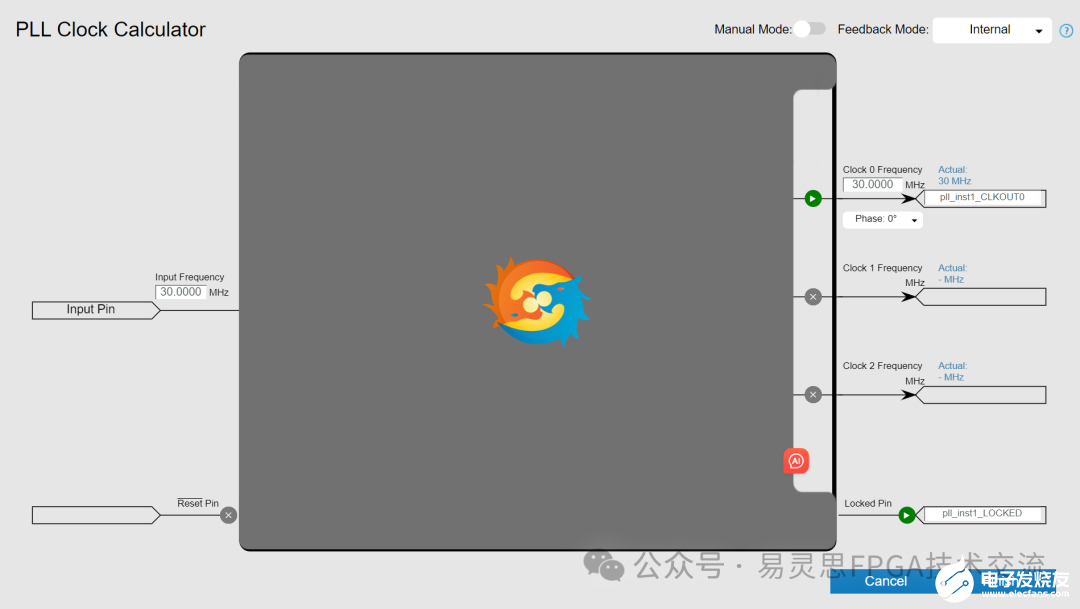

(2)PLL的輸出的時(shí)鐘約束。

因?yàn)镻LL的輸入輸出頻率都是設(shè)置好的,所以軟件可以檢測到。如下圖,輸入輸出時(shí)鐘頻率都是30MHz.

在pt.sdc文件中會(huì)提供相應(yīng)的約束 。

create_clock -period 33.3333 pll_inst1_CLKOUT0

在時(shí)鐘約束完成之后,可以查看Routing -->.timing.rpt文件中所有的時(shí)鐘是否都進(jìn)行了完整的約束 。

IO約束

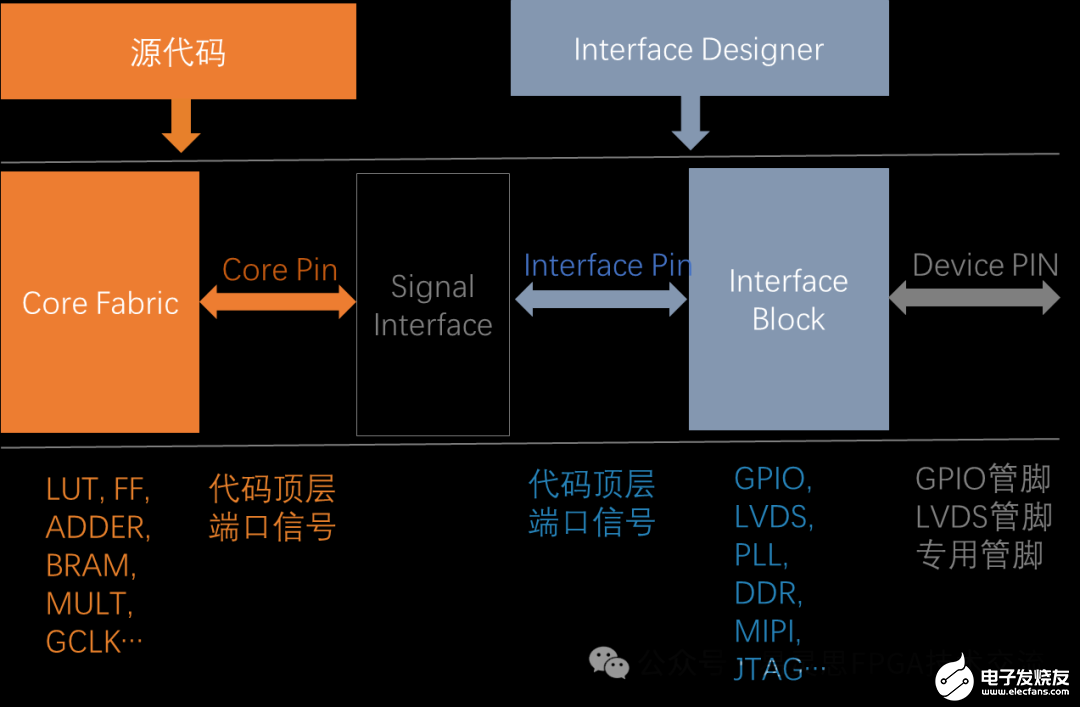

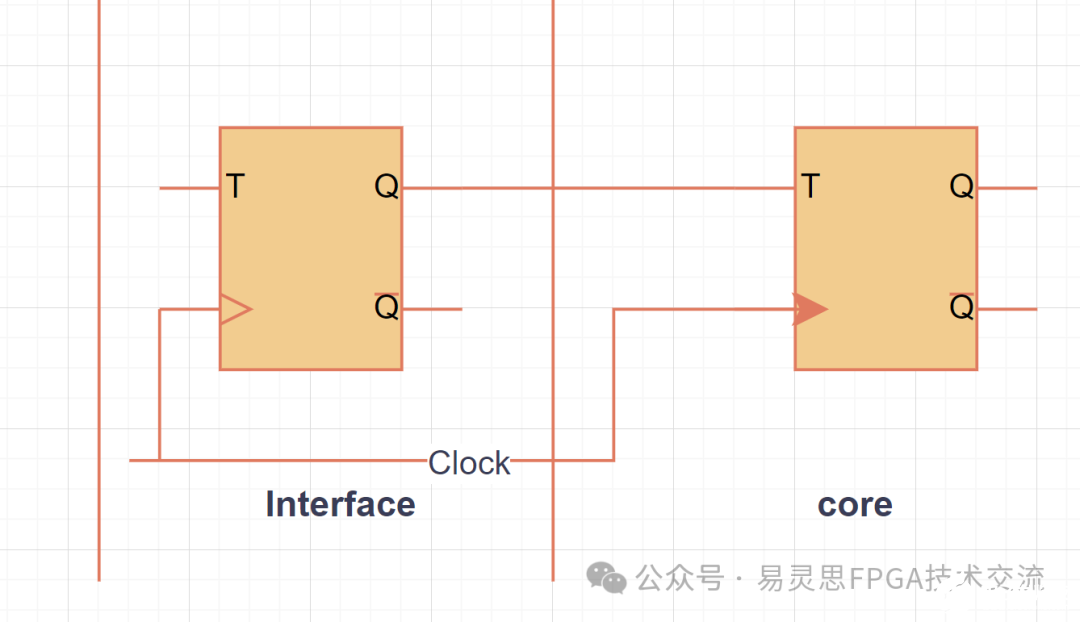

首先我們要了解易靈思的架構(gòu)是core和interface分開的,相對(duì)于core,interface內(nèi)部的GPIO,LVDS,JTAG及其它都是外設(shè)。所以所有針對(duì)于input_delay和outpu_delay的約束都是針對(duì)于interface的。至于FPGA對(duì)于我們平時(shí)理解的外設(shè),比如FPGA外部連接一片AD/DA,這種是沒有辦法約束的。

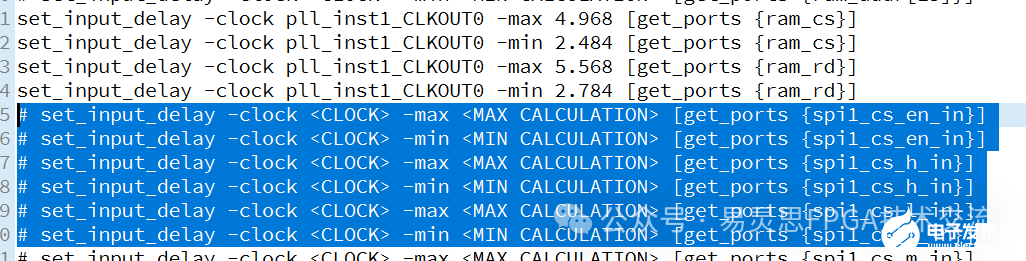

在pt.sdc文件中可以看到關(guān)于set_input_delay和set_output_delay的約束。可以看到有些約束是已經(jīng)屏蔽,那是因?yàn)樘砑拥腎O沒有打開寄存器。

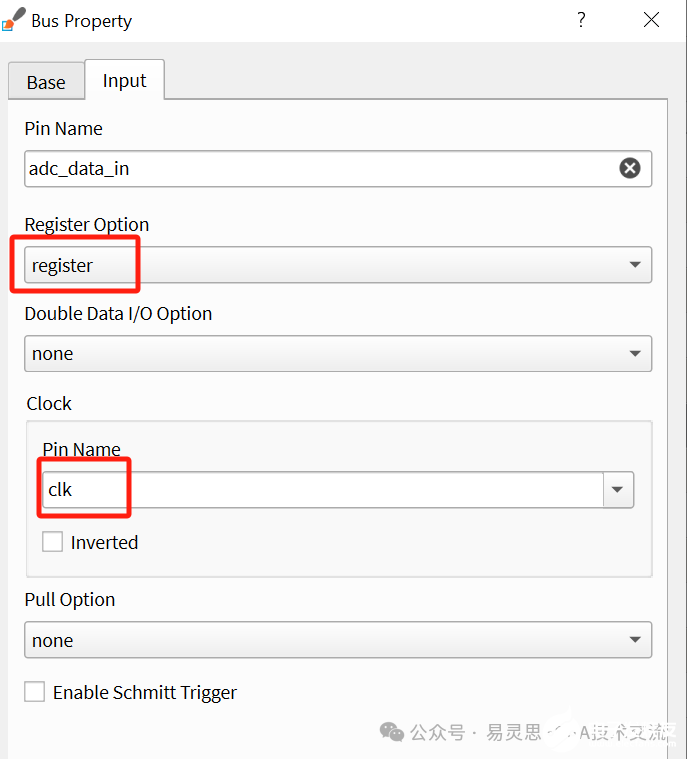

如下圖,易靈思建議把所有IO都添加上IO寄存器。

有的客戶會(huì)有疑問,clock的PIN Name是什么?其實(shí)就是與core內(nèi)連接的寄存器用什么時(shí)鐘,interface中就用什么時(shí)鐘。

(3)跨時(shí)鐘域約束

在保證程序上對(duì)跨時(shí)鐘域做了處理之后,約束上要對(duì)跨時(shí)鐘進(jìn)行約束 。跨時(shí)鐘約束的語法是set_clock_groups或者set_false_path,關(guān)于用于網(wǎng)上很多,可以自行查找。

set_clock_groups -asynchronous -group {jtag_inst1_TCK jtag_inst1_DRCK}

在所有時(shí)鐘約束完成之后要保證時(shí)序報(bào)告的slack都為正值。

編譯完成之后可以查看時(shí)序報(bào)告,也可以通過routingàxx.timing.rpt來查看路徑詳細(xì)延時(shí)信息

如果時(shí)序上還有違例,在result--> Routing-->timing.rpt文件中查看具體的路徑。根據(jù)路徑來解決具體的時(shí)序問題。

如果想查看更可以通過指令來打印或者通過print_critical_path來控制打印的路徑數(shù)量 。

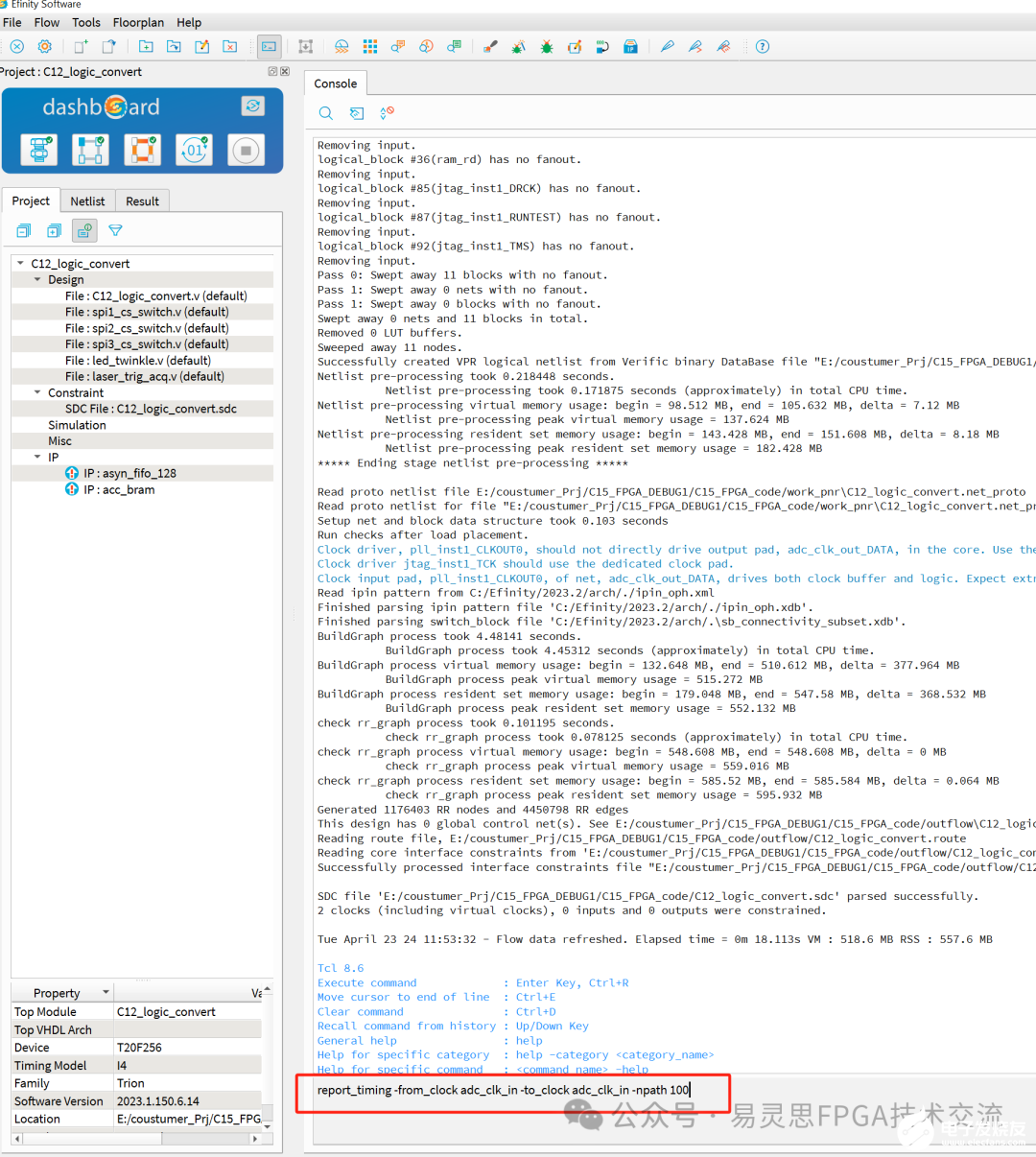

也可以通過report_timing來報(bào)告具體的時(shí)序路徑及數(shù)量。

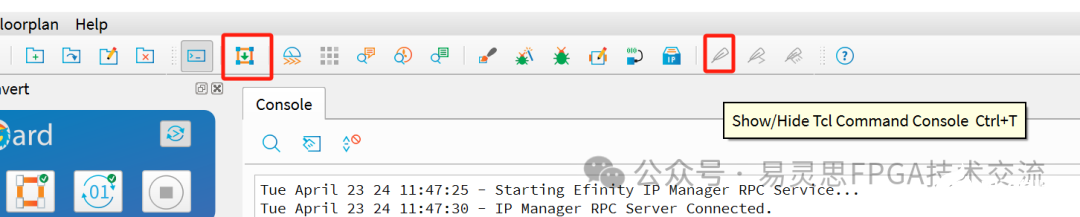

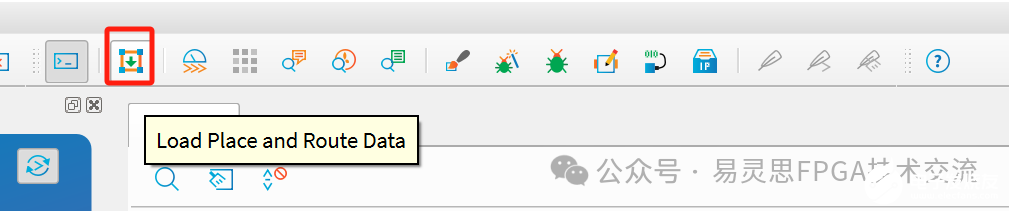

先打開Tcl CommandConsole,如果Show/Hide Tcl commandConsole是灰色的,要先點(diǎn)擊Load Place and Route Data加載布局和布線的數(shù)據(jù)。

打開Tcl commandconsolel,使用report_timing命令來查看需要的路徑。

具體report_timing的用法,請(qǐng)參考EfinityTiming Closure UserGuide.pdf。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21777瀏覽量

604718 -

pll

+關(guān)注

關(guān)注

6文章

780瀏覽量

135225 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1742瀏覽量

131637 -

時(shí)序約束

+關(guān)注

關(guān)注

1文章

115瀏覽量

13433

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

xilinx FPGA IOB約束使用以及注意事項(xiàng)

termius 中文,termius 中文的實(shí)操步驟,linux服務(wù)器遠(yuǎn)程連接的實(shí)用教程

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

常用時(shí)序約束使用說明-v1

Vivado使用小技巧

【實(shí)操文檔】在智能硬件的大模型語音交互流程中接入RAG知識(shí)庫

電路的兩類約束指的是哪兩類

啟明智顯Model3A芯片方案7寸高清觸摸屏:開箱、設(shè)置與實(shí)操全攻略指南

FPGA 高級(jí)設(shè)計(jì):時(shí)序分析和收斂

Xilinx FPGA編程技巧之常用時(shí)序約束詳解

FPGA工程的時(shí)序約束實(shí)踐案例

Xilinx FPGA的約束設(shè)置基礎(chǔ)

時(shí)序約束實(shí)操

時(shí)序約束實(shí)操

評(píng)論