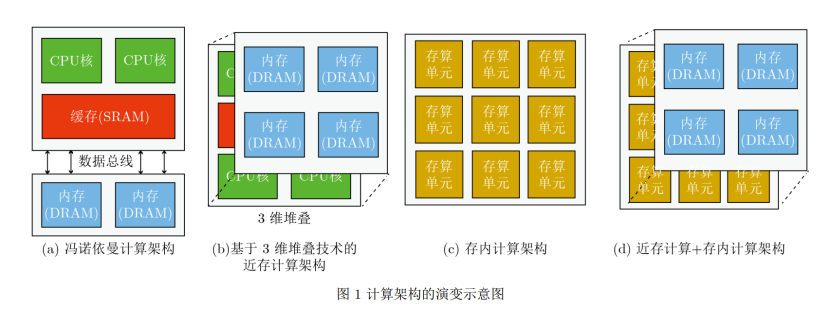

作為新的計算架構,存內計算(Computing In Memory,CIM)被認為是具有潛力的革命性技術。重點是將存儲與計算融合,有效克服馮·諾依曼架構瓶頸,并結合后摩爾時代先進封裝、新型存儲器件等技術,實現計算能效的數量級提升。

存儲介質是存內計算芯片重要的組成部分,基于不同存儲介質的芯片具有不同特點,下面我們將講述當前主流存儲介質。

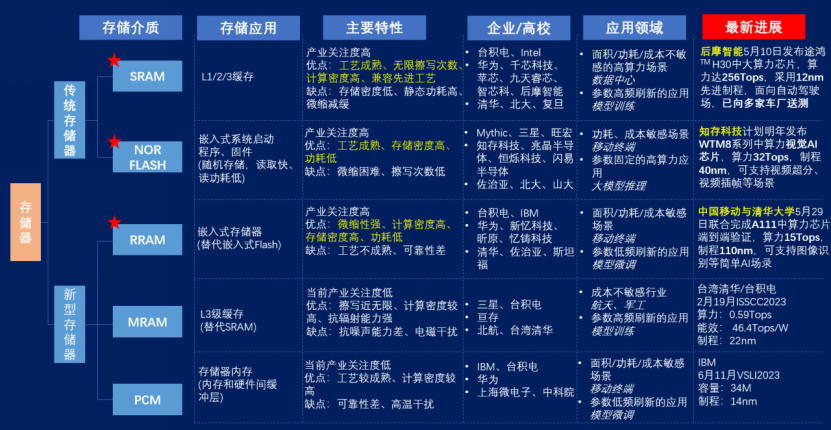

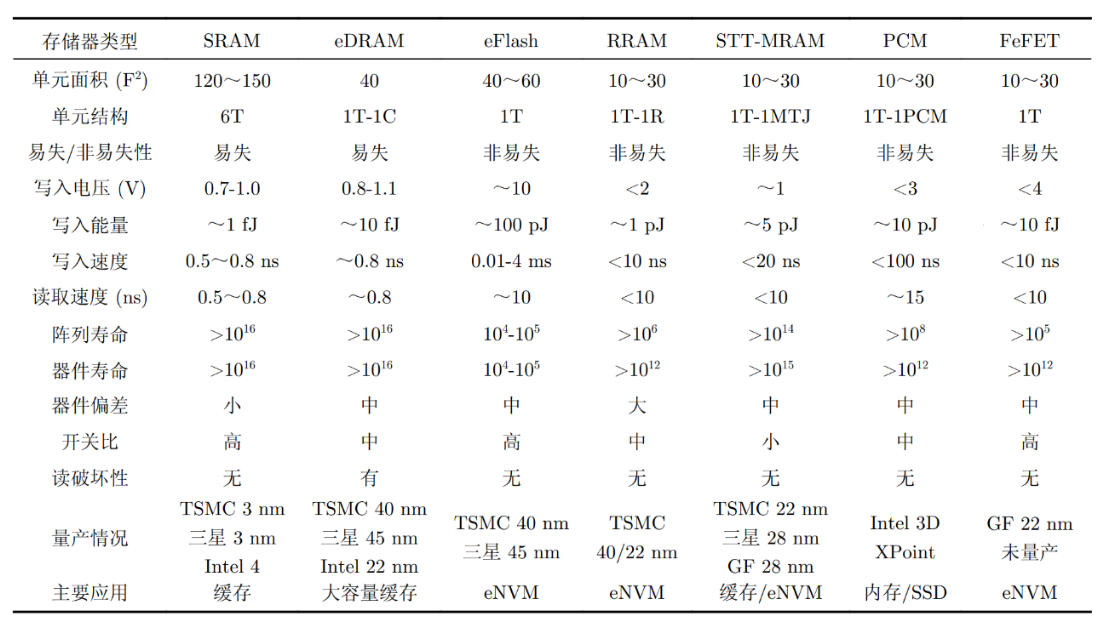

存儲介質有不同的分類方式。從數據保存上分,存儲介質主要分為兩大類:易失性存儲器(Volatile Memory,VM):電源開啟時數據存在,電源關閉則數據消失,如SRAM、DRAM等;非易失性存儲器(Non-Volatile Memory,NVM):存儲的數據不會因為電源關閉而消失,如RRAM、PCM、MRAM、NOR Flash等。從成熟度上分,可以得到如下圖表。

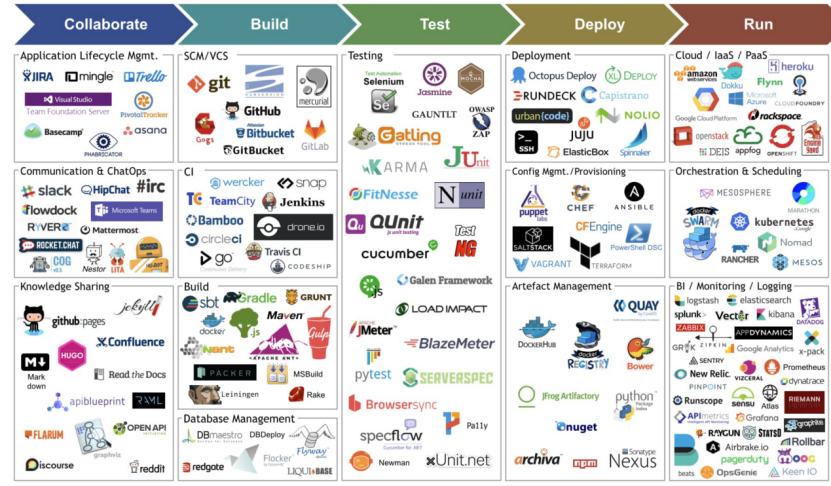

圖 1 存算一體主流技術路線最新總覽圖

(來源:“未來芯片:算力塑造未來”論壇-中國移動通信有限公司研究院-存算一體助力AI大模型的思考與展望)

下面我們將從易失性存儲器和非易失性存儲器兩個方面介紹存儲介質。

易失性存儲器,當前市面上常用的兩種易失性存儲器為SRAM與DRAM。

(1)SRAM[1]

SRAM全稱靜態隨機存儲器(Static Random Access Memory),需要一直通電才能使用,是一種易失性存儲器。Static(靜態),是指這種存儲器只要保持通電,里面儲存的數據就可以長時間保持。

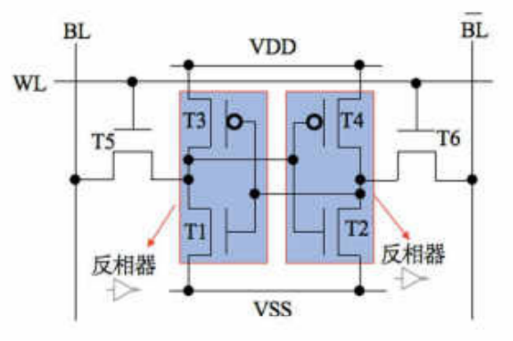

SRAM常用于CPU中的緩存,基本存儲單元由晶體管搭建而成,常見有6晶體管(6T)、8晶體管(8T)結構,圖2為6T SRAM結構。SRAM通過形成互鎖結構的兩個反相器來存儲數據,在設備供電時保持存儲數據不變,斷電后存儲數據丟失,呈現易失性。

圖 2 6T SRAM結構[2]

SRAM讀寫速度快、無讀寫次數限制,且工藝成熟,器件一致性和穩定性較好,適用于數字存算一體。基于SRAM的全數字存內計算可以做到較高的計算精度,并且可以較快實現技術落地與量產。例如在2021年的ISSCC 16.4中,臺積電提出一種基于6T SRAM的全數字存內計算宏,用于卷積神經網絡中的乘累加運算[3]。但SRAM價格昂貴、多晶體管單元結構下存儲密度較低、需要通電以保持數據,因此芯片面積、功耗較大,不適用于對成本和功耗敏感的場景。

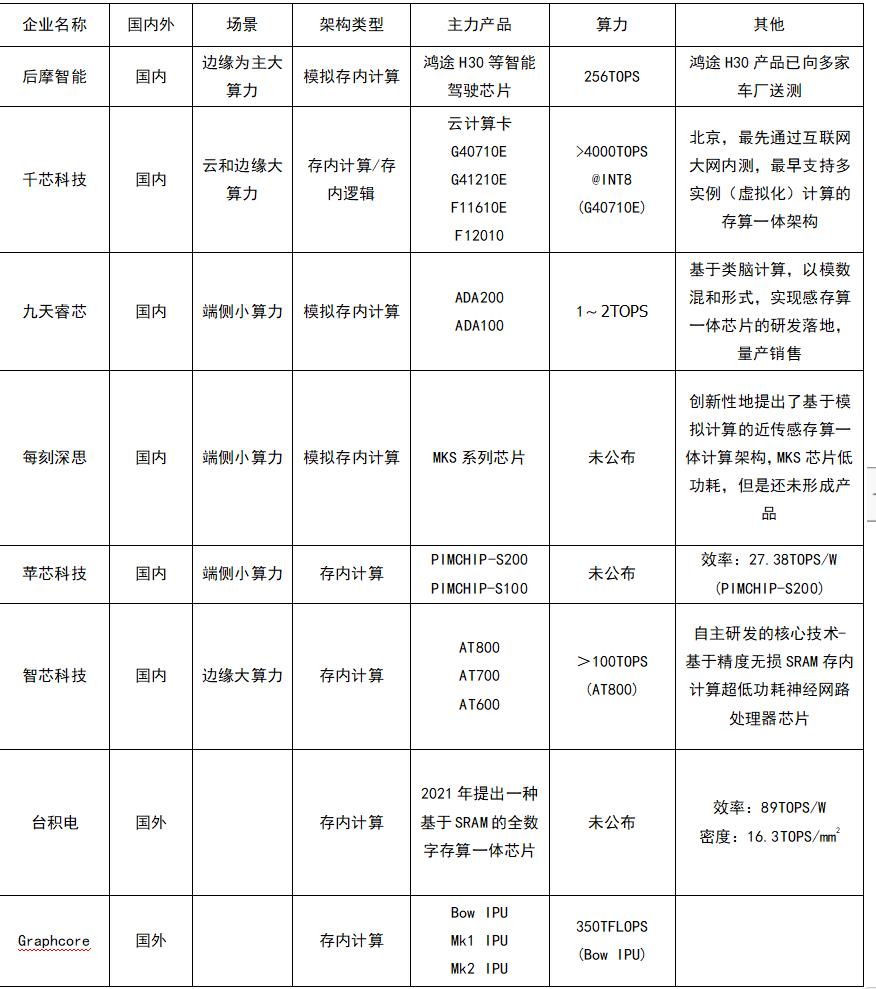

SRAM工藝成熟,目前已經有多家企業基于SRAM研發存算一體芯片,企業情況如下表所示,需要注意的是,以下信息均源于企業的公開資料,由于作者能力有限,未羅列全基于SRAM做存算一體芯片的企業,列舉的可能并非該企業的最新產品,而企業往往也只會公開產品發布時間點對其有利的部分數據,數據帶有宣傳性質,請酌情采信。

表1 基于SRAM的存算一體企業表格[4]

(2)DRAM

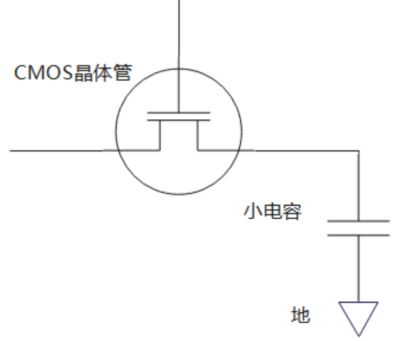

DRAM全稱動態隨機存儲器(Dynamic Random Access Memory),Dynamic(動態),是指DRAM存儲的數據需要周期性更新,和SRAM相對。DRAM將每位數據存儲在一個獨立的電容中,電容會隨著時間自然放電,需要定期刷新電荷,因此DRAM呈現易失性。

如圖3所示,DRAM基本單元結構由一個晶體管和一個電容組成。電容是存儲信息的關鍵,規定當電容存有電荷,單元存儲信息“1”,反之,單元存儲信息“0”。 打開晶體管后,通過在晶體管另一側施加電壓來存數據;通過電容是否放電來取數據[5]。

圖 3 DRAM基本單元結構[6]

DRAM需要1個晶體管和1個電容來存儲信息,而SRAM往往需要6個晶體管來存儲。因此DRAM密度高,單位體積的容量較高因此成本較低。但DRAM需要周期性刷新電荷,所以訪問速度較慢,耗電量較大。DRAM低速、高容量,主要應用于主存和內存等場景。此外,許多新技術逐漸產生,例如3D DRAM技術,是將存儲單元堆疊至邏輯單元上方,以增加單位晶圓面積上的產量。

非易失性存儲器

常見的非易失性存儲器有RRAM、PCM、MRAM、FeFET、NOR Flash等。

(1)RRAM

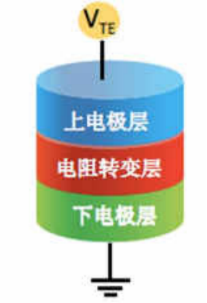

RRAM(Resistive Random Access Memory)又被稱為憶阻器,是一種極具潛力的新型非易失存儲器件,基本存儲單元為金屬-絕緣體-金屬或者金屬-絕緣體-半導體的三明治結構。 如圖4所示,上下為電極層,中間為絕緣的電阻轉變層。通過在電極層施加電壓/電流,電阻轉變層的電阻值可以實現高阻態和低阻態的切換,每種組態對應1或者0,這樣就可以存儲器信息。且電阻轉變層可以實現多級電阻狀態,使其可存儲多比特信息,這種電阻狀態改變是非破壞性的的,即斷電后也不會改變,這也是RRAM具有非易失性的原因。

圖 4 RRAM基本結構[7]

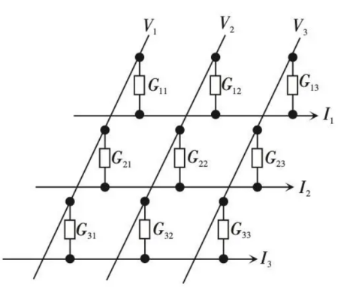

圖5 RRAM陣列[8]

如圖5,憶阻器電路可以做成陣列結構,與矩陣形狀類似,利用其矩陣運算能力,可以廣泛應用于Al推理場景中。在Al推理過程中,通過輸入矢量與模型的參數(也即權重)矩陣完成乘加運算,便可以得到推理結果。

以矩陣乘加運算為例,如圖5所示,將模型的輸入數據設為矩陣[V],模型的參數設為矩陣[G],運算后的輸出數據設為矩陣[I]。在運算前,模型參數被轉化為憶阻器阻值按行列位置存入憶阻器矩陣中(即[G]),在輸入端給定不同電壓值來表示輸入矢量(即[V]),根據歐姆定律(電流=電壓/電阻),便可在輸出端得到對應的電流矢量,再根據基爾霍夫定律將電流相加得到輸出結果的模擬值[I],經過ADC轉換,便得到輸出結果的數字值。多個存算陣列并行,便可完成多個矩陣乘加計算。

2023年10月,清華錢鶴、吳華強帶領團隊創新設計出適用于憶阻器存算一體的高效片上學習的新型通用算法和架構(STELLAR),研制出全球首顆全系統集成的、支持高效片上學習的憶阻器存算一體芯片,該成果已發表在《Science》上。

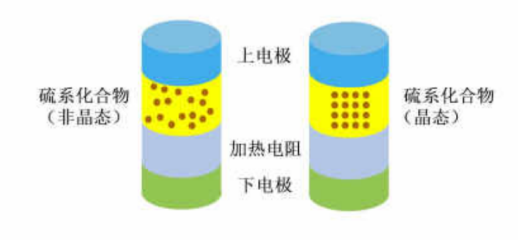

(2)PCM

PCM(Phase-change RAM)即相變存儲器,是一種由硫族化合物材料構成的非易失存儲器件,因為相變材料的兩種相在切換之后,即使在斷電的情況下也可以相對穩定地保持,這是因為相變涉及材料的結構重排,而這種結構變化是物理上的,并不依賴于持續的電源供應。如圖6所示,PCM器件的典型結構為上電極、硫族化合物、電阻加熱器、下電極。通過在兩電極間施加不同形式的脈沖,對硫族化合物加熱使其在晶態和非晶態之間轉變,來表征高低阻特性,分別對應1或0,從而實現數據的存儲和控制。

圖 6 PCM基本結構[9]

PCM有非易失、存儲密度高、多比特存儲、支持3D堆疊等優點, 但PCM存在寫入功耗較大、擦寫次數較少等問題尚需攻關,因此當前PCM主要還是作為大容量存儲器發展。基于PCM的存內計算研究相對較少,需要待產業進一步發展。

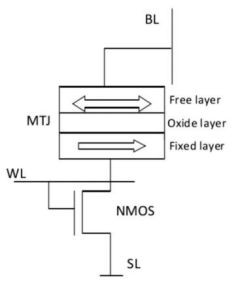

(3)MRAM

MRAM(Magnetoresistive Random Access Memory)是一種基于自旋電子學的新型非易失存儲器件,以磁隧道結(MTJ)為核心結構,利用隧道磁阻效應實現電阻狀態改變,每種電阻狀態對應1或者0,來達到存儲信息的目的,這種狀態改變不隨斷電而改變,因此也是非易失性存儲器。如圖7可見,MTJ是自由層-隔離層-固定層三明治結構。固定層的磁場方向保持不變, 施加電壓可改變自由層的磁場方向,當自由層和固定層磁場方向一致時, 器件呈現低阻態,代表邏輯“0”;當自由層和固定層磁場方向相反則為高阻態,代表邏輯“1”。

圖 7 MRAM基本結構[10]

基于MRAM的存內計算芯片具有非易失、訪問速度快、讀/寫次數高等優點,且具備較高的可靠性和穩定性,但MRAM器件成熟度較低,功耗、速度和耐久性等指標離理論預期尚有一定差距。當前業界基于MRAM的存內計算研究較少,需要推動器件成熟,同步挖掘其在存算一體領域的潛在場景。對于MRAM的相關研究,北航集成電路學院在MRAM領域的研究較多并已經做出了相當多的成果。

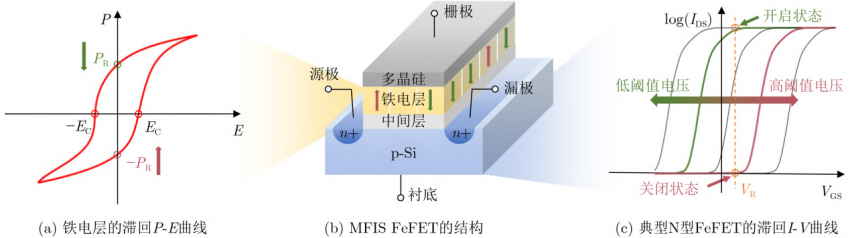

(4)FeFET[11]

FeFET(Ferroelectric Field Effect Transistor)具有極低的寫功耗、快速的讀取操作以及與CMOS兼容的高微縮能力等特點,這使基于FeFET的存儲與CiM電路在密度和能效上的優勢尤為突出。但FeFET仍存在工藝成熟度、可靠性和壽命上的不足。圖8(b)展示了被廣泛研究的金屬-鐵電-絕緣層-半導體(Metal-Ferroelectric-Insulator-Semiconductor, MFIS)FeFET結構,該結構在晶體管的柵極堆疊中嵌入鐵電材料作為鐵電層,如圖8(a)所示,在施加電場時鐵電層的極化狀態同電場強度呈滯回特性,其極化狀態在移除電場后仍能夠保持不變。

FeFET的工作原理在于鐵電層可以通過極化電荷對溝道施加場效應,從而控制晶體管的閾值電壓。如圖8(c)所示,FeFET的寫入過程具有滯回特性,可以通過調整寫入脈沖的幅度、寬度和次數來實現多值存儲。由于寫入操作中漏極與源極的電壓可以相同,FeFET實際上具有容性的寫入負載,寫操作功耗極低。

圖 8 FeFET基本結構及性質

(5)NOR Flash[12][13]

Flash 存儲器根據其內部架構和實現技術可以分為AND、NAND、NOR幾種,目前占據主流市場的有NOR Flash和NAND Flash兩大類。它們都將存儲單元組織為塊陣列。塊是擦除操作的最小單位,頁是讀、寫操作的基本單位。NAND Flash的頁大小通常為512B、2KB、4KB,而NOR Flash能夠以字節為單位進行數據訪問。

NOR Flash以并行的方式連接存儲單元,具有分離的控制線、地址線和數據線,具有較快的讀速度,能夠提供片上執行的功能。但寫操作和擦除操作的時間較長、且容量低、價格高。因此NOR Flash多被用于手機、BIOS芯片以及嵌入式系統中進行代碼存儲。

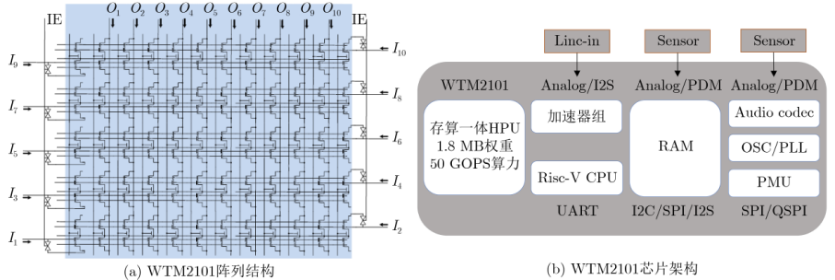

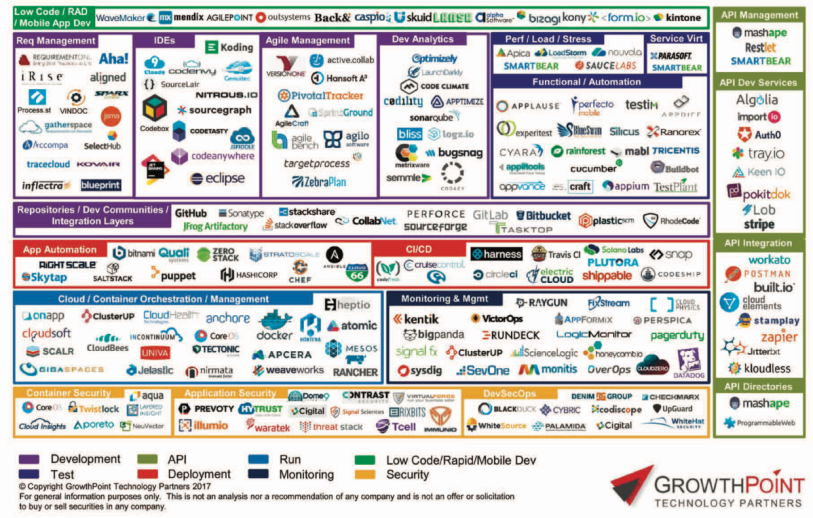

而在存內計算應用中,每個Flash存儲器件的要存儲遠超存儲應用下的bit位數,bit之間裕度更小、閾值電壓飄逸、行串擾問題更加嚴重。知存WTM2101使用特殊的電路設計抑制閾值電壓漂移對計算精度的影響。為了同時實現低功耗計算與低功耗控制,WTM2101結合了RISC-V指令集與NOR Flash存內計算陣列,其陣列結構與芯片架構如圖9所示,包括1.8 MB NOR Flash存內計算陣列,一個RISC-V核,一個數字計算加速器組,320 kB RAM以及多種外設接口。

圖 9 WTM2101芯片陣列及架構

(6)混合型存儲器

由于目前還沒有一種完美的存儲器能夠同時實現低成本、高訪問速度、低能耗和高可靠性,為了在應用中實現一種具備這些優點的存儲方式,其中一種思路就是將不同存儲器混合使用[14]。文獻[15]提出了一種將RRAM和SRAM存儲器混合使用的方法,使用RRAM存儲權重數據,因為它是非一時性存儲器,具備零泄漏的特點,可以減少維持權重數據的功率開銷;使用SRAM用于存儲激活(storing activation),因為它的讀寫速度快,可以頻繁更換數值。

總結

存儲器繁多、各具特點。具體到存內計算而言,由于不同類型的存儲器幾乎都需要“定制”不同的電路、控制方式等與其匹配,才能使其作為存內計算來使用。從具體使用的角度來看,應考慮具體應用場景的需求來選擇存內計算的計算范式和使用的器件。從市場的角度來看,當前具備成熟生產條件的RRAM、Flash存儲器或許是當前推動存內計算落地應用的重要方向。

表2 不同存儲介質對比[16]

參考文獻:

[1][2][7][9] 存算一體白皮書(2022年),中國移動通信有限公司研究院.

[3] Y. -D. Chih et al., "16.4 An 89TOPS/W and 16.3TOPS/mm2 All-Digital SRAM-Based Full-Precision Compute-In Memory Macro in 22nm for Machine-Learning Edge Applications," 2021 ISSCC, San Francisco, CA, USA, 2021, pp. 252-254.

[4] 存算一體芯片賽道企業收錄(收錄于存算一體芯片賽道投資融資分析,持續更新,上次更新于20230226) - 知乎.

[5][6] 深入內存/主存:解剖DRAM存儲器 - 知乎.

[8] 針對憶阻器的工作原理和發展的研究 - 知乎.

[10] 存算一體:MRAM席卷而來 - 半導體產業縱橫.

[11][16] 劉勇,李泰昕,祝希等.基于鐵電晶體管的存儲與存算一體電路[J].電子與信息學報,2023,45(09):3083-3097.

[12] 鄭文靜,李明強,舒繼武.Flash存儲技術[J].計算機研究與發展,2010,47(04):716-726.

[13] 郭昕婕,王光燿,王紹迪.存內計算芯片研究進展及應用[J].電子與信息學報,2023,45(05):1888-1898.

[14] K. Johguchhi, "A Smart Hybrid Solid-State-Drive Storage System based on Nonvolatile Storage-Class-Memories : Device, Circuit Design and Architecture," 2020 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 2020, pp. 1-2, doi: 10.1109/ISDCS49393.2020.9263016.

[15] M. Rios, F. Ponzina, G. Ansaloni, A. Levisse and D. Atienza, "Running Efficiently CNNs on the Edge Thanks to Hybrid SRAM-RRAM In-Memory Computing," 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2021, pp. 1881-1886, doi: 10.23919/DATE51398.2021.9474233.

審核編輯 黃宇

-

芯片

+關注

關注

455文章

50816瀏覽量

423613 -

DRAM

+關注

關注

40文章

2315瀏覽量

183489 -

存儲器

+關注

關注

38文章

7492瀏覽量

163834 -

sram

+關注

關注

6文章

767瀏覽量

114689 -

存內計算

+關注

關注

0文章

30瀏覽量

1380

發布評論請先 登錄

相關推薦

存內計算芯片研究進展及應用

探索存內計算—基于 SRAM 的存內計算與基于 MRAM 的存算一體的探究

存內計算芯片的基石-存儲介質匯總

存內計算芯片的基石-存儲介質匯總

評論