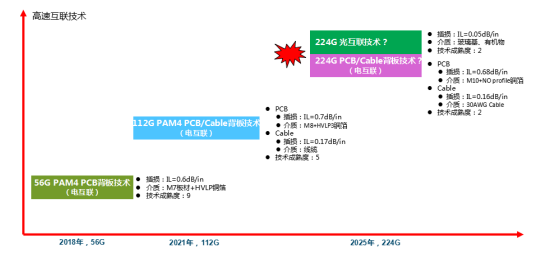

隨著電子設備越來越先進,集成電路封裝尺寸也變得越來越小,但這不僅僅是為了提高引腳密度。較高的引腳密度對于具有許多互連的高級系統非常重要,但在更高級的網絡器件中,還有一個重要的原因是要為這些系統中運行的互連器件設定帶寬限制。224G 系統和 IP 正在從概念過渡到商業產品,這意味著封裝設計需要滿足這些系統的帶寬要求。

封裝中的“高帶寬”并不是一個新概念,而且封裝設計人員知道如何構建可在極高頻率下工作的互連。例如,在 MMIC 中,接口能以相對較高的功率提供高頻率,即使沒有高密度封裝也能做到這一點。這些封裝并不是新興事物,它們已經在某些實例中使用了幾十年。

224G 系統和這些系統的未來一代產品所面臨的挑戰是,需要實現從直流到極高頻率的高帶寬。這意味著 BGA 封裝、封裝基板、封裝中介層和內部封裝布線的設計必須能在最低階的模式傳播機制下運行。

1

高速接口的封裝布線方式

新一代數據中心架構的正常運行離不開正確的封裝,這種封裝能夠支持基本 (TEM) 模式下的超高頻模式傳播。根據傳輸線理論,在傳輸線設計中,假定相關信號以 TEM 模式傳播,這在信道的最低帶寬要求下依然適用。這些因素尤其會影響信號在封裝中的傳播行為:

封裝底部 BGA bump 之間的間距

半導體晶粒上 bump 之間的間距

封裝內部的布線(即跨層布線)

再分布層 (RDL) 中內部走線的尺寸

對封裝中內部布線的每個部分進行分析,可以發現這些因素在何處收斂,以確定封裝的帶寬限制。要知道,這些因素中的任何一個都會限制封裝的總帶寬,從而限制從封裝到 PCB 或連接器的頻率。

考慮到 224G 信道的帶寬限制,應使用焊球間距不超過 0.8 mm 的封裝尺寸來支持 56 GHz 寬帶信道。這與英特爾公司提供的仿真數據以及利用過渡過孔周圍的整體空腔面積得出的基本計算結果相吻合。

使用封裝底部的焊球排列進行簡單計算,可以估算出 TEM 模式的頻率限制。計算過程如下——

首先,利用 4 焊球 x 3 焊球的方形區域、封裝基底材料的介電常數和 0.8 mm 的焊球間距限制,得出半波長截止頻率:

F =(真空中的光速)/[sqrt(Dk) * 0.8mm * 2 * 2]

如果基板材料是 ABF,則 Dk = 3.5,近似截止頻率為 F = 50 GHz。這與 802.3 工作組的仿真數據和測試數據中的估計值相似,他們將 0.8 mm 間距封裝的截止頻率設定為 59 GHz。

對于封裝內部,可以使用類似的計算方法來確定一階(TE 或 TM)模式——

假設我們在差分對與接地平面之間使用上下各約 40 微米的帶狀線,在封裝的過孔柵欄之間使用 120 微米的帶狀線。這些帶狀線的 TEM 截止頻率大約為:

F =(真空中的光速)/[sqrt(Dk) * 0.12mm * 2]

由此得出的結果是 667 GHz。封裝內部的實際布線要復雜一些,但這一基本估計值說明了封裝設計可以支持的高帶寬。在這個簡單的例子中,即使帶狀線與接地平面的距離大一個數量級,也能輕松支持 224G PAM-4 信號。

2

封裝如何達到帶寬限制

接下來的兩節中,我們將詳細介紹如何達到上述 TEM 模式傳播的頻率限制。

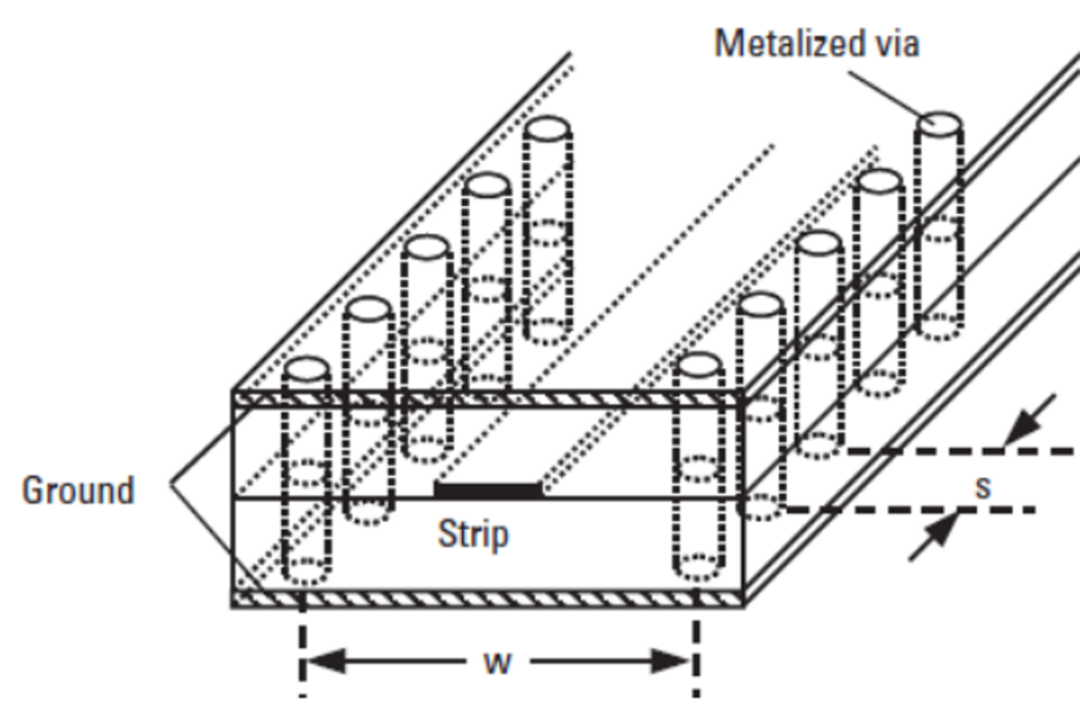

封裝傳輸線中的 TEM 和非 TEM 模式

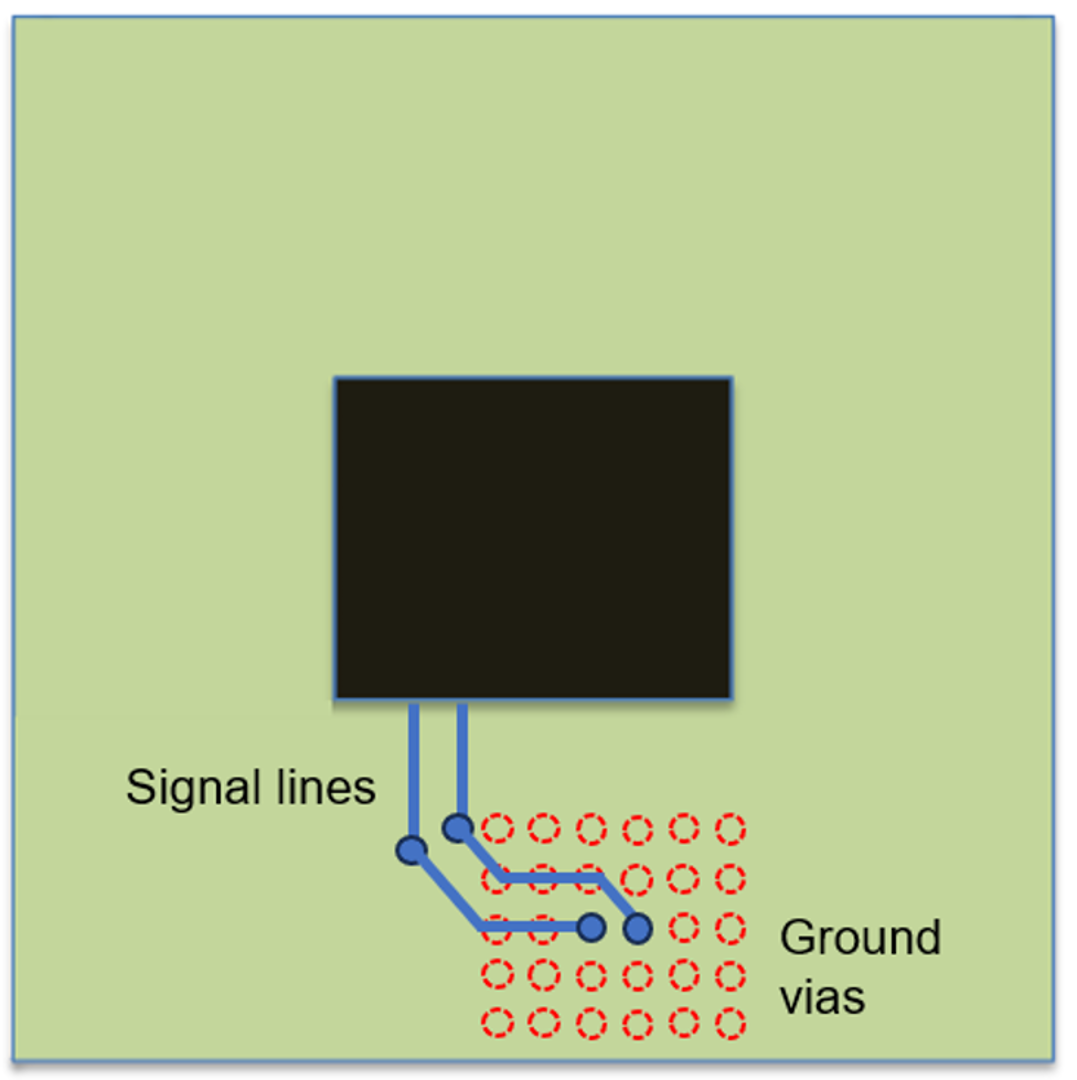

傳輸線(特別是用于封裝布線的帶狀線)的尺寸非常小,可以實現非常高的 TEM 模式帶寬截止頻率。下圖是這些傳輸線的典型布線方式;其中包括在過孔柵欄之間布線(通常是差分布線),以設置線路阻抗并在附近線路之間提供屏蔽。

確定封裝中使用的帶狀線帶寬截止頻率的參數。

在用于封裝的帶狀線中,決定單根帶狀線中 TEM 模式帶寬截止頻率的因素同樣適用于差分帶狀線。將差分帶狀線用于速度極高的 224G 通道,是為了使封裝不會從封裝基板邊緣產生強烈輻射。因為 W 的尺寸較小(約 0.1 mm),TEM 帶寬限制非常高,所以傳統封裝在高頻率下也能很好地工作。

焊球間距造成的 TEM 限制

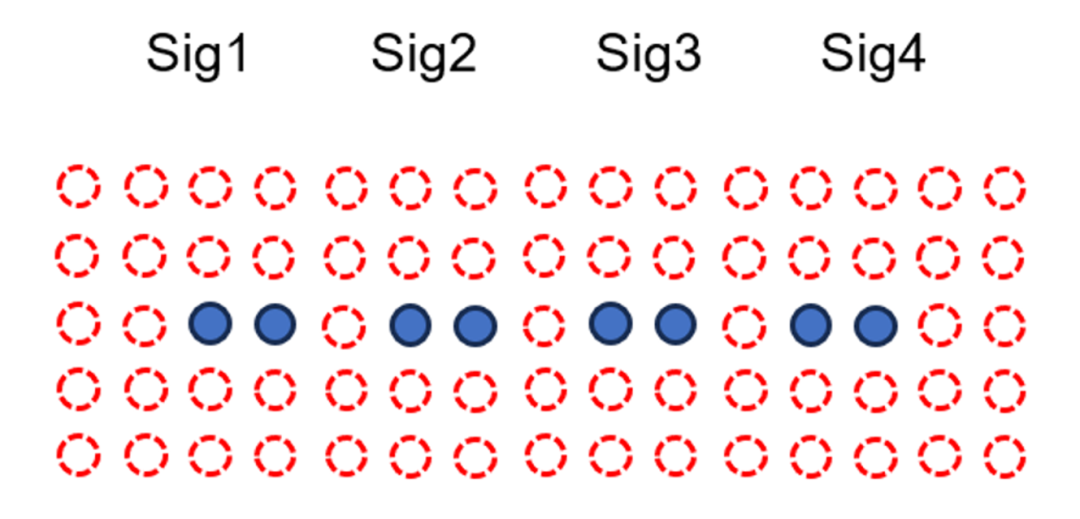

在封裝中,焊球間距也會產生類似的帶寬限制效應。這是因為高級處理器和 FPGA 高數據速率接口的封裝會用接地引腳將信號引腳包圍起來。這些引腳在封裝底部形成了一個同軸差分對。典型的引腳排列如下圖所示,標紅的引腳是與 PCB 的接地連接。

典型的封裝焊球排列。

封裝底部的每個信號引腳都是差分對的一部分。信號引腳周圍距離最近的接地引腳負責確定 TEM 模式截止頻率,因為這些信號焊球周圍的區域看起來就像一個矩形封閉空腔,所以對于較小的空腔,其最低諧振模式的截止頻率通常更低。這是因為過孔的作用類似于過孔柵欄,它們有兩種功能:

將信號功率限制在過孔周圍,以減少串擾

影響連接封裝和 PCB 的差分過孔的阻抗

一旦信號帶寬超過 TEM 截止頻率,部分信號將以高階模式(TE 或 TM 模式)傳播,該模式將在不同封裝區域的導體周圍呈現出一定的波形。首先,在跨層區域,每根銅線周圍都可能存在 TEM 模式,這種模式會阻礙信號在 56 GHz 以上的帶寬中進行寬帶傳播。在封裝底部的焊球區域,可能會存在一種 TEM 模式,位于進入 PCB 焊盤的成對焊球周圍。對于在 224G 下使用差分對的現代 ASIC 而言,這兩種情況都不太理想。

3

如何評估封裝帶寬

上述計算只是一種粗略的計算方法,將帶狀線或封裝 bump 對近似為矩形波導。但由于過孔/焊球間距和中心導體的影響,封裝布線實際上并不是以這種方式工作的。

確定信號行為和信號導體周圍電磁場的唯一方法是使用電磁場求解器。使用場求解器計算出的數據,為 224G 封裝的每個部分建立仿真模型。這些仿真工具的基本流程如下:

使用電磁場計算結果來確定封裝互連 (bump-to-bump) 各部分的 S 參數

將 S 參數回歸到網絡各部分的線性網絡中

可以修改從 S 參數數據中提取的線性網絡,以優化信道模型

可將其他因素(如均衡和 PCB 上的傳輸線)添加到模型中

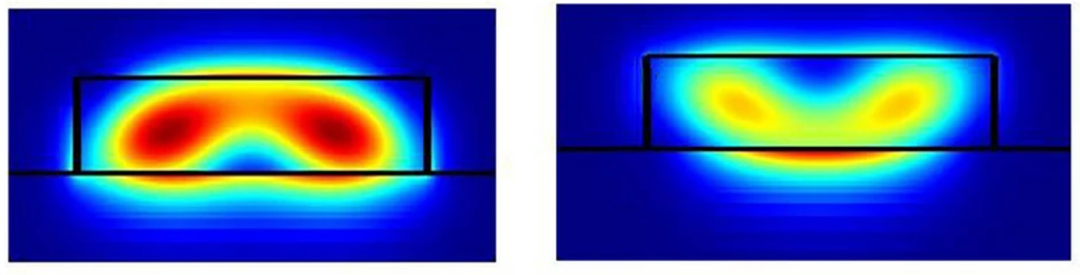

可以通過觀察強度模式(通常是二維平面上的彩色強度圖)來觀察從 TEM 行為到非 TEM 行為的過渡。下圖是一個矩形介質波導的簡單示例,其中電磁波進入了兩種不同的模式(TE 和 TEM)。

總之,在設計互連幾何結構時,封裝設計人員不僅要考慮低損耗,還要考慮高帶寬。目前,限制信道帶寬的主要因素是封裝上的焊球間距。這意味著按照摩爾定律,如果帶寬再增加一倍,封裝尺寸就可能達到傳統封裝制造技術的極限。在考量封裝設計時,應該對整個互連過程進行仿真,從封裝內的 bump-to-bump 開始。

封裝是確保器件正常運行的最后一步。如果您的設計團隊需要了解封裝設計與涉及 PCB 和連接器的互連之間的相互作用,Cadence Allegro X Advanced Package Designer(Allegro X APD)為集成電路封裝提供了先進的設計和分析工具,可以設計和仿真 224G PAM-4 系統,用于實現高效的引線鍵合設計技術、約束感知基板互連設計以及詳細的互連提取、建模和信號完整性/供電分析,同時集成了用于熱分析的多物理場求解器,助力設計人員有效驗證在散熱方面要求嚴苛的芯片和封裝設計。

-

集成電路

+關注

關注

5412文章

11837瀏覽量

365836 -

asic

+關注

關注

34文章

1237瀏覽量

121619 -

封裝

+關注

關注

128文章

8303瀏覽量

144304 -

MMIC

+關注

關注

3文章

632瀏覽量

24807

發布評論請先 登錄

相關推薦

HPC需求高速增長推動224G以太網SerDes技術發展加速

古希臘掌管224G 的神 | Samtec 224G PAM4 高速互連大合集!

0805封裝尺寸/0402封裝尺寸/0603封裝尺寸/1206封裝尺寸

展望未來英特爾FPGA設計,介紹新型224G PAM4收發器

ASIC,ASIC是什么意思

Molex莫仕推出業界首個芯片到芯片224G連接器組合

CIOE參展手札 | Samtec 224Gbps PAM4性能演示精彩亮相

淺談下一代數據中心中的224G PAM-4架構

Samtec技術前沿 | 全新224G互連產品系列現場演示

TE AdrenaLINE 224G連接器產品組合介紹

224G 高速互聯對 PCB 及覆銅板需求及激光錫球植球機的助力(上)

224G 高速互聯對 PCB 及覆銅板需求及激光錫球植球機的助力(下)

AI領域市場爆發,解讀224G技術下高速互連方案

評論