來(lái)源:中國(guó)科學(xué)院微電子研究所

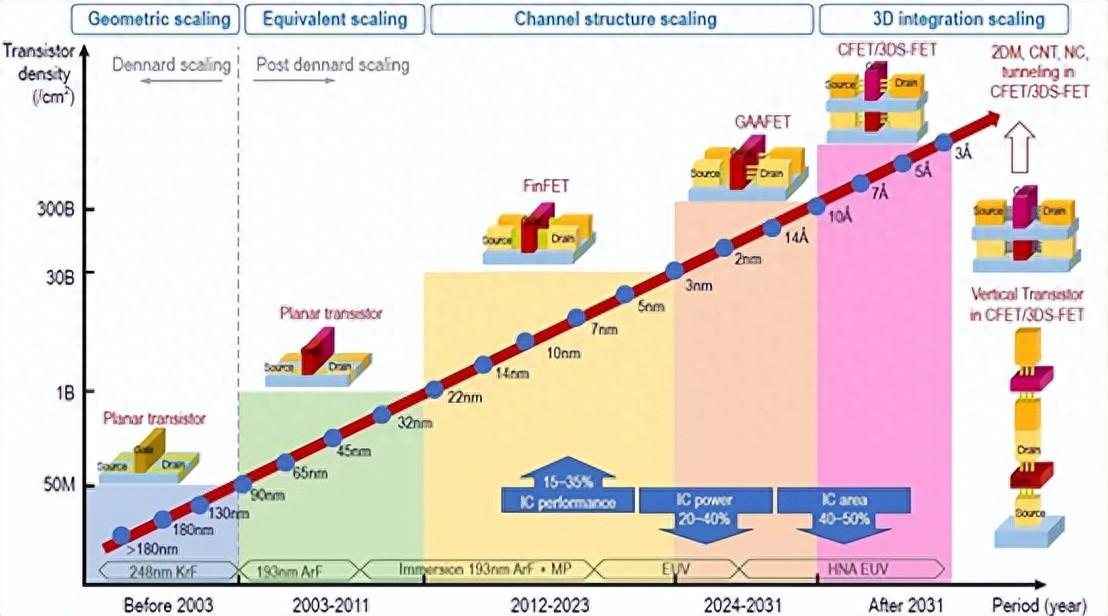

金屬-氧化物-半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)是推動(dòng)大規(guī)模CMOS集成電路按照“摩爾定律”持續(xù)微縮并不斷發(fā)展的核心器件。近十幾年,為突破更小技術(shù)節(jié)點(diǎn)下的微縮挑戰(zhàn),晶體管結(jié)構(gòu)創(chuàng)新成為了技術(shù)發(fā)展的主要路徑,從平面晶體管演進(jìn)到鰭式場(chǎng)效應(yīng)晶體管,再到最新3nm技術(shù)節(jié)點(diǎn)下的堆疊納米溝道全環(huán)繞柵極FET(GAAFET),通過(guò)晶體管內(nèi)部溝道的全三維化以獲得更好的短溝道柵控能力與同尺寸導(dǎo)電性能。在1nm技術(shù)節(jié)點(diǎn)附近,因?yàn)镸OSFET柵控能力無(wú)法進(jìn)一步提升、內(nèi)部Si基導(dǎo)電溝道臨近載流子傳輸量子效應(yīng)限制邊界,傳統(tǒng)摩爾定律所描述的尺寸縮減不再預(yù)期有效,晶體管結(jié)構(gòu)創(chuàng)新將邁入更進(jìn)一步的晶體管垂直三維堆疊。

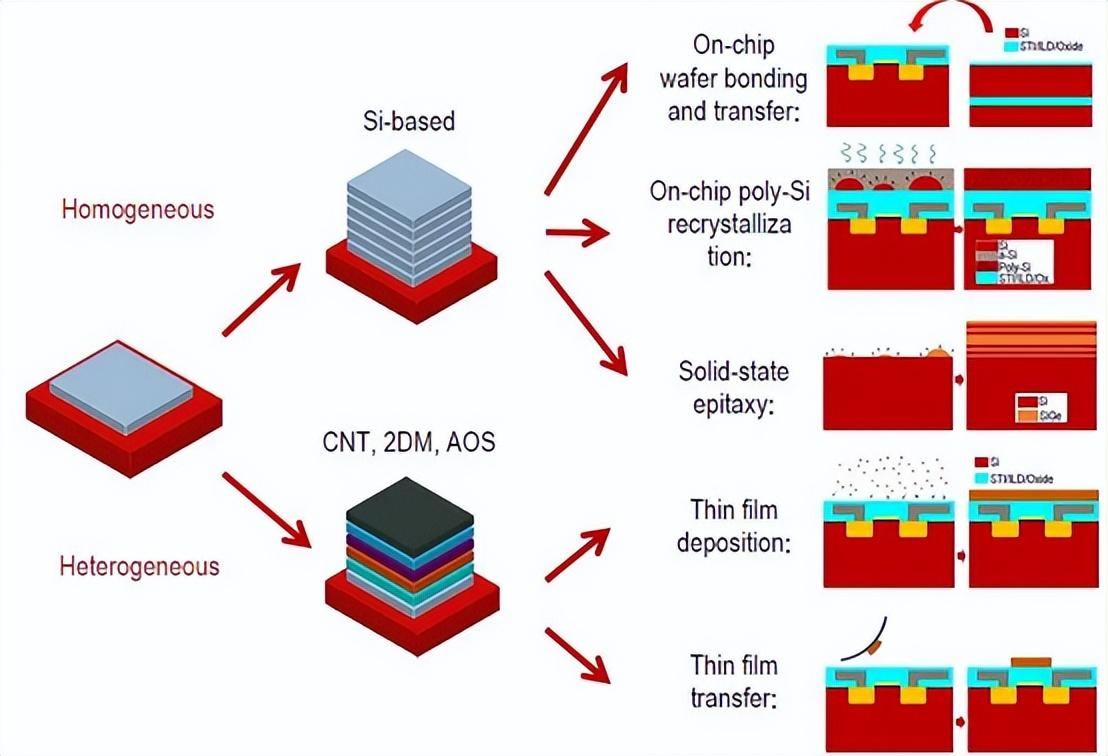

近日,中國(guó)科學(xué)院微電子研究所集成電路先導(dǎo)工藝研發(fā)團(tuán)隊(duì)在中國(guó)科學(xué)雜志社的《國(guó)家科學(xué)評(píng)論》(National Science Review,NSR)在線發(fā)表了關(guān)于先進(jìn)CMOS集成電路新結(jié)構(gòu)晶體管的綜述文章“New structure transistors for advanced technology node CMOS ICs”(《用于集成電路的新興材料和晶體管》專題論文之一),并入選期刊封面論文。該文從最新的GAAFET所面臨的關(guān)鍵技術(shù)挑戰(zhàn)出發(fā),針對(duì)1nm技術(shù)節(jié)點(diǎn)下集成電路持續(xù)發(fā)展的集成密度需求,介紹了實(shí)現(xiàn)晶體管垂直三維堆疊的主要途徑,包括上下垂直互補(bǔ)FET(也稱3D堆疊FET)和垂直溝道晶體管,總結(jié)了實(shí)現(xiàn)晶體管三維堆疊的單次與順次集成路徑和工藝方法、所需的創(chuàng)新工藝、材料(低溫外延硅、碳納米管、二維材料等)以及協(xié)同設(shè)計(jì)技術(shù),分析了面向大規(guī)模集成應(yīng)用的關(guān)鍵工藝、電路設(shè)計(jì)及內(nèi)部散熱挑戰(zhàn),展望了未來(lái)進(jìn)一步與其它新原理晶體管及3D芯片與系統(tǒng)結(jié)合的綜合發(fā)展可能。

中國(guó)科學(xué)院微電子研究所張青竹研究員、張永奎高級(jí)工程師為論文第一作者,殷華湘研究員為論文通訊作者。

全文鏈接:

https://doi.org/10.1093/nsr/nwae008

集成電路中MOSFET持續(xù)創(chuàng)新發(fā)展路徑

晶體管三維堆疊中的不同溝道材料選擇與方法

聲明:本網(wǎng)站部分文章轉(zhuǎn)載自網(wǎng)絡(luò),轉(zhuǎn)發(fā)僅為更大范圍傳播。 轉(zhuǎn)載文章版權(quán)歸原作者所有,如有異議,請(qǐng)聯(lián)系我們修改或刪除。

審核編輯 黃宇

-

晶體管

+關(guān)注

關(guān)注

77文章

9723瀏覽量

138602 -

場(chǎng)效應(yīng)晶體管

+關(guān)注

關(guān)注

6文章

364瀏覽量

19543 -

微電子

+關(guān)注

關(guān)注

18文章

387瀏覽量

41236 -

CMOS集成電路

+關(guān)注

關(guān)注

4文章

41瀏覽量

14272

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

微電子所在超寬帶低噪聲集成電路設(shè)計(jì)領(lǐng)域取得新進(jìn)展

玻色量子亮相2024年《國(guó)家科學(xué)評(píng)論》物理與信息科學(xué)前沿論壇

CMOS晶體管的尺寸規(guī)則

CMOS晶體管和MOSFET晶體管的區(qū)別

CMOS晶體管的工作原理和結(jié)構(gòu)

易華錄榮獲國(guó)家科學(xué)技術(shù)進(jìn)步獎(jiǎng)二等獎(jiǎng)

芯片晶體管的深度和寬度有關(guān)系嗎

PNP晶體管符號(hào)和結(jié)構(gòu) 晶體管測(cè)試儀電路圖

TTL電路和CMOS電路的區(qū)別和聯(lián)系

NMOS、PMOS、CMOS的結(jié)構(gòu)

晶體管的分類與作用

賽微電子收購(gòu)賽萊克斯北京少數(shù)股權(quán),與國(guó)家集成電路股權(quán)無(wú)關(guān)

探秘我國(guó)集成電路科技工作者早期創(chuàng)業(yè)足跡

晶體管和集成電路是什么關(guān)系?

什么是達(dá)林頓晶體管?達(dá)林頓晶體管的基本電路

微電子所在《中國(guó)科學(xué):國(guó)家科學(xué)評(píng)論》發(fā)表關(guān)于先進(jìn)CMOS集成電路新結(jié)構(gòu)晶體管的綜述論文

微電子所在《中國(guó)科學(xué):國(guó)家科學(xué)評(píng)論》發(fā)表關(guān)于先進(jìn)CMOS集成電路新結(jié)構(gòu)晶體管的綜述論文

評(píng)論