電子發燒友網報道(文/周凱揚)隨著EDA市場的競爭加劇,越來越多的供應商開始在工具中引入AI/ML,從而幫助芯片制造商和系統供應商區分其產品。去年是AI EDA工具陸續推出的一年,所以業內對于AI深入設計的做法都持以謹慎態度,但伴隨著AI工具對于改善設計效率的效果逐漸顯現,近一年以來AI驅動EDA工具輔助流片的產品也在不斷增加,這一趨勢也反映到了EDA巨頭的財報表現上。

新思:AI EDA工具成為搶單利器

新思于5月22日發布了今年Q2的財報,其季度營收達到14.55億美元,同比增長15%,非GAAP營業利潤率為37.3%,同比增長約3%。為此,新思再度上調了全年收入和非GAAP每股收益的指引。

在這樣一個人工智能芯片和軟件定義系統普及的時代,新思認為這些技術趨勢推動了研發的系統復雜性,卻也為其帶來了不少機遇。如今其芯片客戶競相設計和制造復雜的專用芯片,而這些客戶已經不再局限于芯片設計公司,還包括不少系統方案公司。

AI工具的快速采用也給新思帶來了前所未有的競爭力,其設計自動化業務營收同比增長14%,得益于整體業務的強勁表現和Synopsys.AI在客戶內的快速采用,包括DSO.ai、ASO.ai等一系列AI套件。比如第二季度,多家亞洲設計服務廠商借助DSO.ai突破了最高頻率目標,而一家領先的美國GPU廠商通過部署DSO.ai提高了生產力等。

新思也提到,在模擬與混合信號設計中,客戶希望借助新思的解決方案盡快實現流程現代化,并遷移到更先進的工藝節點。新思在本季度贏得了10個替代設計,包括一家領先的美國系統方案公司改用了新思的全流程方案,一家領先的亞洲存儲公司為其下一代存儲產品設計改用了新思的模擬設計環境等。在驗證工具上,VSO.ai也得到了30多家客戶的廣泛應用,將周轉時間最高縮短了10倍。

不過,新思對于今年中國市場的業績持謹慎態度,雖然上半年的營收表現不錯,但由于宏觀經濟挑戰和一些限制原因,新思預計今年來自中國市場營收依然會呈現增長的態勢,但占比可能會略低于去年。

Cadence:AI自動化的普及才剛剛開始

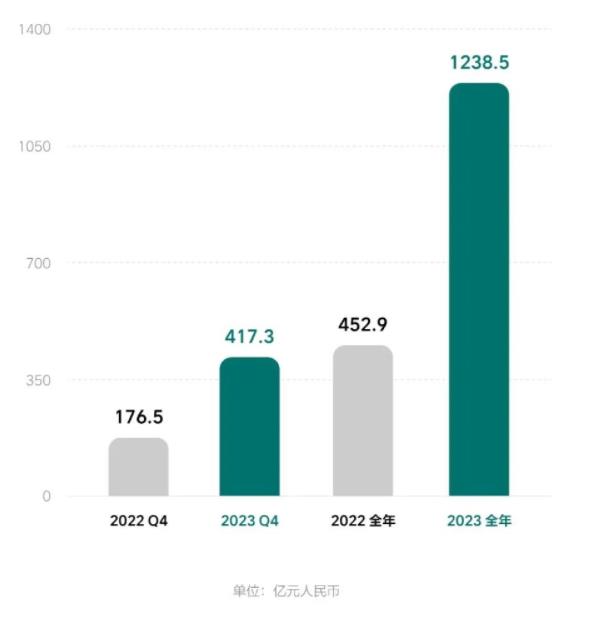

Cadence于4月底發布了今年Q1的財報成績,該季度總營收達到10.09億美元,相較去年同期的10.22億美元幾乎沒有變化。Cadence預計第二季度的營收在10.3億美元至10.5億美元之間,2024財年的總營收在45.6億至46.2億美元之間,高于去年的40.9億美元總營收。之所以能有不俗的Q1表現和全年營收預期,Cadence將其歸功于去年與今年發布的多款新品,以及其AI設計引擎收獲的巨大成功。

在不久前舉辦的CadenceLive大會上,高通公司就表示,他們借助Cadence的Verisium AI驗證平臺,將驗證時間縮短了20倍。而Cadence的另一個大AI工具Cerebrus在數字全流程設計上也得到了廣泛使用,提供一流PPA和效率的同時,已經成為大客戶設計流程以及多個晶圓代工廠新工藝節點DTCO流程中不可或缺一部分,目前已經用于350多個設計項目的流片,同時有50多家客戶在3nm及以上工藝的設計中部署了Cadence的解決方案。

Cadence指出,除了數字設計領域AI的普及之外,未來PCB和封裝領域也會迎來更多的AI自動化,而Cadence的Allegro X AI將成為其中的佼佼者,目前已經在300多家客戶中得到使用。比如英特爾就提到在PCB設計上使用Allegro X AI后,實現了4倍到10倍的效率提升。

西門子:EDA撐起DI業務

相較另外兩家EDA巨頭,西門子的EDA業務被歸為其數字化工業集團,與其他工業自動化、電氣自動化等業務并列。從西門子近期發布的Q2財報來看,其整個數字化工業集團的業務營收為45.05億歐元,同比下滑13%。

這是由于市場環境挑戰較大,客戶庫存較高,自動化業務訂單量整體下降造成的,尤其是在中國市場。其軟件業務卻從去年Q2的11.65億歐元增長至13.66億歐元,訂單數量也有兩位數的增長。西門子表示這主要是由EDA業務增長驅動的,得益于美國地區的半導體客戶高漲的EDA需求,西門子在EDA業務上實現了50%以上的營收增長。對于今年下半年的預期,西門子表示在軟件業務上將迎來更加強勁的客戶活動,且集中在EDA和授權業務上。

目前西門子已經將不少AI功能導入其EDA工具中,比如Solido DE,就是一個全面由AI驅動的SPICE級設計環境,集成了AI和云部署技術。Solido DE可以借助AI來幫助用戶確定優化途徑,改進電路PPA并提供良率分析,比傳統的蒙特卡羅分析法要快上幾個數量級。

目前不少大客戶已經引入了西門子的AI EDA工具,比如SK海力士。為了進一步提高驗證精度和周轉時間,SK海力士已經在下一代存儲器技術的設計中用到了Solido DE,并大幅縮短了從初始設計到生產所需的時間。除此之外還有Forza Silicon這一CMOS圖像傳感器廠商,也將Solido DE作為其仿真環境,為機器視覺、汽車、XR等應用設計高分辨高速CMOS圖像傳感器。

近日,西門子發布了全新的Catapult AI NN軟件,用于ASIC和SoC上神經網絡加速器的高級綜合,可以將AI框架中的神經網絡描述轉換成C++,并綜合成Verilo或VHDL,用于ASIC、FPGA或SoC上的實現。這樣可以使得AI開發人員在軟件開發的過程中,在芯片設計上獲取最佳的PPA表現。

寫在最后

相較EDA巨頭,國產EDA廠商對于AI的導入進度則略顯落后。雖然這并不影響其在設計活動頻繁的去年和今年營收快速增長,但同樣快速增長的研發投入也在進一步壓縮其利潤空間。而目前主流芯片設計廠商已經將AI EDA工具引入了最先進芯片的設計流程中,并在PPA和設計效率上展現了前所未有的優勢。相信這也是國內EDA廠商在全力打造全流程工具的同時,加大在AI引擎上研發投入的原因。

-

eda

+關注

關注

71文章

2764瀏覽量

173330 -

AI芯片

+關注

關注

17文章

1887瀏覽量

35053

發布評論請先 登錄

相關推薦

世界先進9月營收大幅增長34%

臺積電8月營收大增33%,AI芯片需求強勁

韓企存儲芯片在華熱銷,營收翻倍增長

2024年全球半導體營收預計迎來20%增長

阿里巴巴季報出爐 阿里云二季度營收增長6%

世芯聚焦HPC、AI領域,預計營收持續增長

高溫來勢洶洶,光伏電站如何應對

AI芯片設計來勢洶洶,EDA巨頭營收順勢增長

AI芯片設計來勢洶洶,EDA巨頭營收順勢增長

評論