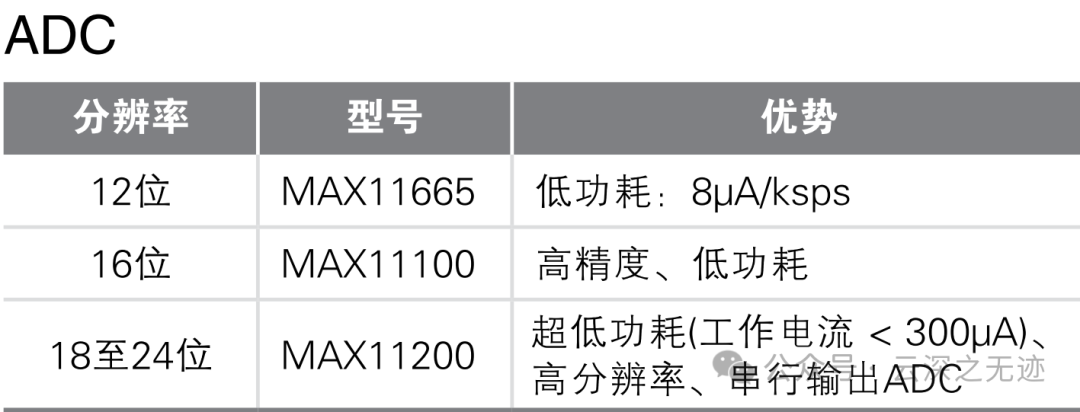

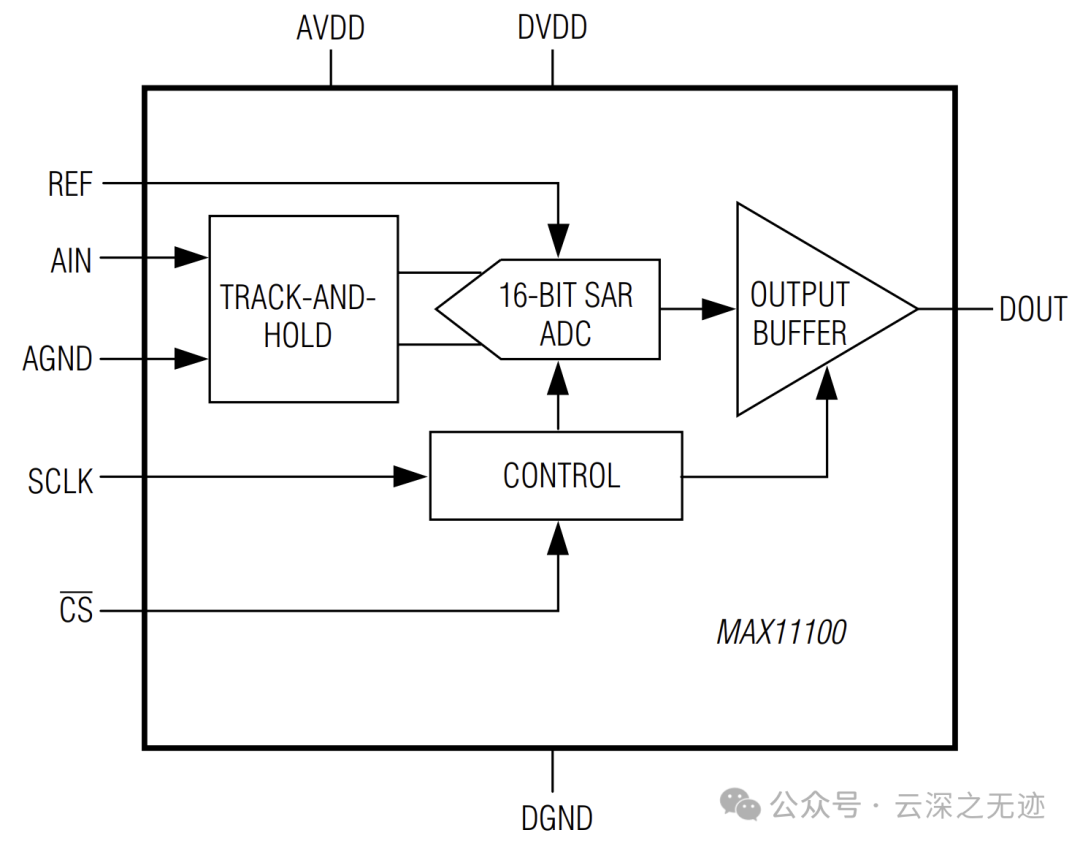

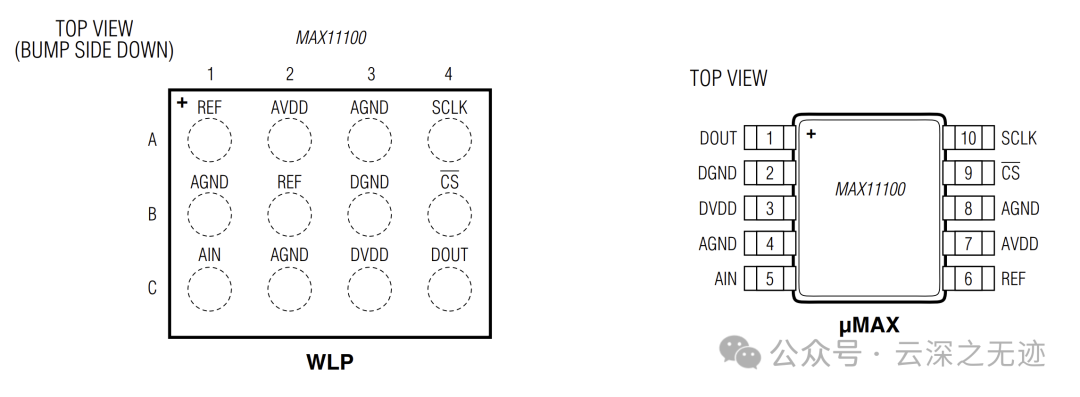

今天看了一個ADI的產品冊,關于精密信號鏈的,發現了一個特別小的ADC。

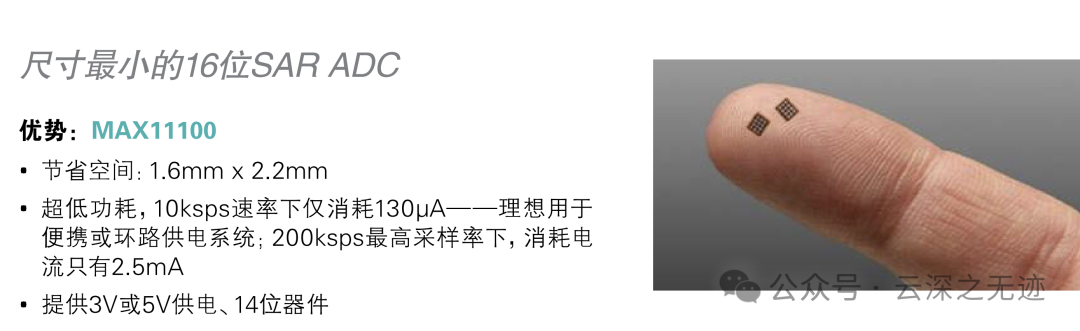

除了小以外,就是使用簡單,數據手冊里面就有關斷和普通采集兩個模式。

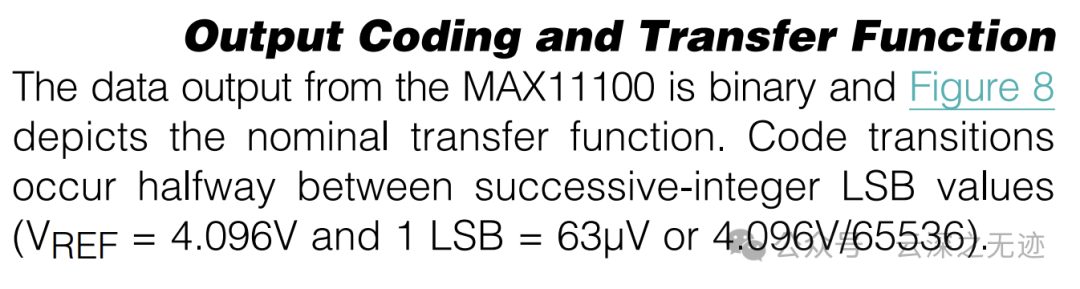

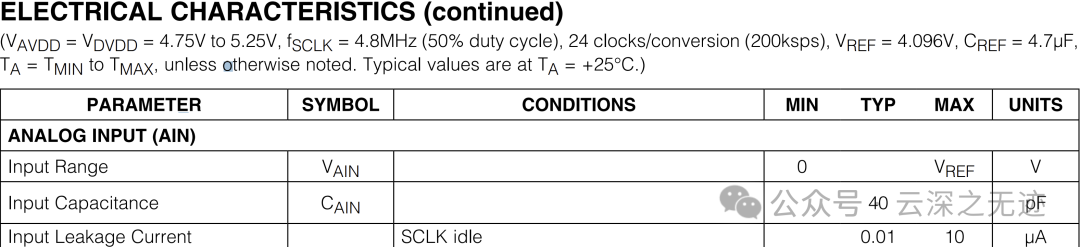

16bit,在典型的環境下可以采樣63uV的信號,普通的夠用

沒有負電壓,不支持差分功能

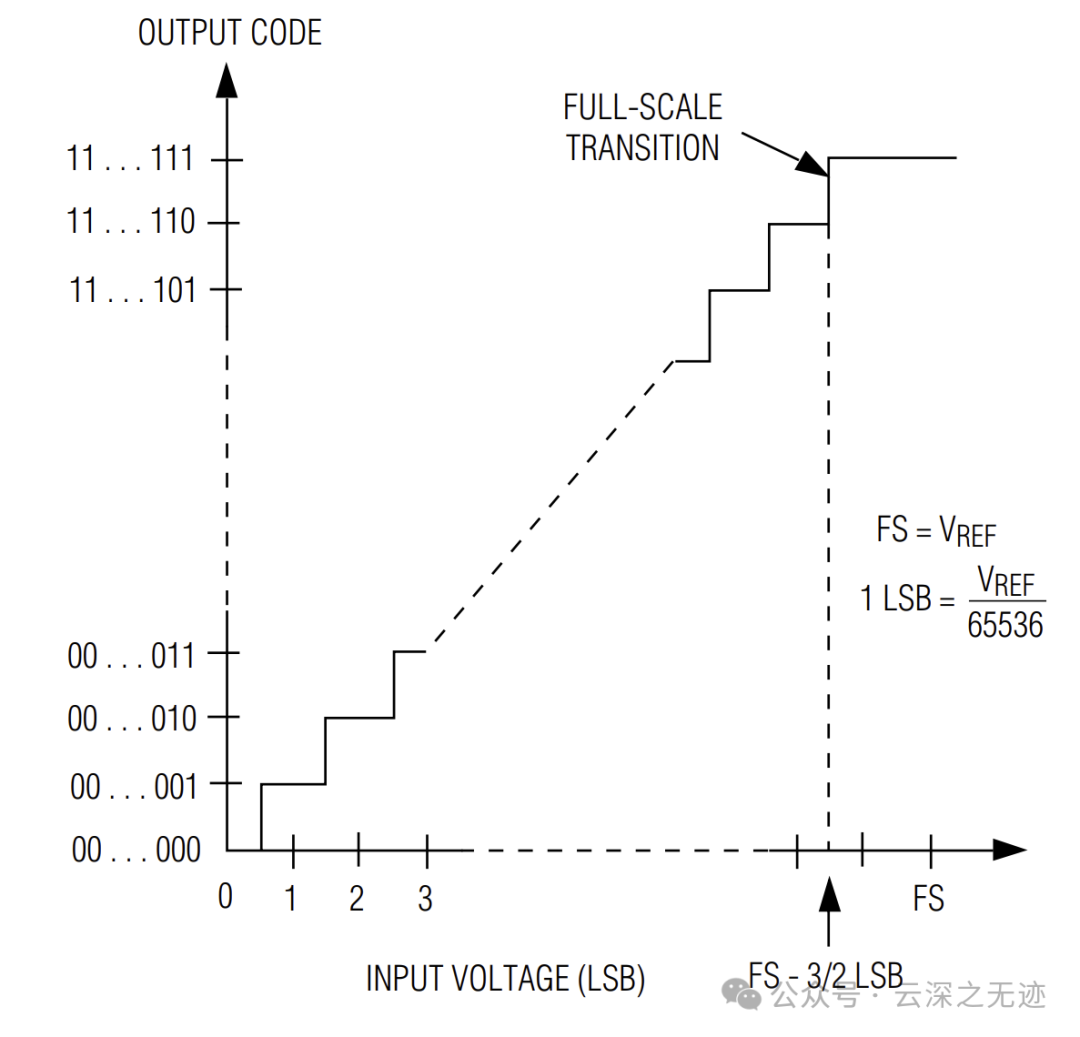

要想達到16bit的精度,還得加緩沖器,又加了多余的器件,emmm

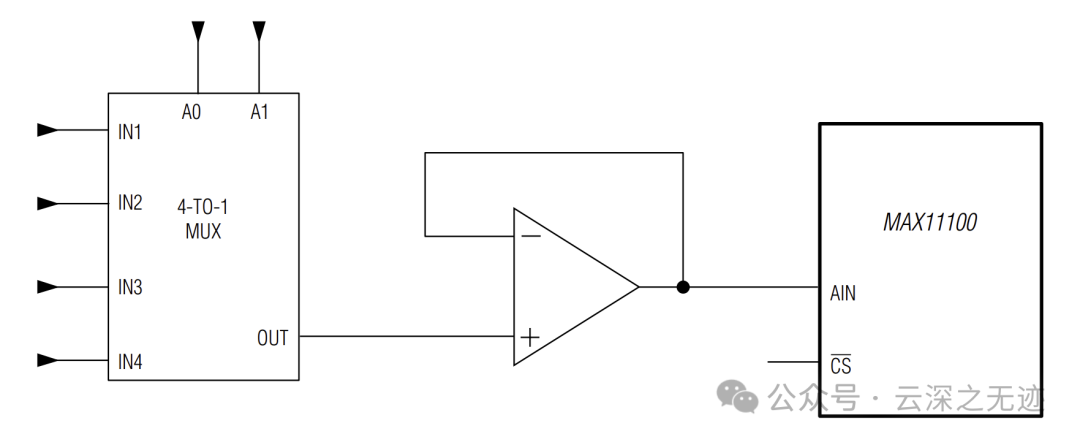

典型傳感器應用涉及到傳感器參數的監測和執行器的控制。傳感器信號鏈(如下圖所示)由模擬域和數字域組成。典型傳感器輸出的是幅度很小的模擬信號。

這些弱模擬信號使用運放、模數轉換器或壓頻轉換器進行放大和濾波,并轉換為數 字值,然后在MCU中進行處理。模擬傳感器輸出通常需要先進 行適當的信號調理,然后再轉換為數字信號。

MCU會根據信號檢測條件來控制執行器和維持傳感器信號調理電路的操作。在數模反饋路徑中,最常用的是數模轉換器(DAC)、數字電位器和脈寬調制器(PWM)等器件。

MOSFET驅動器常用作反饋電路和執行器(如電機和閥門)之間的接口。

這個圖是信號鏈的全景,通過ADC感知現實何DAC干預現實展開

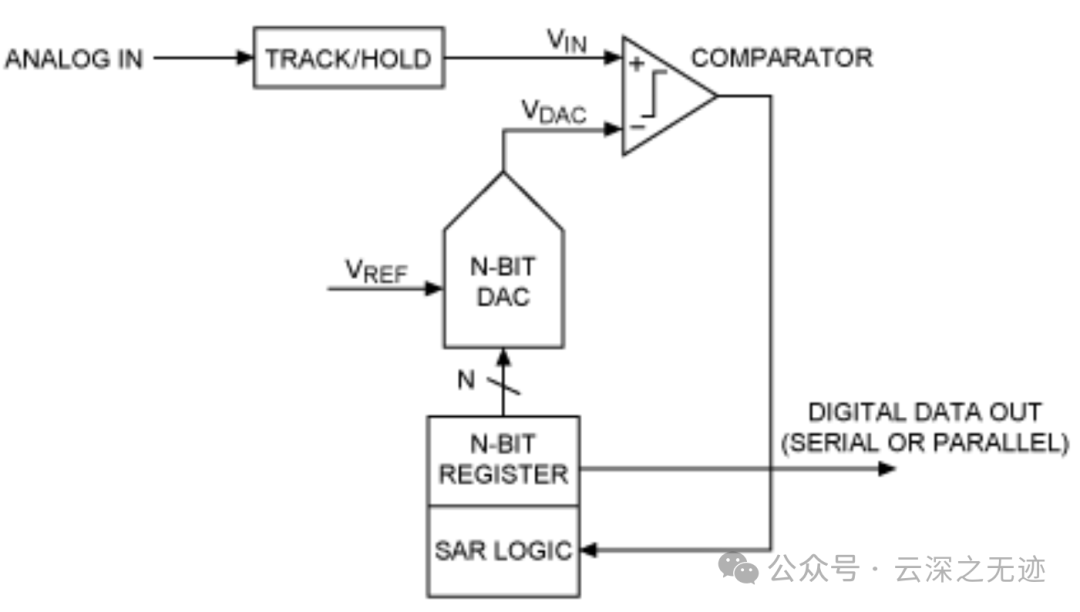

逐次逼近寄存器型(SAR)模數轉換器(ADC)占據著大部分的中等至高分辨率ADC市場。SAR ADC的采樣速率最高可達5Msps,分辨率為8位至18位。SAR架構允許高性能、低功耗ADC采用小尺寸封裝,適合對尺寸要求嚴格的系統。

逐次逼近寄存器型(SAR)模擬數字轉換器(ADC)是采樣速率低于5Msps (每秒百萬次采樣)的中等至高分辨率應用的常見結構。這個話雖然和上面比差不多,但是

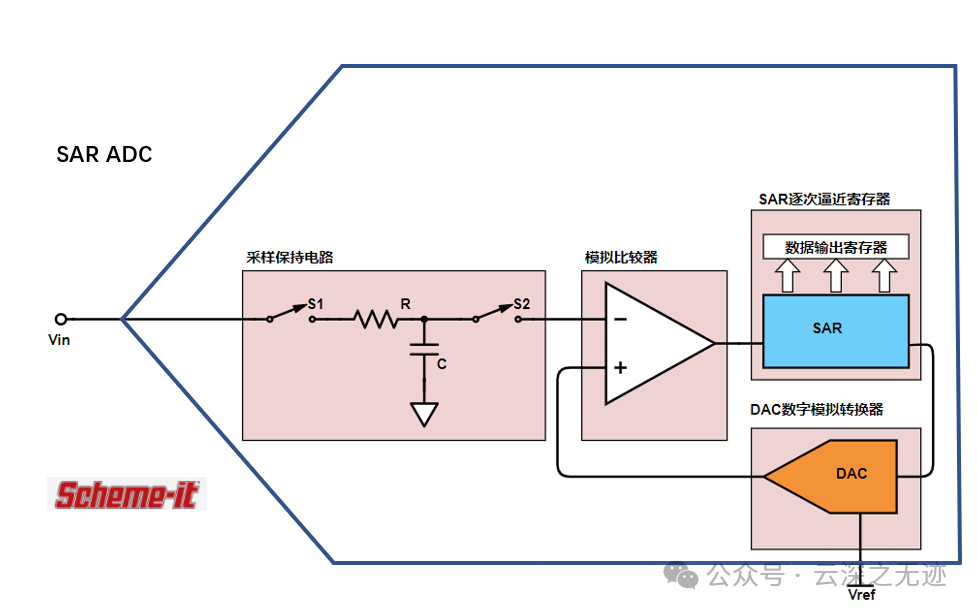

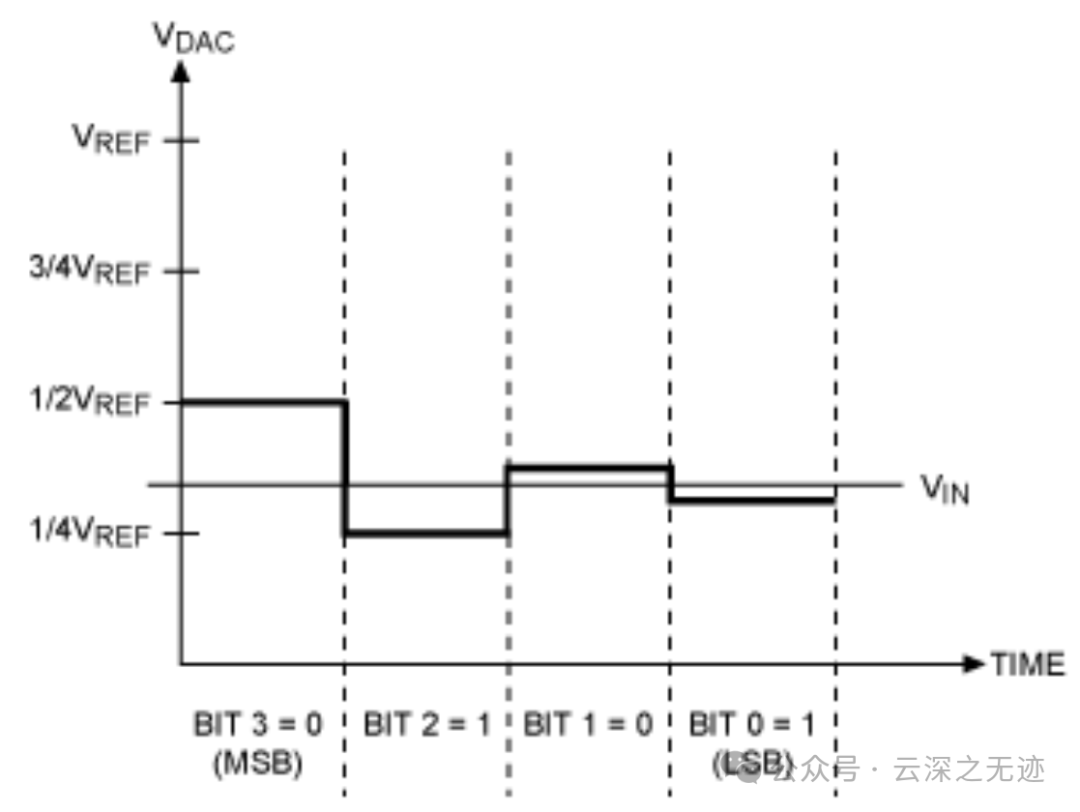

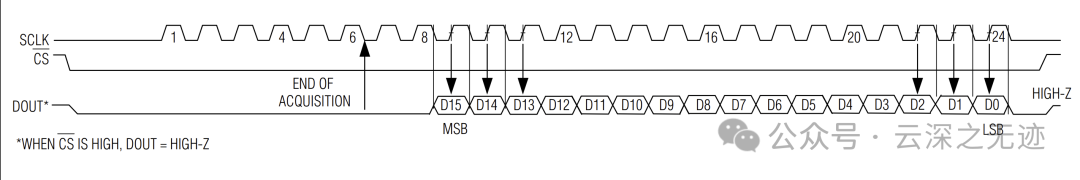

模擬輸入電壓(VIN)由采樣/保持電路保持。

為實現二進制搜索算法,N位寄存器首先設置在中間刻度(即:100... .00,MSB設置為1)。

這樣,DAC輸出(VDAC)被設為VREF/2,VREF是提供給ADC的基準電壓。然后,比較判斷VIN是小于還是大于VDAC。如果VIN大于VDAC,則比較器輸出邏輯高電平或1,N位寄存器的MSB保持為1。

相反,如果VIN小于VDAC,則比較器輸出邏輯低電平,N位寄存器的MSB清0。隨后,SAR控制邏輯移至下一位,并將該位設置為高電平,進行下一次比較。這個過程一直持續到LSB。上述操作結束后,也就完成了轉換,N位轉換結果儲存在寄存器內。

大概就是這樣

放個彩圖

給出了一個4位轉換示例,y軸(和圖中的粗線)表示DAC的輸出電壓。

本例中,第一次比較表明VIN< VDAC。

所以,位3置為0。

然后DAC被置為01002,并執行第二次比較。

由于VIN> VDAC,位2保持為1。DAC置為01102,執行第三次比較。

根據比較結果,位1置0,DAC又設置為01012,執行最后一次比較。

最后,由于VIN> VDAC,位0確定為1。

那么這個值就會被慢慢的比較出來。

這個就是不停的比大小

對于4位ADC需要四個比較周期。

通常,N位SAR ADC需要N個比較周期,在前一位轉換完成之前不得進入下一次轉換。

由此可以看出,該類ADC能夠有效降低功耗和空間,當然,也正是由于這個原因,分辨率在14位至16位,速率高于幾Msps (每秒百萬次采樣)的逐次逼近ADC極其少見。

SAR ADC的另一個顯著的特點是:功耗隨采樣速率而改變。這一點與閃速ADC或流水線ADC不同,后者在不同的采樣速率下具有固定的功耗。這種可變功耗特性對于低功耗應用或者不需要連續采集數據的應用非常有利

SAR結構的主要局限是采樣速率較低,并且其中的各個單元(如DAC和比較器),需要達到與整體系統相當的精度。ADI的文檔給了各個單元的細節,我就不放了,那就抄的太多了。

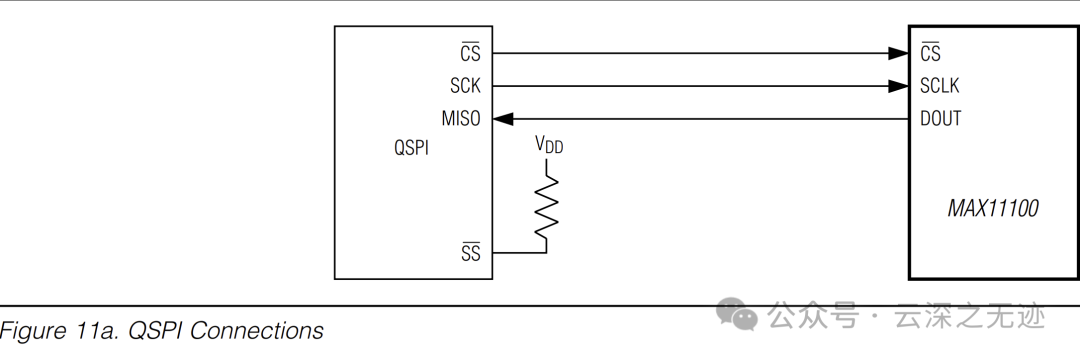

QSPI,這連接也不對啊

時序也沒有上面不一樣

應該這個QSPI就是快一些,沒有很多的資料了,這里MCU是PIC的,感覺國外的MicroChip好流行啊!

說說布線:

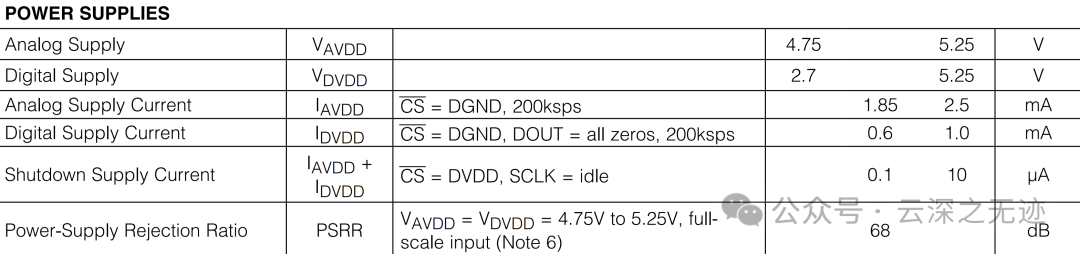

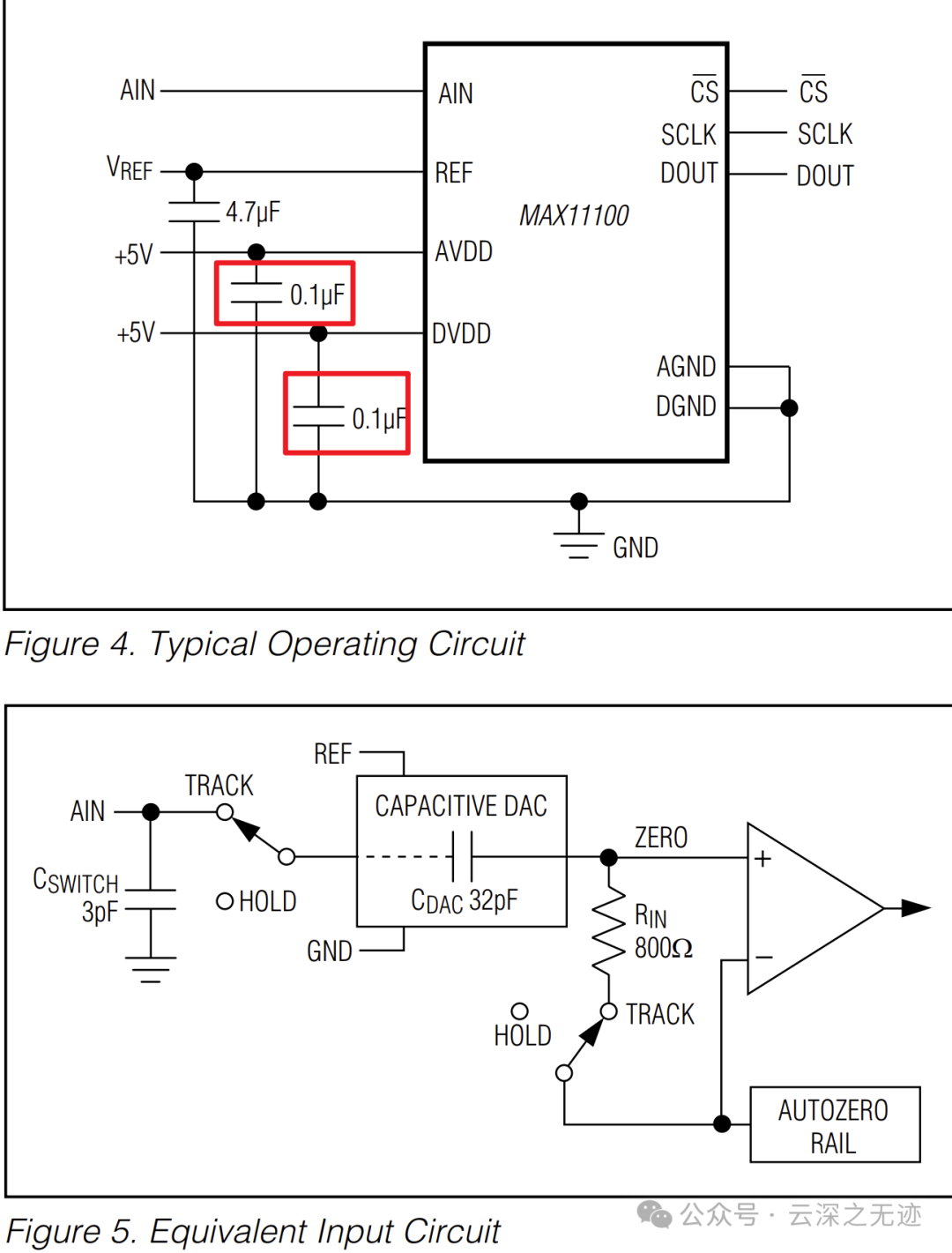

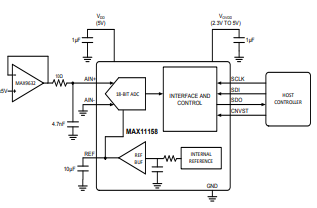

電源,布局,接地和旁路使用pcb與單獨的模擬和數字接地平面。

不要使用單面板 在MAX11100上連接兩個接地平面。當模擬電源和數字電源來自同一源時,用低值電阻(10Ω)或鐵氧體磁頭將數字電源與模擬電源隔離。

供電、輸入順序的約束如下:AGND優先于DGND。

在AVDD和AGND存在后應用AIN和REF。

DVDD與電源順序無關。

確保數字返回電流不通過模擬地,并且返回電流路徑是低阻抗的。

當5mA電流流過PCB接地走線阻抗僅為0.05Ω時,產生的誤差電壓約為250μV,在+4V滿量程系統中產生的誤差為4lsb。電路板布局應確保數字和模擬信號線保持分開。不要讓模擬和數字(尤其是SCLK和DOUT)線彼此平行運行。因為在空間中會互相耦合。 如果一個必須與另一個相交,就以直角相交,指線。ADC高速比較器對AVDD電源的高頻噪聲敏感。用一個0.1μF的電容和一個1μF到10μF的低esr電容并聯,旁路一個噪聲過大的電源到模擬地平面。保持電容引線短,以獲得最佳的電源噪聲抑制。

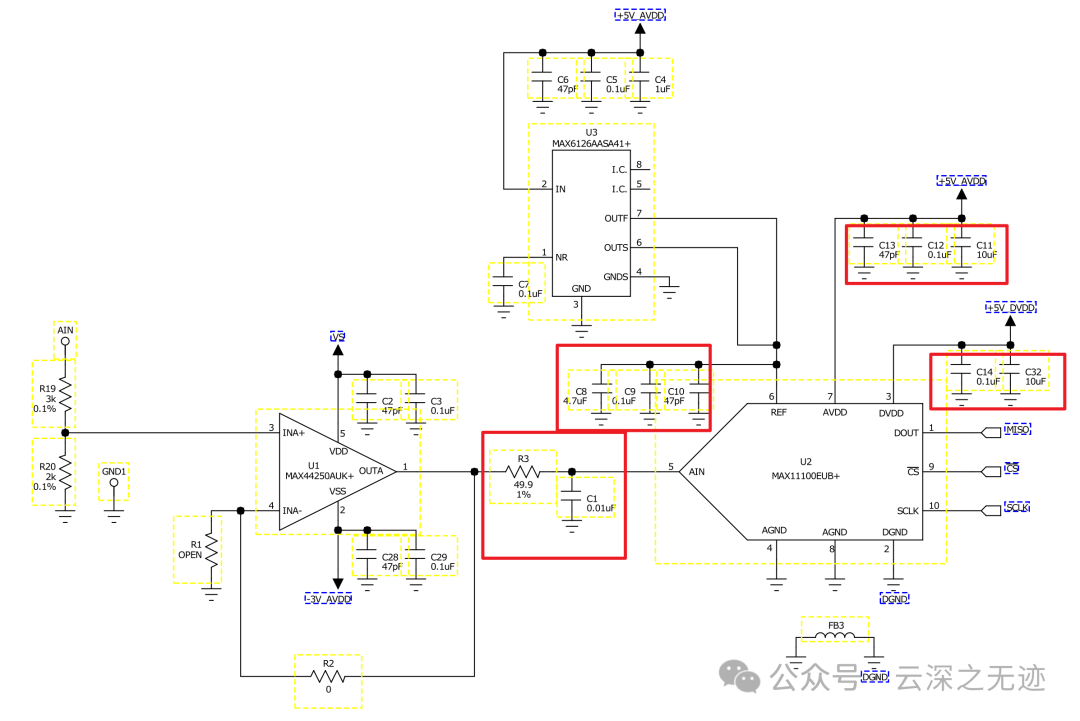

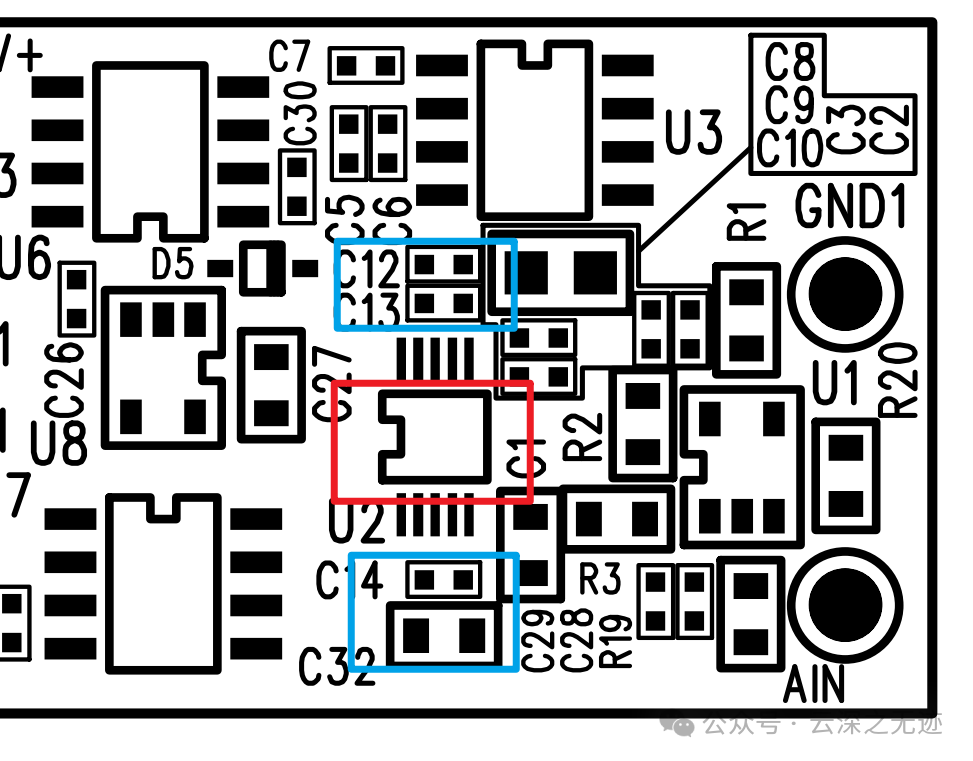

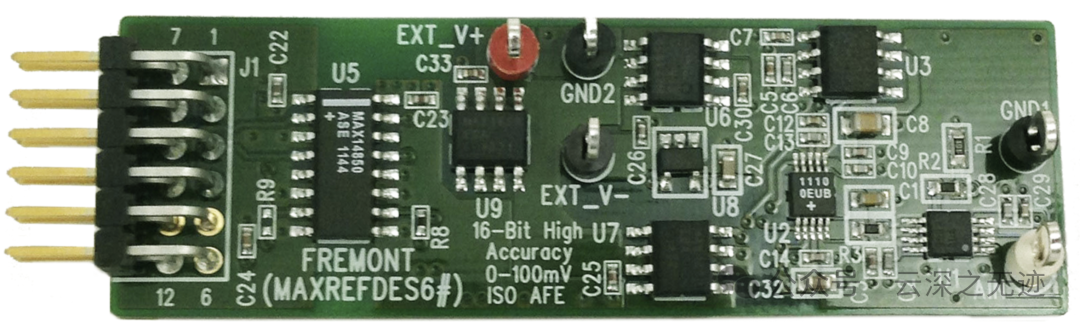

看實際是加了很多的濾波電容,輸入端還有濾波器,也可以調整輸入的時間。

都是大量的電容

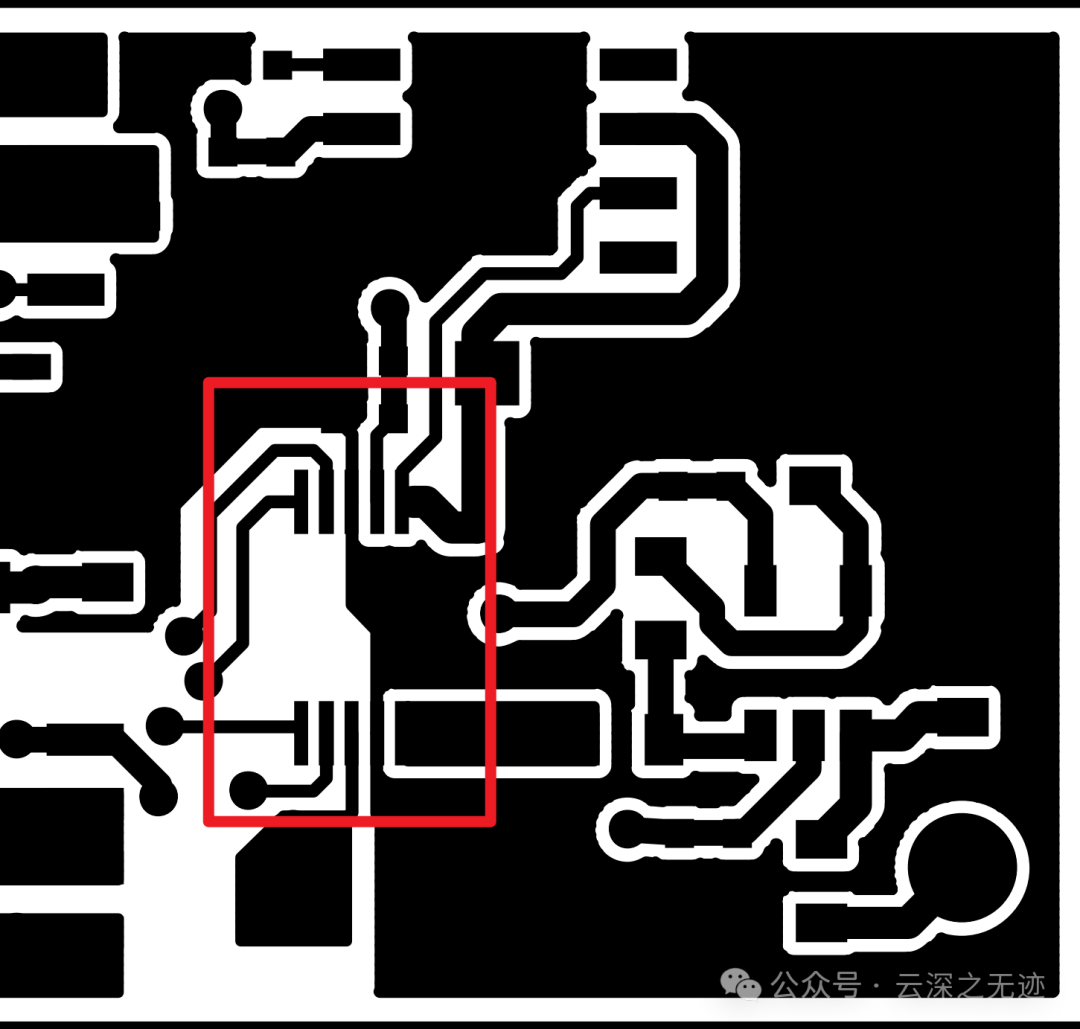

可以看到走線走的很順,證明布局好

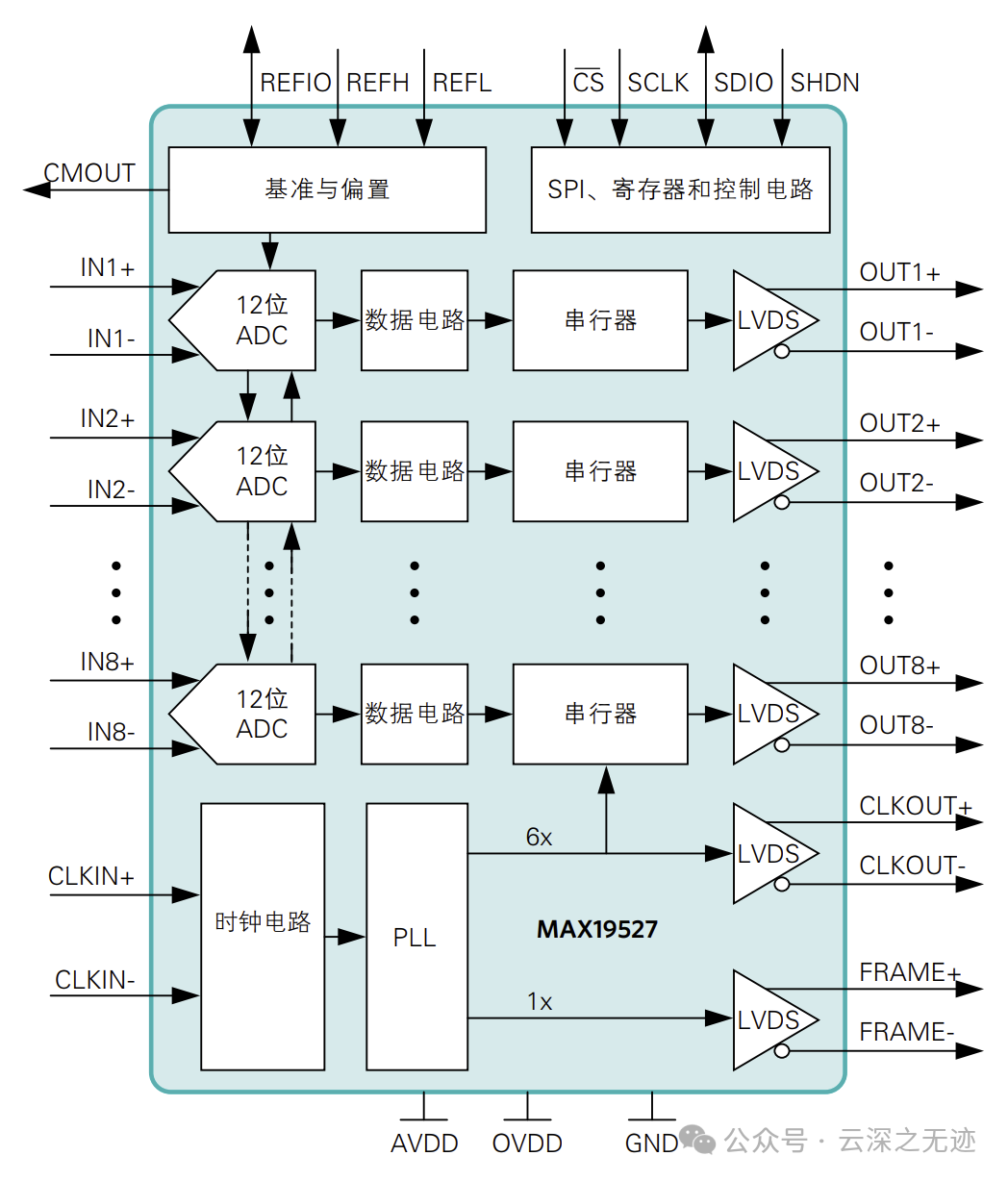

這個是一個高級的ADC,輸出的是LVDS

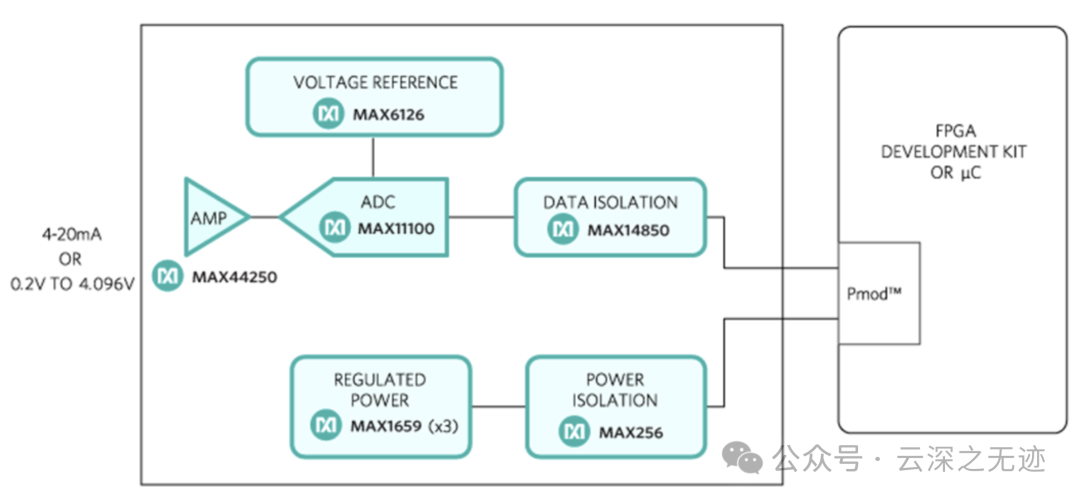

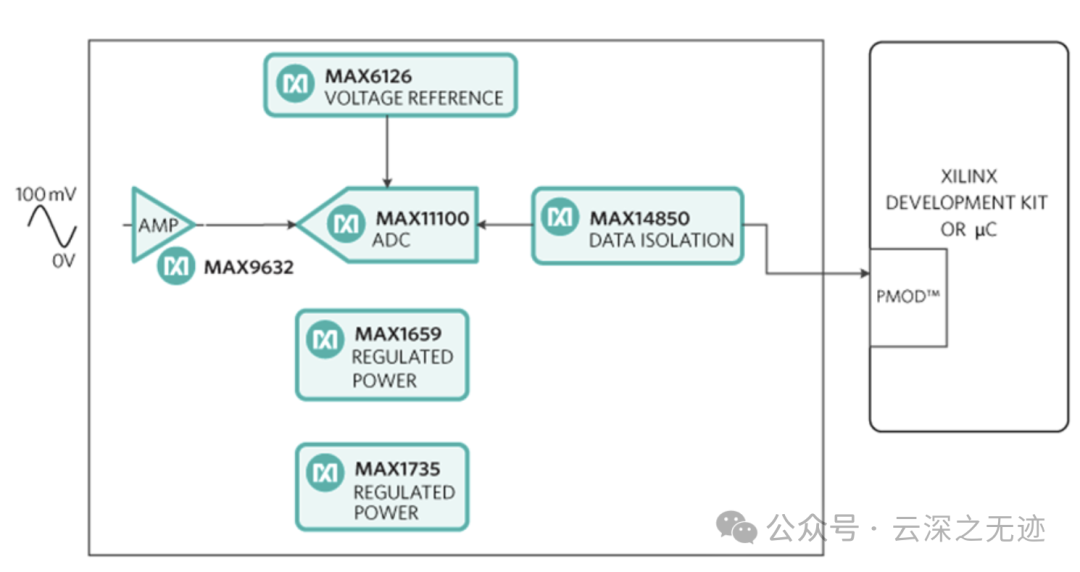

給出了三個設計:

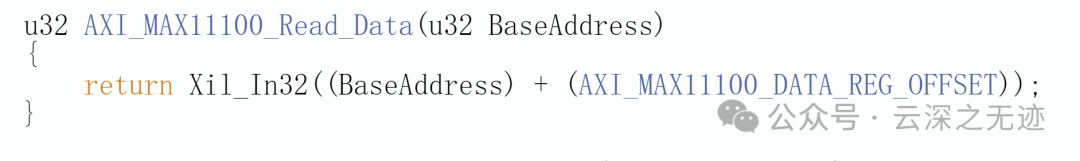

具體的看官網,給的是FPGA上面軟核的C代碼,很抽象。

真的很怪,有什么值得使用FPGA的

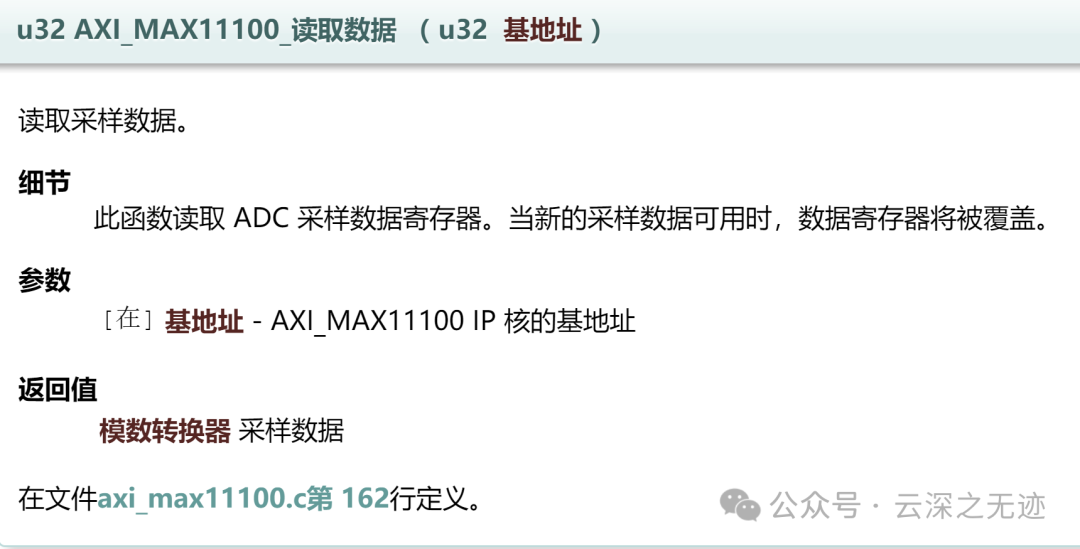

讀取函數

實現,好家伙兒,直接在內存里面撈,牛逼牛逼

單次采樣的C代碼

總之我不理解

哪里好?我買不起是真的

審核編輯:彭菁

-

寄存器

+關注

關注

31文章

5394瀏覽量

122345 -

SAR

+關注

關注

3文章

421瀏覽量

46507 -

adc

+關注

關注

99文章

6594瀏覽量

547348 -

模數轉換器

+關注

關注

26文章

3254瀏覽量

127576

原文標題:尺寸最小的16位SAR ADC-ADI-MAX11100

文章出處:【微信號:TT1827652464,微信公眾號:云深之無跡】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Maxim推出尺寸最小雙極性ADC MAX11166和MAX11167

美信推出業內尺寸最小的18位逐次逼近型ADC MAX11156

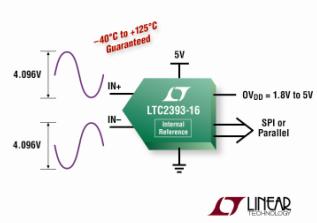

Linear推出16 位 SAR ADC LTC2393-1

Linear推出16位SAR ADC LTC2393-16

MAX11100 業內尺寸最小的16位ADC

MAX11100 ,pdf(16-Bit, +5V, 200ksps ADC)

MAX11166業內尺寸最小的16位ADC,支持±5V雙極性性輸入

16位SAR ADC MAX11168的關鍵特性和應用

UG-1615:4通道、4 MSPS、16位/14位/12位、雙同步采樣SAR ADC

評論