微控制器、現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)、數(shù)字信號(hào)處理器(DSP)、模數(shù)轉(zhuǎn)換器(ADC)以及以多個(gè)電壓軌供電的其他器件都需要電源時(shí)序控制。這些應(yīng)用通常要求,內(nèi)核和模擬模塊在數(shù)字輸入/輸出(I/O)軌之前上電,不過(guò)有些設(shè)計(jì)可能要求采用其他序列。正確的上電和關(guān)斷時(shí)序控制可以防止閂鎖引起的即刻損壞和靜電放電(ESD)引起的長(zhǎng)期損壞。另外,對(duì)電源實(shí)施時(shí)序控制還可在上電期間錯(cuò)開(kāi)浪涌電流,在采用限流電源供電的應(yīng)用中,這一特性特別有用。

本應(yīng)用筆記探討采用分立式元件對(duì)電源進(jìn)行時(shí)序控制的優(yōu)缺點(diǎn),同時(shí)還將描述利用ADP5134,的內(nèi)部精密使能引腳實(shí)現(xiàn)時(shí)序控制的一種簡(jiǎn)單而有效的方法。ADP5134將2個(gè)1.2A降壓調(diào)節(jié)器與2個(gè)300mA低壓差(LDO)調(diào)節(jié)器結(jié)合起來(lái)。本應(yīng)用筆記同時(shí)還將描述一些序列器IC,它們可能對(duì)要求更為精確和靈活的時(shí)序控制這類應(yīng)用更有幫助。

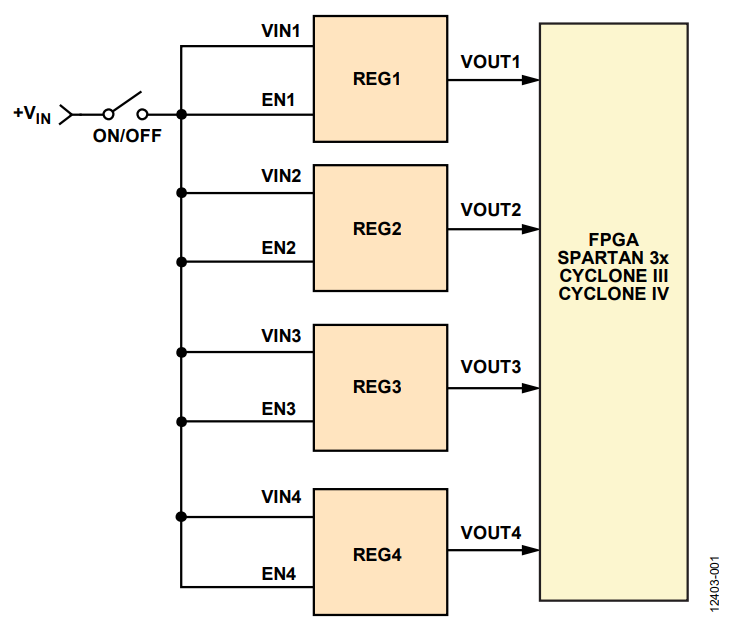

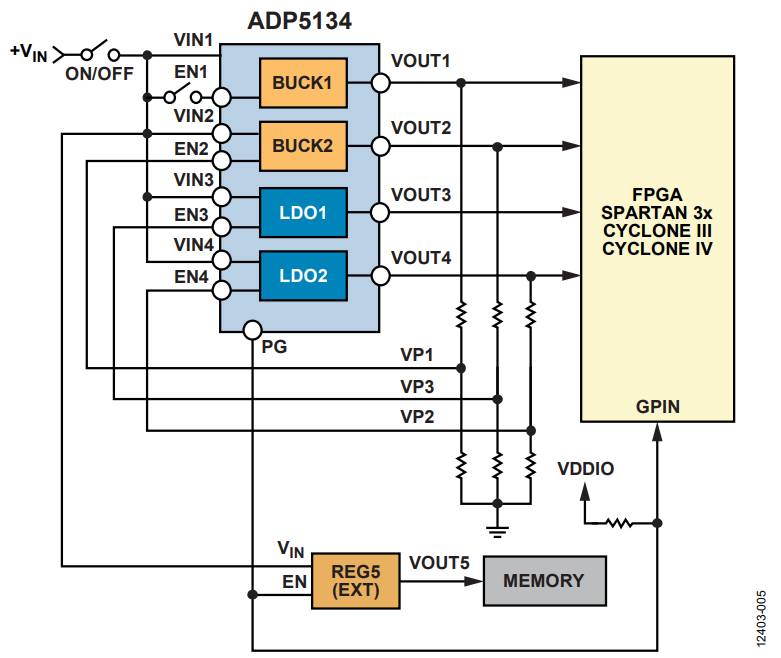

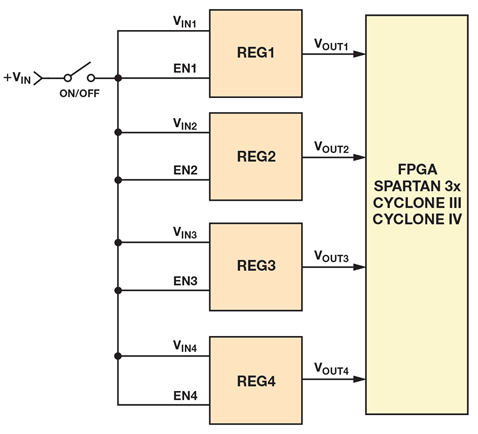

圖1所示的應(yīng)用要求使用多個(gè)供電軌。這些供電軌分別為內(nèi)核電源(VCCINT)、I/O電源(VCCO)、輔助電源(VCCAUX)和系統(tǒng)存儲(chǔ)器電源。

圖1.處理器和FPGA的典型供電方法

例如,XilinxSpartan-3A FPGA集成了上電復(fù)位電路,該電路確保在所有電源均達(dá)到閾值之后,才允許對(duì)器件進(jìn)行配置。上電復(fù)位電路降低了對(duì)電源時(shí)序控制的嚴(yán)格要求;但是,為了盡量降低浪涌電流水平,同時(shí)考慮連接到FPGA的電路的時(shí)序控制要求,必須按以下序列給供電軌上電:先是VCCINT,然后是VCCAUX最后是VCCO。請(qǐng)注意,有些應(yīng)用要求遵循特定序列;因此,請(qǐng)務(wù)必參看相關(guān)數(shù)據(jù)手冊(cè)電源要求部分。

利用無(wú)源延遲網(wǎng)絡(luò)實(shí)現(xiàn)簡(jiǎn)單的電源時(shí)序控制

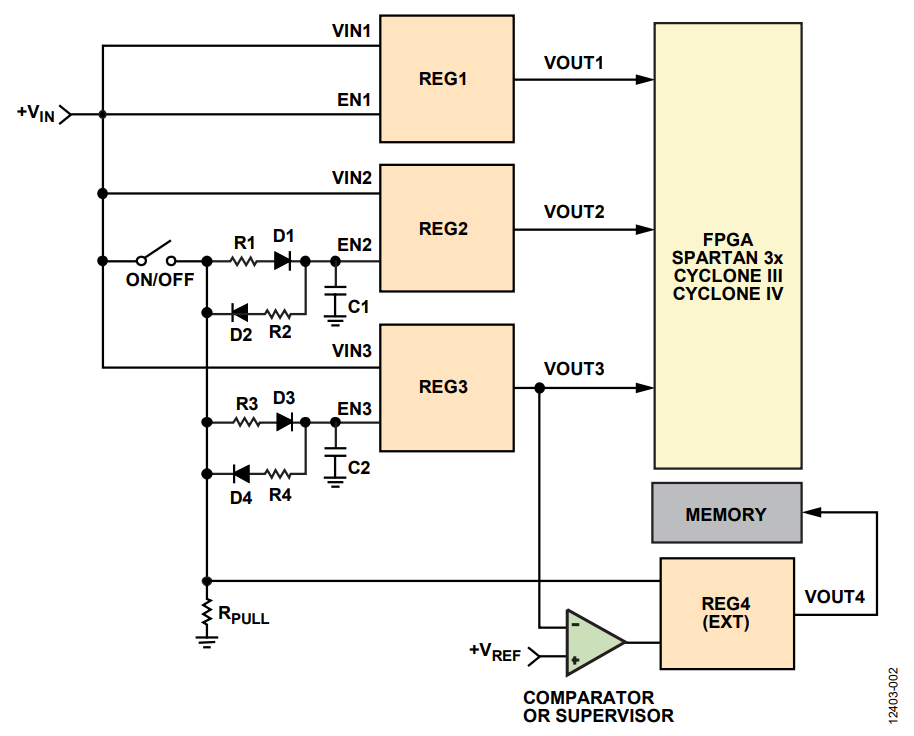

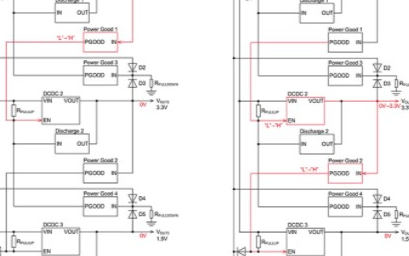

對(duì)電源實(shí)施時(shí)序控制的一種簡(jiǎn)單辦法是用無(wú)源元件延遲進(jìn)入調(diào)節(jié)器使能引腳的信號(hào),此類無(wú)源元件包括電阻、電容、二極管等,如圖2所示。當(dāng)開(kāi)關(guān)閉合時(shí),D1導(dǎo)通,D2斷開(kāi)。C1充電,EN2的電壓以取決于R1和C1的速率上升。當(dāng)開(kāi)關(guān)斷開(kāi)時(shí),C1通過(guò)R2、D2和RPULL放電至地。EN2的電壓以取決于R2、RPULL和C1的速率下降。改變R1和R2的值,將改變充電和放電時(shí)間,從而設(shè)定調(diào)節(jié)器的開(kāi)啟和關(guān)閉時(shí)間。

圖2.利用電阻、電容和二極管實(shí)現(xiàn)的簡(jiǎn)單電源時(shí)序控制方法

這種方法可以用于不要求進(jìn)行精密時(shí)序控制的應(yīng)用。只需延遲信號(hào)的應(yīng)用可能只需要外部電阻和電容。在標(biāo)準(zhǔn)調(diào)節(jié)器中使用這種方法的劣勢(shì)在于,使能引腳的邏輯閾值可能隨電壓和溫度而大幅變化。另外,電壓斜坡中的延遲取決于電阻和電容的值和容差。在–55°C至+85°C的溫度范圍內(nèi),典型X5R電容的變化幅度約為±15%,而受直流偏置效應(yīng)影響,變化幅度還會(huì)增加±10%,這個(gè)偏差會(huì)使時(shí)序失去準(zhǔn)確性,有時(shí)還會(huì)變得不可靠。

精密使能引腳簡(jiǎn)化時(shí)序控制

為了實(shí)現(xiàn)精密時(shí)序控制所需的穩(wěn)定閾值水平,多數(shù)調(diào)節(jié)器要求采用一個(gè)外部基準(zhǔn)電壓源。ADP5134通過(guò)集成一個(gè)精密基準(zhǔn)電壓源克服了這個(gè)問(wèn)題,同時(shí)還可大幅節(jié)省成本和減少印刷電路板(PCB)面積。每個(gè)調(diào)節(jié)器都有一個(gè)單獨(dú)的使能輸入引腳。

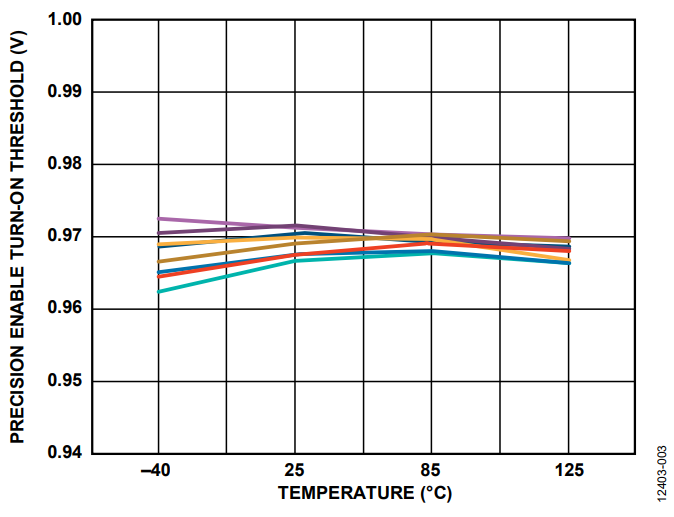

當(dāng)使能輸入引腳的電壓升至ENx引腳上升閾值(VIH_EN[0.9V最小值])以上時(shí),器件退出關(guān)斷模式,管理模塊開(kāi)啟,但不會(huì)激活調(diào)節(jié)器。器件將使能輸入引腳的電壓與一個(gè)精密內(nèi)部基準(zhǔn)電壓(典型值為0.97V)進(jìn)行比較。當(dāng)使能引腳的電壓升至精密使能閾值以上時(shí),調(diào)節(jié)器激活,輸出電壓開(kāi)始上升。在輸入電壓和溫度轉(zhuǎn)折點(diǎn),基準(zhǔn)電壓源變化幅度只有±3%。這么小的變化范圍確保了時(shí)序控制的精確性,解決了使用分立式元件時(shí)存在的問(wèn)題。

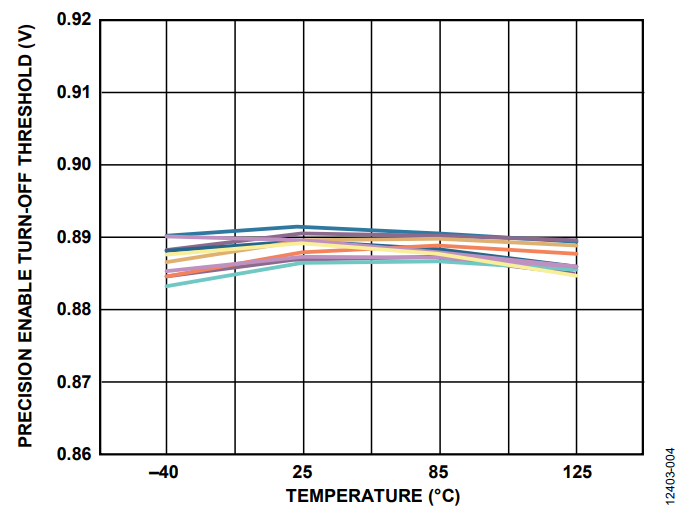

當(dāng)使能輸入引腳的電壓下降到比基準(zhǔn)電壓低80mV(典型值)時(shí),調(diào)節(jié)器停用。當(dāng)所有使能輸入引腳的電壓都降至ENx下降閾值(VIL_EN[0.35V最大值])以下時(shí),器件進(jìn)入關(guān)斷模式。在該模式下,功耗降至1μA以下。圖3和圖4展示了ADP5134精密使能閾值在整個(gè)溫度范圍內(nèi)針對(duì)BUCK1的精度。

圖3.整個(gè)溫度范圍內(nèi)的精密使能開(kāi)啟閾值(10個(gè)樣本)

圖4.整個(gè)溫度范圍內(nèi)的精密使能關(guān)閉閾值(10個(gè)樣本)

利用分阻器實(shí)現(xiàn)簡(jiǎn)單的電源時(shí)序控制

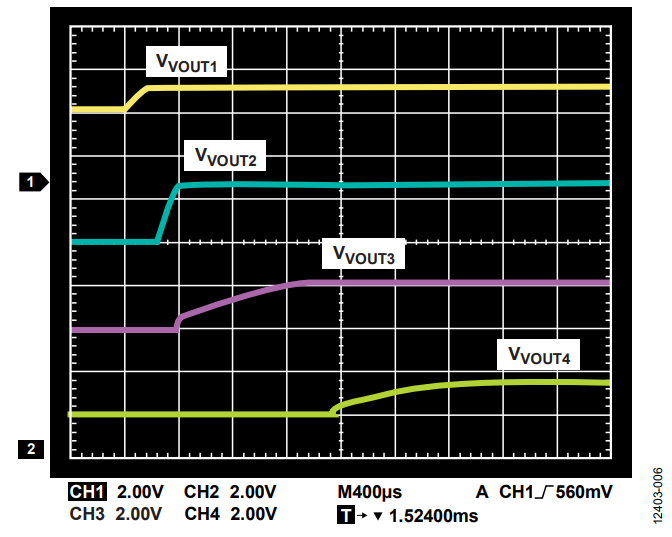

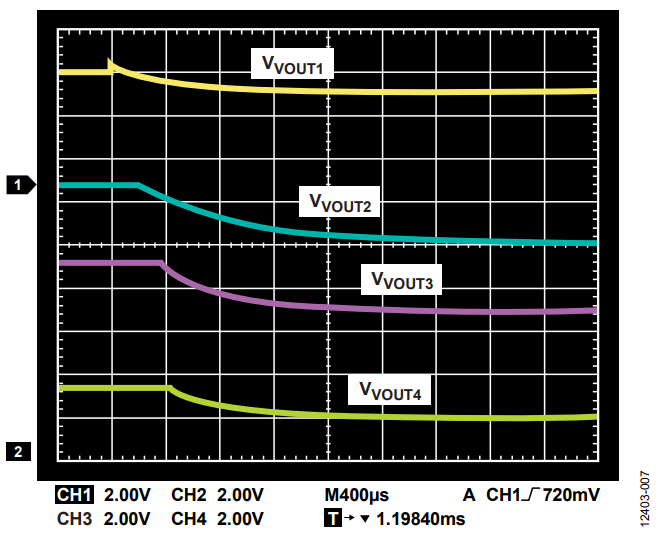

通過(guò)將一個(gè)調(diào)節(jié)器經(jīng)過(guò)衰減的輸出連接到下一個(gè)要上電的調(diào)節(jié)器的使能引腳,可以對(duì)多通道電源進(jìn)行時(shí)序控制,如圖5所示,其中,調(diào)節(jié)器按順序開(kāi)啟或關(guān)閉:從BUCK1到BUCK2,再到LDO1,最后到LDO2。圖6顯示了在將EN1連接到VIN1之后的上電序列。圖7所示為在將EN1從VIN1斷開(kāi)后的關(guān)斷序列。

圖5.利用ADP5134實(shí)現(xiàn)的簡(jiǎn)單時(shí)序控制

圖6.ADP5134啟動(dòng)序列

圖7.ADP5134關(guān)斷序列

序列器IC提高時(shí)序精度

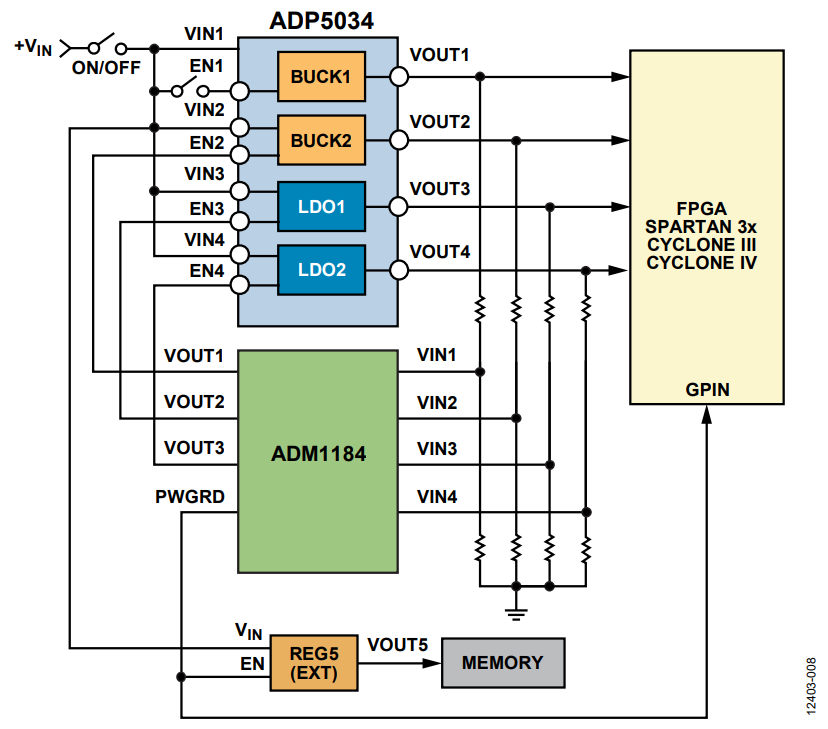

在某些情況下,實(shí)現(xiàn)精密時(shí)序比減少PCB面積、節(jié)省成本更重要。對(duì)于這類應(yīng)用,可以使用電壓監(jiān)控和序列器IC,如ADM1184四通道電壓監(jiān)控器,后者在電壓和溫度范圍內(nèi)的精度達(dá)±0.8%。另一種選擇是帶可編程時(shí)序的ADM1186四通道電壓序列器和監(jiān)控器;該器件可用于要求對(duì)上電和關(guān)斷序列進(jìn)行更精準(zhǔn)控制的應(yīng)用。

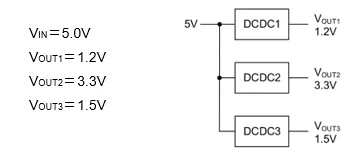

例如,ADP5034 4通道調(diào)節(jié)器集成了2個(gè)3MHz、1200mA降壓調(diào)節(jié)器和2個(gè)300mA LDO。可以利用ADM1184實(shí)現(xiàn)典型的時(shí)序控制功能,用于監(jiān)控一個(gè)調(diào)節(jié)器的輸出電壓,并在受監(jiān)控的輸出電壓達(dá)到某個(gè)水平時(shí),向下一個(gè)調(diào)節(jié)器的使能引腳提供一個(gè)邏輯高信號(hào)。如圖8所示,這種方法可用于不提供精密使能功能的調(diào)節(jié)器。

圖8.利用ADM1184四通道電壓監(jiān)控器對(duì)ADP5034 4通道調(diào)節(jié)器進(jìn)行時(shí)序控制

結(jié)論

利用ADP5134精密使能輸入引腳進(jìn)行時(shí)序控制非常簡(jiǎn)單,實(shí)現(xiàn)起來(lái)也很方便,每個(gè)通道只需要2個(gè)外部電阻即可。借助ADM1184或ADM1186電壓監(jiān)控器,可以實(shí)現(xiàn)更加精確的時(shí)序控制。

原文轉(zhuǎn)自亞德諾半導(dǎo)體

-

微控制器

+關(guān)注

關(guān)注

48文章

7552瀏覽量

151423 -

電源

+關(guān)注

關(guān)注

184文章

17718瀏覽量

250170 -

時(shí)序控制

+關(guān)注

關(guān)注

0文章

37瀏覽量

11964 -

浪涌電流

+關(guān)注

關(guān)注

1文章

201瀏覽量

25304

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何簡(jiǎn)化并實(shí)現(xiàn)復(fù)雜的電源時(shí)序控制

輕松實(shí)現(xiàn)復(fù)雜電源時(shí)序控制

基于高性能模擬器件的精密電源時(shí)序控制實(shí)現(xiàn)

復(fù)雜電源的時(shí)序控制解決方案

輕松實(shí)現(xiàn)復(fù)雜電源時(shí)序控制

電源時(shí)序控制或電源定序

輕松實(shí)現(xiàn)復(fù)雜電源時(shí)序控制

輕松實(shí)現(xiàn)復(fù)雜電源時(shí)序控制

復(fù)雜電源時(shí)序控制如何輕易實(shí)現(xiàn)?資料下載

輕松實(shí)現(xiàn)復(fù)雜的電源排序

輕松實(shí)現(xiàn)復(fù)雜的電源時(shí)序控制

輕松實(shí)現(xiàn)復(fù)雜的電源時(shí)序控制

評(píng)論