1、$fwrite 向文件寫入數(shù)據(jù) $fdisplay 格式:$fwrite(fid,"%h%hn",dout_r1,dout_r2);

(1)fwrite是需要觸發(fā)條件的,需要手動添加換行。

(2)如果寫放文件的格式為%d,則認(rèn)為是無符號數(shù),如下例: wire [27:0] data; fp_re = $fopen("dout.txt","w"); always @(posedge clk) begin if(dout_rdy == 1'b1) $fwrite(fileid,"%d",data); end

如果要輸出有符號數(shù)據(jù),需要將信號定義為有符號數(shù)。

eg:wire signed [27:0] data;

(3)輸出頂層文件中例化的信號(或下一級例化的文件的信號)

eg:$fwrite(file_id,"%d%12dn",u_coef_update.ekxdn_i,

u_coef_update.u_mult.mult_out);

在文件coef_update中定義的信號或REG ekxdn_i,如果要輸出有符號數(shù),

要在coef_update中把ekxdn_i定義為signed;

在文件coef_update文件中例化文件u_mult,輸出相應(yīng)的信號mult_out. 2、$fscanf 從文件中讀取數(shù)據(jù) (1)讀取格式為按行讀取,一行讀完之后再轉(zhuǎn)向下一行; (2)讀取也是需要觸發(fā)條件的; always @ ( posedge clk ) begin if(cnt_test == 3'd7) begin $fscanf(coef_file,"%d%d%d%d",coef01_i,coef01_q,coef02_i,coef02_q); $fscanf(ref_file,"%d%d%d%d",ref01_i,ref01_q,ref02_i,ref02_q); end end 3、$fopen 打開文件 (1) 在讀寫文件之前,一定要用fopen打開文件 (2)讀寫路徑的設(shè)置 file_id = $fopen("F:/modelsim/coef.txt"),注意這里的斜杠方向。

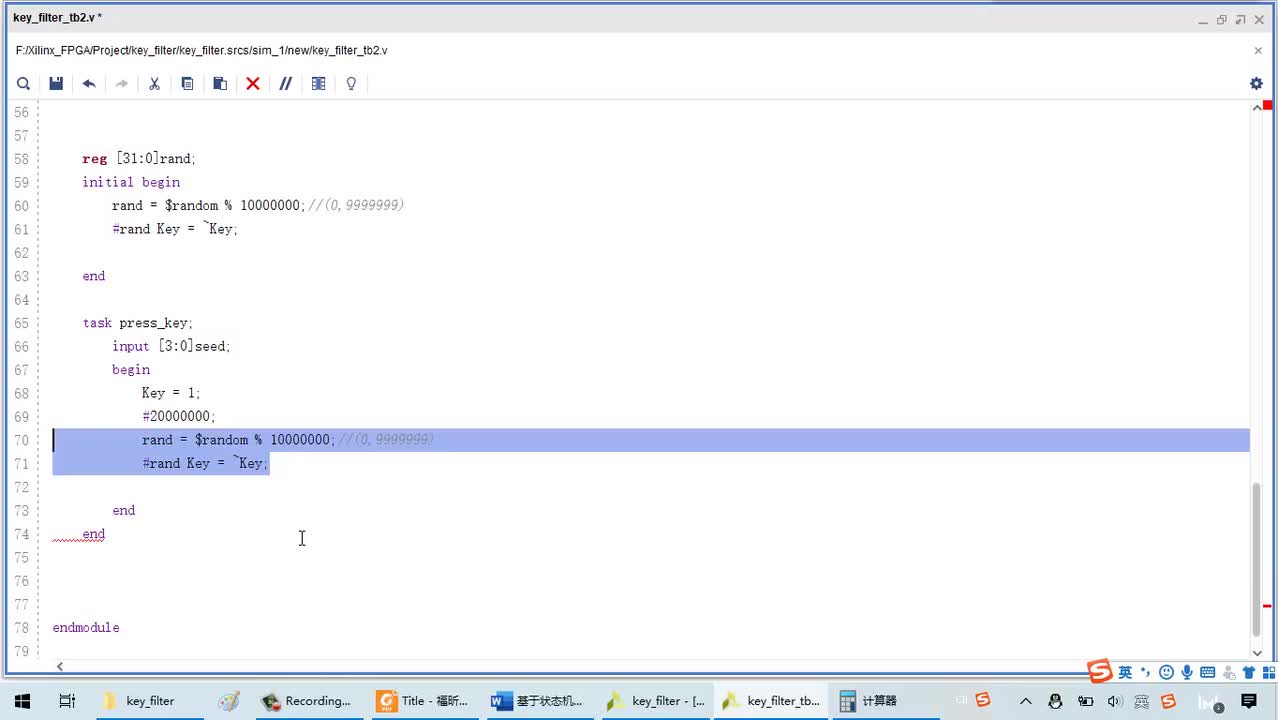

4、$random

random_function ::= $random [ ( seed ) ]

$random產(chǎn)生一個32位的有符號數(shù),seed可以是reg,integer,time類型

Example 1—Where b is greater than 0, the expression ($random % b) gives a number in the following range: [(-b+1): (b-1)].

產(chǎn)生–59 到59的數(shù): reg [23:0] rand; rand = $random % 60; Example 2—用連接符產(chǎn)生0 to 59: reg [23:0] rand; rand = {$random} % 60;

=====================================

操作實例:

=====================================

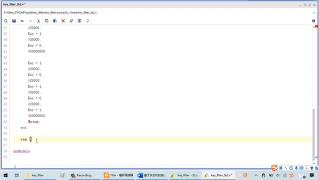

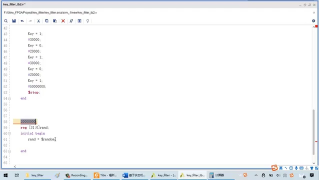

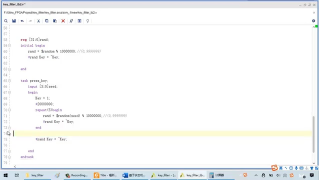

integer step_file; //文件要定義成integer

//open the fileInitialBeginstep_file = $fopen("F:/Company/Src/txt/step.v","r"); file_ekxdn =$fopen("F:/Company/Src/txt/ekxdn.v","w");end always #5 clk = !clk; //read data from file

always @ ( posedge clk )//read from the file begin if( cnt_test[2:0] == 0 ) $fscanf(step_file,"%d%d",ref01_i,ref01_q);

end

//write data to file wire signed[24:0] ekxdn_i,ekxdn_q; always @( posedge clk ) begin if( cnt_test[2:0] == 3'b111 ) $fwrite(nx_coef_file,"%d%12dn",nx01_coef_i,nx01_coef_q);end

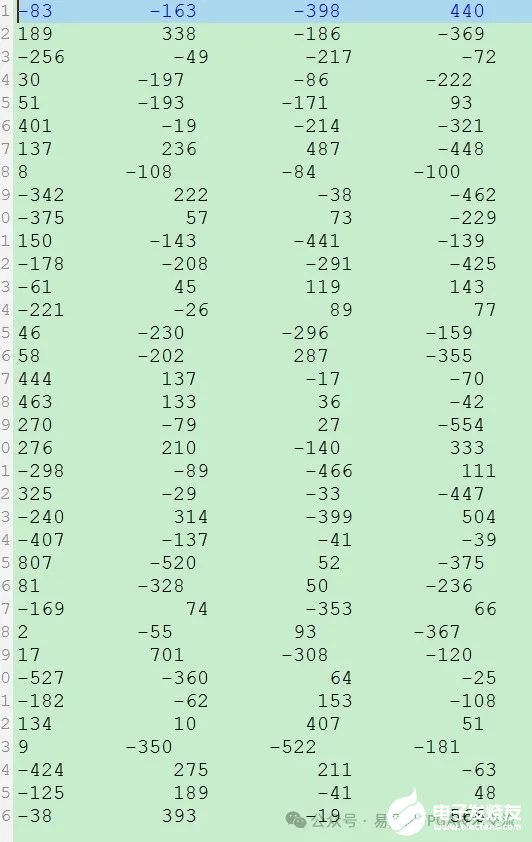

讀寫文件的數(shù)據(jù)格式如下:

? ? ? ? ? ? ? ? ? ? ?

? ? ? ? ? ? ? ? ? ? ?

以下點要注意:

1、可能由于加密的原因,讀不了txt文件,只能讀。V的了

2、打開文件的$fopen語句必須放在initial 中才可以

3、必須注意路徑中斜杠的方向“/”

4、相對路徑的設(shè)置(請參考積累中的“相對路徑與絕對路徑”)

5、如果讀入的是有符號數(shù),那么要把數(shù)據(jù)的類型定義為signed

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110100 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4331瀏覽量

62618

發(fā)布評論請先 登錄

相關(guān)推薦

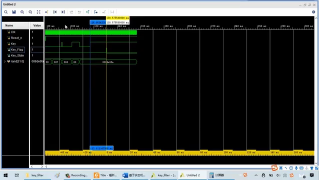

#硬聲創(chuàng)作季 #FPGA Xilinx入門-15C 基于Verilog系統(tǒng)函數(shù)語法的按鍵抖動模擬與仿真-1

#硬聲創(chuàng)作季 #FPGA Xilinx入門-15C 基于Verilog系統(tǒng)函數(shù)語法的按鍵抖動模擬與仿真-2

22 15C 基于Verilog系統(tǒng)函數(shù)語法的按鍵抖動模擬與仿真 - 第1節(jié) #硬聲創(chuàng)作季

22 15C 基于Verilog系統(tǒng)函數(shù)語法的按鍵抖動模擬與仿真 - 第2節(jié)

22 15C 基于Verilog系統(tǒng)函數(shù)語法的按鍵抖動模擬與仿真 - 第3節(jié) #硬聲創(chuàng)作季

22 15C 基于Verilog系統(tǒng)函數(shù)語法的按鍵抖動模擬與仿真 - 第4節(jié) #硬聲創(chuàng)作季

22 15C 基于Verilog系統(tǒng)函數(shù)語法的按鍵抖動模擬與仿真 - 第5節(jié) #硬聲創(chuàng)作季

Verilog的打印系統(tǒng)函數(shù)有哪幾類? 在使用Verilog時有哪些注意事項?

Verilog HDL語言中任務(wù)與函數(shù)的比較

剖析verilog2005的騷操作之對數(shù)函數(shù)

Verilog數(shù)字系統(tǒng)設(shè)計——任務(wù)和函數(shù)二(系統(tǒng)任務(wù)readmemb或readmemh)

verilog系統(tǒng)函數(shù)

verilog系統(tǒng)函數(shù)

評論