本文翻譯轉(zhuǎn)載于:Cadence blog

作者:Deep Mehta

由于全球數(shù)據(jù)流量呈指數(shù)級增長,PCIe 6.0 交換機(jī)的市場需求也出現(xiàn)了激增。PCIe 6.0 交換機(jī)在高性能計(jì)算(HPC)系統(tǒng)(尤其是數(shù)據(jù)中心)中為需要大帶寬和超低延遲的應(yīng)用提供了重要的數(shù)據(jù)傳輸支持。然而,確保這些交換機(jī)嚴(yán)格滿足性能、能效和成本等要求是一項(xiàng)艱巨的挑戰(zhàn)。盡管如此,全面的測試和驗(yàn)證過程還是能夠降低這些交換機(jī)設(shè)計(jì)的復(fù)雜性。

傳統(tǒng)的驗(yàn)證方法仍具有價(jià)值,如 PCIe 5.0 交換機(jī)采用數(shù)據(jù)完整性和虛擬通道仲裁測試。盡管如此,PCIe 6.0 要求采用更全面的驗(yàn)證方法——比基本功能驗(yàn)證更深入的高階驗(yàn)證策略,其中包括生成用于識別潛在性能問題并確保交換機(jī)在實(shí)際場景中以最佳狀態(tài)運(yùn)行的反向壓力流量。只有主動(dòng)應(yīng)對這些挑戰(zhàn),才能設(shè)計(jì)出滿足高性能計(jì)算應(yīng)用要求的低延遲、高帶寬交換機(jī)。

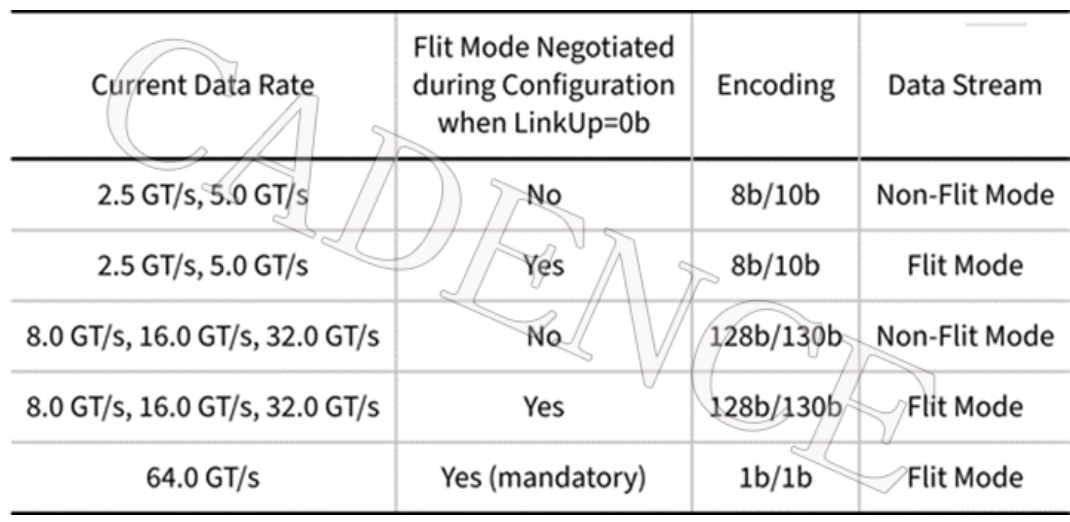

Flit 模式和非Flit 模式的互操作性

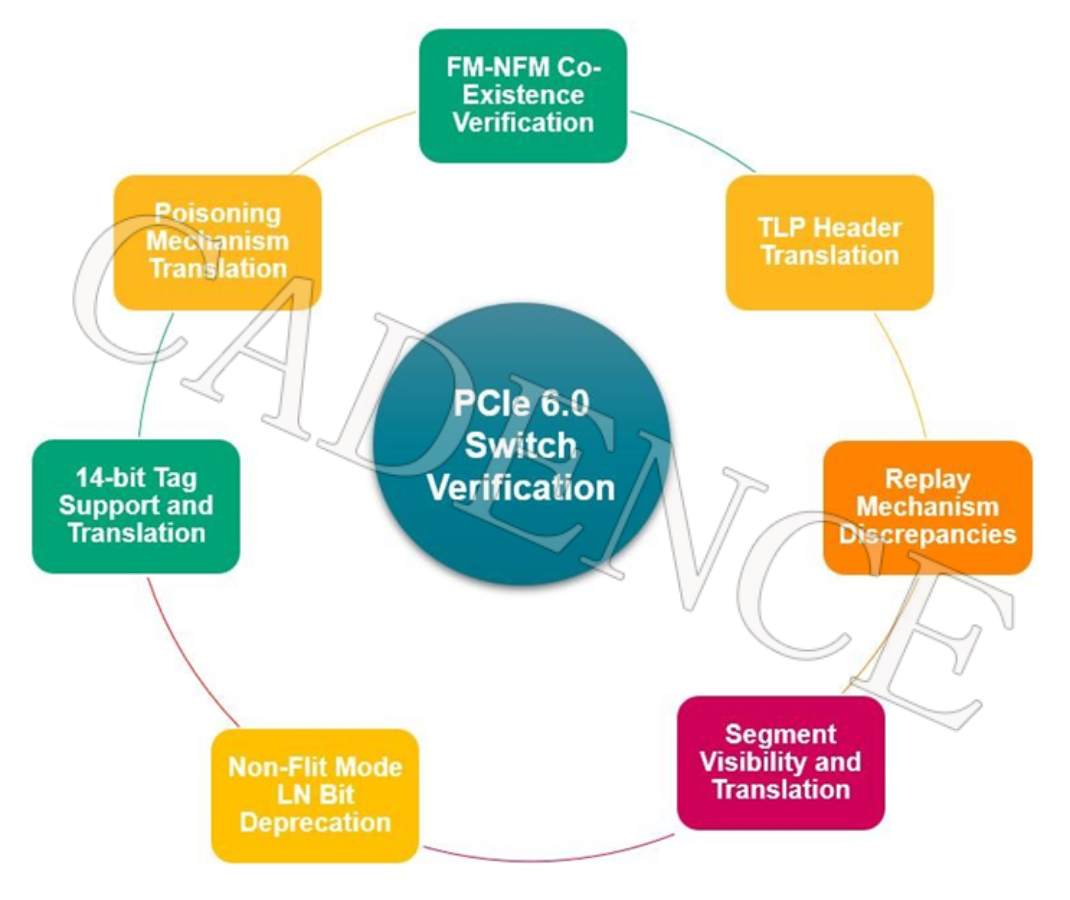

PCIe 6.0 新增的 Flit 模式對交換機(jī)提出了全新的驗(yàn)證挑戰(zhàn)。如下圖所示,我們可以將驗(yàn)證分為幾個(gè)關(guān)鍵領(lǐng)域來思考。

●共存驗(yàn)證:交換機(jī)必須能夠有效處理通過不同端口的 Flit 模式(FM)和非 Flit 模式(NFM)的混合流量。這種驗(yàn)證方法確保了交換機(jī)的性能不會因?yàn)榱髁磕J降漠悩?gòu)性而降低。

●事務(wù)層數(shù)據(jù)包(TLP)的數(shù)據(jù)頭轉(zhuǎn)換:NFM 和 FM 使用不同的數(shù)據(jù)頭格式。當(dāng)入口端和出口端采用不同運(yùn)行模式時(shí),交換機(jī)就需要對不同格式進(jìn)行轉(zhuǎn)換,驗(yàn)證策略的重點(diǎn)是確保該轉(zhuǎn)換過程的正確性。

●重傳機(jī)制差異:FM 和 NFM 使用不同的重傳機(jī)制。驗(yàn)證策略必須考慮這些差異,才能在重傳期間妥善處理傳輸錯(cuò)誤并確保數(shù)據(jù)完整性。

●段的可見性和轉(zhuǎn)換:段信息僅可在 FM 鏈路中直接訪問,這使得 FM 和 NFM 事務(wù)層數(shù)據(jù)包(TLP)之間的路由變得更復(fù)雜,尤其是當(dāng)入口端和出口端采用不同運(yùn)行模式時(shí)。例如,交換機(jī)有時(shí)會報(bào)告 TLP 轉(zhuǎn)換出口被阻止的錯(cuò)誤,因此必須根據(jù)轉(zhuǎn)換規(guī)則進(jìn)行驗(yàn)證。

設(shè)備 3 的能力寄存器具有一個(gè)“段捕獲”位;交換機(jī)在將一項(xiàng) TLP 從 NFM 轉(zhuǎn)換為 FM 時(shí),必須遵循段捕獲位的具體規(guī)則。

●棄用 NFM 中的 LN 位:PCIe 6.0 棄用了 NFM 中使用的 LN(輕量級通知)位。驗(yàn)證策略必須針對棄用的 LN 位制定專門的轉(zhuǎn)換規(guī)則。

●14 位標(biāo)簽支持和轉(zhuǎn)換:14 位標(biāo)簽是 FM 獨(dú)有的。PCIe 規(guī)范規(guī)定了將請求從 FM 轉(zhuǎn)換為 NFM 的具體轉(zhuǎn)換規(guī)則,以解決標(biāo)簽位數(shù)差異的問題。

●中毒機(jī)制轉(zhuǎn)換:如果在 FM TLP 轉(zhuǎn)換為 NFM TLP 的過程中應(yīng)用了任一種中毒機(jī)制,則必須設(shè)置 NFM TLP 的錯(cuò)誤中毒位(EP位)。相反,從 NFM 轉(zhuǎn)換到 FM 時(shí),如果在 NFM TLP 中設(shè)置了 EP 位,則該 EP 位必須在轉(zhuǎn)換后的 FM TLP 中保留。驗(yàn)證策略應(yīng)確保交換機(jī)遵循這些中毒機(jī)制的轉(zhuǎn)換規(guī)則。

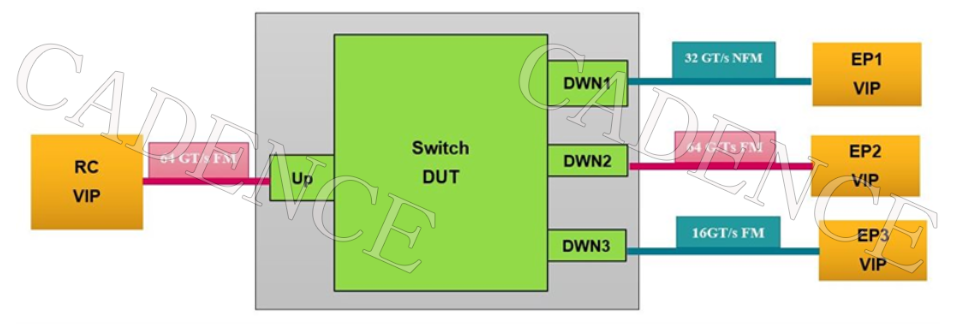

通過全面驗(yàn)證這些互操作性,設(shè)計(jì)人員可確保 PCIe 6.0 交換機(jī)有效且穩(wěn)定地處理 FM 和 NFM 的混合流量。以下拓?fù)鋱D展示了交換機(jī)端口上混合模式流量(FM 和 NFM)的一個(gè)示例場景,其中包含一個(gè)上行端口和三個(gè)下行端口,分別與根復(fù)合體(RC)和各個(gè)端點(diǎn)(EP)連接。

應(yīng)考慮的性能損失

雖然應(yīng)用這些轉(zhuǎn)換規(guī)則和各種共享或?qū)S眯庞霉芾砟軌蚝喕粨Q機(jī)的設(shè)計(jì),但在 Flit 模式下添加額外的無操作(NOP)流控單元或NOP TLP 可能增加性能損失,并額外增加非Flit 模式中的邏輯空閑(IDL)雙字節(jié)。這也是現(xiàn)在必須在交換機(jī)設(shè)計(jì)的驗(yàn)證和驗(yàn)收標(biāo)準(zhǔn)中進(jìn)行性能測試的原因。

交換機(jī)驗(yàn)證可以通過流量建模、延遲監(jiān)控和緩沖區(qū)分析來識別和糾正性能問題。

●流量建模:通過將大量 Flit 模式流量與非 Flit 模式流量互相轉(zhuǎn)換,開發(fā)模擬真實(shí)世界流量模式的測試場景。測試策略需要根據(jù)隨機(jī)因素評估,如不同的傳輸速度、鏈路寬度,以及生成的不同 TLP 類型的流量,確保所有交換機(jī)端口都采用了 Flit 模式和非 Flit 模式進(jìn)行驗(yàn)證。

●延遲監(jiān)控:監(jiān)控?cái)?shù)據(jù)包在通過交換機(jī)時(shí)產(chǎn)生的延遲,并重點(diǎn)關(guān)注頻繁轉(zhuǎn)換模式的路徑,找出可能表明轉(zhuǎn)換過程效率低下的異常延遲峰值。

●緩沖區(qū)分析:分析在流量模擬過程中交換機(jī)內(nèi)部緩沖區(qū)的行為。必須識別出任何接近滿載或溢出的緩沖區(qū)場景,因?yàn)檫@種情況可能表明過多的轉(zhuǎn)換負(fù)載導(dǎo)致出現(xiàn)潛在的性能問題。換言之,交換機(jī)端口必須根據(jù)協(xié)議標(biāo)準(zhǔn)的規(guī)定對 TLP(包括“保留”TLP)進(jìn)行緩沖和路由。

總 結(jié)?

Summary

PCIe 6.0 標(biāo)準(zhǔn)為 PCIe 協(xié)議的分層堆棧帶來了革命性的變化,其中最具顛覆性的創(chuàng)新是采用了“Flit”。根據(jù)標(biāo)準(zhǔn)的要求,交換機(jī)入口端會接收一個(gè)包含多目標(biāo) TLP 的 Flit 數(shù)據(jù)包,這些多目標(biāo) TLP 需要簡化路由邏輯,才能利用轉(zhuǎn)換邏輯將數(shù)據(jù)發(fā)送到相應(yīng)的出口端(反之亦然)。在應(yīng)用經(jīng) OHC 封裝的轉(zhuǎn)換邏輯時(shí),不同的共享或?qū)S眯庞霉芾砗?TLP 重傳機(jī)制的交換機(jī)路由邏輯可能會增加性能損失,僅驗(yàn)證數(shù)據(jù)集成測試無法識別出這種性能損失。必須對性能測試策略加以評估,才能確保對所有支持 Flit 模式和非 Flit 模式流量的交換機(jī)端口進(jìn)行全面驗(yàn)證。此外,性能測試還有助于識別在不同負(fù)載條件(即有效負(fù)載長度)下可能出現(xiàn)的潛在瓶頸或問題。

關(guān)于 Cadence

Cadence 是電子系統(tǒng)設(shè)計(jì)領(lǐng)域的關(guān)鍵領(lǐng)導(dǎo)者,擁有超過 30 年的計(jì)算軟件專業(yè)積累。基于公司的智能系統(tǒng)設(shè)計(jì)戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設(shè)計(jì)概念成為現(xiàn)實(shí)。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計(jì)算、5G 通訊、汽車、移動(dòng)設(shè)備、航空、消費(fèi)電子、工業(yè)和醫(yī)療等最具活力的應(yīng)用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產(chǎn)品。Cadence 已連續(xù)十年名列美國財(cái)富雜志評選的 100 家最適合工作的公司。

-

交換機(jī)

+關(guān)注

關(guān)注

21文章

2700瀏覽量

100941 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

5057瀏覽量

73018 -

PCIe

+關(guān)注

關(guān)注

16文章

1298瀏覽量

84326

原文標(biāo)題:利用有效的驗(yàn)證策略簡化 PCIe 6.0 交換機(jī)的設(shè)計(jì)

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何實(shí)現(xiàn)POE交換機(jī)串聯(lián)?

接入層交換機(jī)、匯聚層交換機(jī)和核心層交換機(jī)的區(qū)別

交換機(jī)如何工作

工業(yè)控制交換機(jī)和工業(yè)交換機(jī)的區(qū)別

核心交換機(jī)、匯聚交換機(jī)與普通交換機(jī)的區(qū)別介紹

家庭交換機(jī)怎么安裝_交換機(jī)網(wǎng)速是平分的嗎

網(wǎng)絡(luò)交換機(jī)的作用_網(wǎng)絡(luò)交換機(jī)怎么用

什么是網(wǎng)絡(luò)交換機(jī)?網(wǎng)絡(luò)交換機(jī)的分類標(biāo)準(zhǔn)

核心交換機(jī)、匯聚交換機(jī)、接入交換機(jī)之間的對比分析

pcie2.0交換機(jī)資料

PoE交換機(jī)可以當(dāng)普通交換機(jī)使用嗎

以太網(wǎng)交換機(jī)的升級版:PCIe交換機(jī)

評論