- 串聯電路

- 晶體負載電容

- 并聯電路

- 驅動電平

- 頻率與振蕩模式

- 設計注意事項

- 負阻抗

在這篇文章中,我們將介紹振蕩器設計的基礎知識以及晶體振蕩器電路設計的 7個關鍵組件中的每一個。

什么是晶體振蕩器電路?(振蕩器電路基礎知識)

晶體振蕩器電路由放大器和反饋網絡組成。反饋網絡從放大器獲取特定輸出,并將其發送回放大器輸入。拉出來的時候看起來很簡單......

...但是,我們越深入,就越復雜。抓緊!

晶體振蕩器電路要有效運行,必須滿足兩個關鍵條件:

- 環路功率增益必須等于一致。

- 環路相移必須等于0、2Pi、4Pi等弧度。

直接回到放大器輸入端的功率必須足以為放大器輸入和振蕩器良率提供電源,并克服電路損耗。

振蕩器的精確頻率由振蕩器電路內的環路相移決定。相移的任何變化都會導致頻率的變化。減少凈相移的最佳方法之一是在反饋回路中使用石英晶體。我們在TROQ生產的所有晶體都包括石英晶體(石英晶體振蕩器)。

當振蕩器的反饋回路中使用石英晶體時,振蕩器的頻率輸出實際上是自我調節的。石英晶體產生滿足相環要求的電抗。

現在您已經對晶體振蕩器設計的基礎知識有了扎實的了解,讓我們來看看晶體振蕩器電路設計的關鍵考慮因素。

晶體振蕩器電路設計的 7個關鍵考慮因素

- 串聯電路

串聯電路晶體振蕩器使用設計用于在其固有諧振頻率下工作的晶體。對于此類電路,反饋回路中不需要電容器。串聯諧振器電路是相當基本的,通常使用,因為它們的元件數量很少。

串聯電路可以提供通過晶體以外的反饋路徑。這意味著即使在晶體故障期間,電路也可能繼續以主觀頻率振蕩。

串聯電路的一個重大缺點是,如果系統需要修改,則無法調整輸出頻率。串聯諧振晶體設計為首選的頻率、容差和穩定性,并且無需調整選項即可保持。

2.負載電容

負載電容在振蕩器電路設計中起著至關重要的作用。在下一個設計考慮因素中,您將看到負載電容重要性的示例,但現在,讓我們仔細看看負載電容本身。

負載電容被描述為在電路中的晶體端子上測量或計算的電容量。

當涉及到串聯電路時,晶體電路的連接點之間沒有電容。因此,電路中沒有負載電容。對于并聯電路來說,情況就不同了。

要確定并聯電路中的負載電容(在設計考慮因素 #3中描述)

在這個等式中,LC1和LC2表示負載電容。Cs是電路雜散電容(通常在 3到 5 pF之間)。

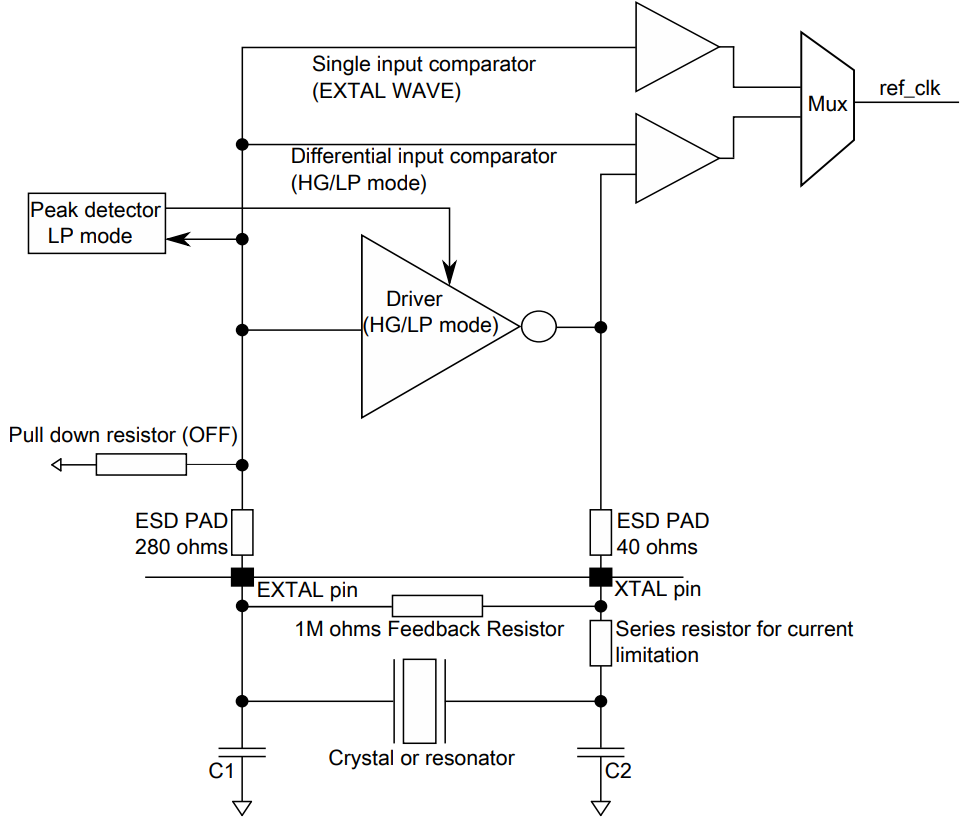

3.并聯電路

并聯諧振振蕩器電路由晶體制成,該晶體設計用于在特定負載電容下工作。這導致晶體振蕩器的工作頻率高于串聯諧振頻率,但低于真正的并聯諧振頻率。

要完成此類電路中的反饋回路,必須設計穿過晶體的路由。如果晶體發生故障,電路將不再振蕩。

那么決定振蕩器頻率的負載電容從何而來呢?該電路實際上使用一個單獨的逆變器,在反饋回路中有兩個電容器,包括負載電容。如果負載電容發生變化,振蕩器產生的頻率也會發生變化。

話雖如此,重要的是要注意,如果需要,這種電路類型并不適合輕松調整頻率。此外,還需要精確的頻率控制和負載電容的精確規格。

例如,如果將容量為20 pF的20 MHz晶體放置在評估值為30 pF的電路中,則晶體將低于指定值。但是,如果電路的評估值僅為10 pF,則頻率將高于指定值。

4.驅動電平

驅動電平是晶體在運行時消耗的功率。功率通常以毫瓦或微瓦來描述。

石英晶體被指定為可以影響振蕩器頻率和工作模式的最大驅動電平值。與晶體振蕩器供應商合作,確定石英振蕩器可以維持的最大驅動電平非常重要。

那么,如果晶體振蕩器超過最大驅動電平會發生什么?它可能導致振蕩器:

- 變得不穩定

- 加快老齡化速度

- 在關鍵應用中導致通信丟失或時序丟失

要計算晶體的驅動電平,請使用以下公式(基本上只是歐姆定律,但用于功率):

驅動電平 =(Irms2x R)

在這個方程中,Irms是通過石英晶體的測量 RMS電流,R是石英晶體的最大電阻。

要測量晶體振蕩器電路的實際驅動電平,可以在其中插入一個電阻器。然后可以讀取電阻兩端的壓降,以計算電流和功率耗散。當然,請確保在此測量后移除電阻器。

5.頻率與模式

晶體振蕩器的頻率可能受到物理尺寸的限制。有時,這可能是某些應用程序的長度和寬度。其他時候,它可能是石英晶體本身的厚度。石英晶圓越薄,頻率就越高。石英晶圓的厚度通常變得太薄,無法在30 MHz左右進行加工。

如果您需要頻率高于極限頻率的振蕩器,則可以利用基頻。基頻被定義為“由整個物體的振蕩產生的最低頻率,與更高頻率的諧波不同。如果晶體的基頻為10 MHz,它也可以在基頻的3倍、5倍、7倍等處振蕩。因此,振蕩器可以在 30 MHz、50 MHz、70 MHz等頻率下振蕩。這些是頻率的泛音。

當需要使用泛音頻率時,晶體制造商必須將晶體設計為在所需的泛音頻率下工作。切勿嘗試訂購基波模式晶體,然后在另一個所需的泛音下操作它,因為基波晶體和泛音晶體的晶體制造工藝不同。

6.設計注意事項

為了獲得最佳振蕩器電路操作,應遵循一些設計注意事項。始終建議的一件事是避免在電路中并聯走線。這樣做可以減少雜散電容。所有跡線應盡可能短,以防止耦合。使用接地平面保持組件隔離也有助于解決這個問題。

7.負阻抗

振蕩器的設計必須能夠增強負阻抗以獲得最佳性能。負阻抗通常也稱為振蕩余量。

以下是幫助您計算振蕩器電路中負阻抗的六個簡單步驟:

- 臨時安裝一個與晶體串聯的可變電阻器。

- 將電阻器設置為最低設置(接近零歐姆)。

- 啟動振蕩器上電并監控示波器上的輸出。

- 在持續監控示波器信號時,使用可變電阻器開始增加電路中的電阻。

- 一旦振蕩停止,請注意可變電阻器以確定歐姆值。

- 將晶體的最大電阻值(由供應商指定)與步驟 5中測量的歐姆值相加。

計算出的總值是負阻抗或振蕩余量。對于一般經驗法則,負阻抗應至少為晶體指定最大電阻值的 5倍,才可靠。

石英晶體振蕩器,讓您的下一個項目更進一步

近20年來以來,TROQ創捷電子一直在設計和制造晶體振蕩器。瀏覽我們的全系列頻率產品,找到適合您項目需求的產品,或立即聯系我們的工程師以了解更多信息。

-

振蕩器

+關注

關注

28文章

3832瀏覽量

139094 -

晶振

+關注

關注

34文章

2866瀏覽量

68038 -

振蕩器電路

+關注

關注

1文章

43瀏覽量

16602 -

晶體振蕩器

+關注

關注

9文章

621瀏覽量

29123

發布評論請先 登錄

相關推薦

這7個關鍵因素,您在設計LDO必須重點考慮資料下載

無源晶振的選型理念 無源晶振的EMC電路設計

超詳細!晶振電路設計的7個關鍵因素,小白也能變高手!

超詳細!晶振電路設計的7個關鍵因素,小白也能變高手!

評論