有些特殊的外設會使用基于SPI模式,發送連續比特流來傳輸數據。本文主要介紹對于Renesa RA,如何使用SPI來實現高速比特流的發送。

注意,此方式僅針對搭載了支持該工作模式SPI外設的RA產品,使用前請在硬件手冊中確認這一點。

靈活的Renesas Advanced(RA)32位MCU是采用Arm Cortex-M33、-M23、-M4和-M85處理器內核,并經過PSA認證的、行業領先的32位MCU。RA可提供更為強大的嵌入式安全功能、卓越的CoreMark性能和超低的運行功率,相比競爭對手的Arm Cortex-M MCU具有重大優勢。PSA認證可為客戶提供信心和保障,幫助其快速部署安全的物聯網端點和邊緣設備,以及適用于工業4.0的智能工廠設備。

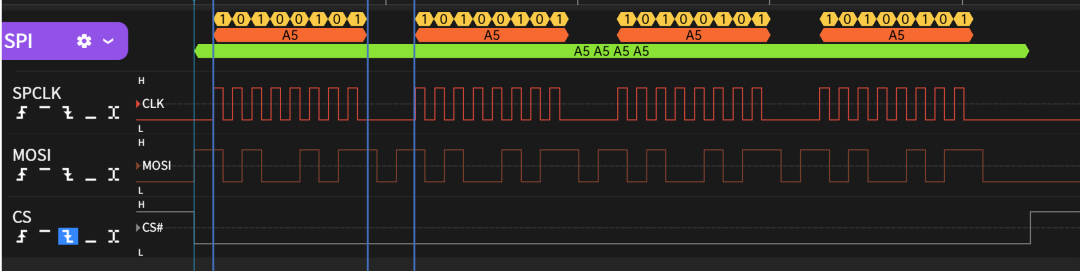

RSPI在正常的配置模式下,如果發送4個字節,總線上波形如下圖所示。在每兩個字節之間都有delay的插入。

點擊可查看大圖

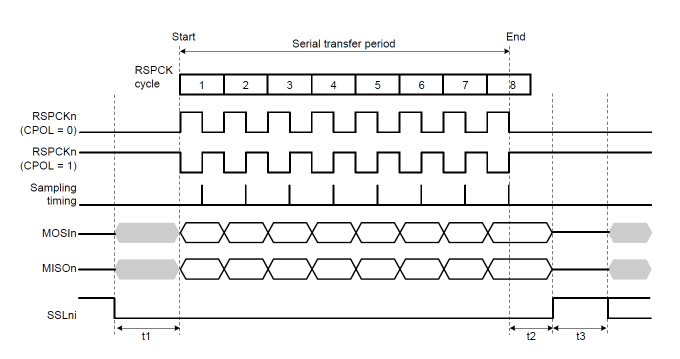

手冊上關于這部分的描述如下:

t1是從SSLn生效到第一個clock的延時

t2是最近一個CLK結束到SSLn失效的延時

t3是SSLn再次使能之前的延時

但是這樣會造成比特流不連續,無法滿足某些特定應用的要求。

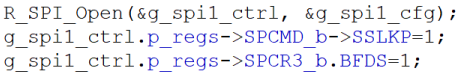

SPI實際上還提供了Burst功能,用于產生連續的比特流,該功能尚未在FSP界面中支持,當前可通過手動修改R_SPI代碼實現,把寄存器位SSLKP和BFDS置位。更新代碼如下所示:

點擊可查看大圖

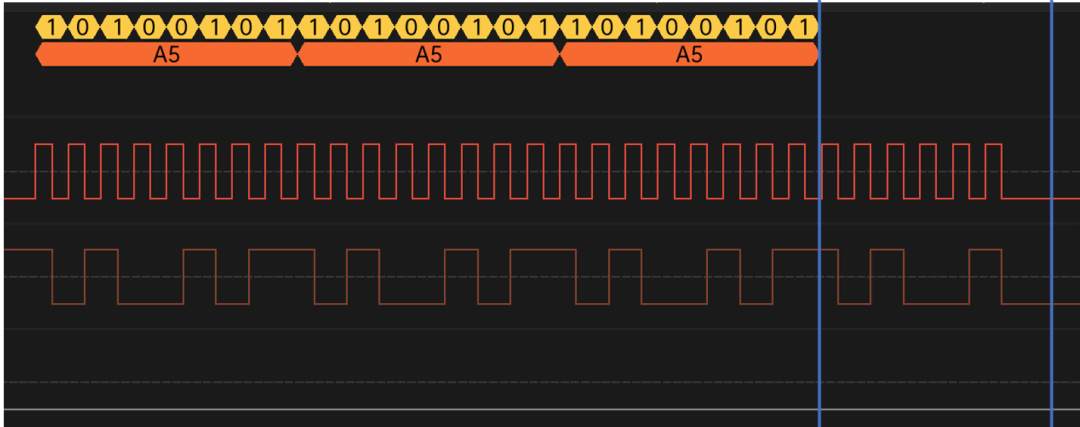

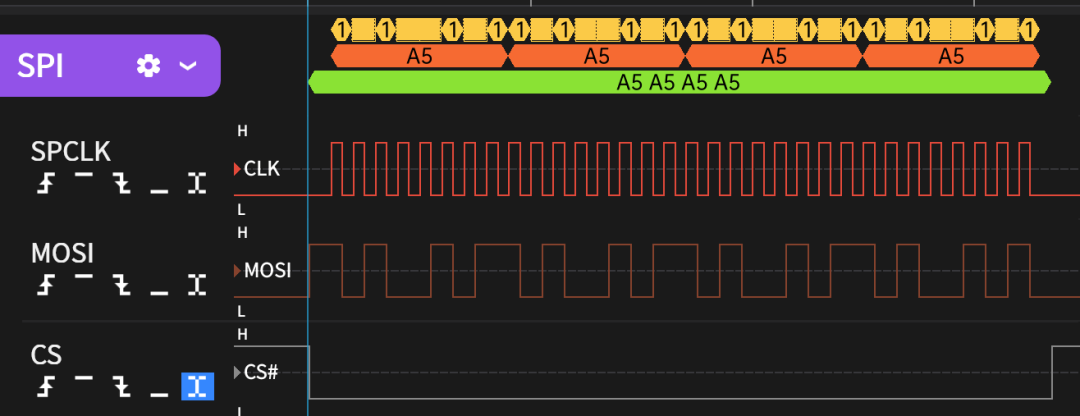

修改代碼后,測試波形結果如下圖:

點擊可查看大圖

細心的小伙伴會發現,最后一個字節沒有發送完成。仔細檢查發現,在最后一個字節發送的過程中,RSPCK上缺少兩個clock,實際上程序也沒有進入發送完成中斷。

所以光這樣還不行,還需要在發送中斷程序中做一下處理。

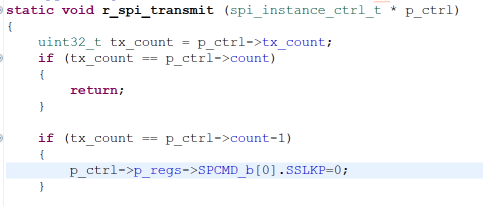

在rafspsrc _spi _spi.c的函數r_spi_transmit函數中增加一個判斷,在發送最后一個字節前,重新把SSLKP清零:

點擊可查看大圖

這是修改后的時序,字節間已經沒有插入delay,保證了比特流的連續性。

點擊可查看大圖

需特別注意的是,假如生成連續比特流,則不支持通過DMA/DTC進行SPI傳輸。

另外,如果不切換FSP的版本,對于源碼的修改,RA文件夾中可以保留,但是ra_cfg和ra_gen文件夾中的內容會被FSP重寫。如果切換FSP的版本,則三個文件夾(ra,ra_cfg和ra_gen)中的內容均會被FSP重寫。

對該功能的支持已加入FSP的開發計劃,屆時無需手動修改,僅需在FSP Stack中配置即可。

-

處理器

+關注

關注

68文章

19286瀏覽量

229842 -

mcu

+關注

關注

146文章

17148瀏覽量

351197 -

SPI

+關注

關注

17文章

1706瀏覽量

91582 -

RA

+關注

關注

0文章

19瀏覽量

24680 -

比特流

+關注

關注

0文章

10瀏覽量

8128

原文標題:關于使用RSPI來發送連續比特流的方法

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

了解FPGA比特流結構

無法生成比特流

將時鐘與輸入比特流同步

無法生成比特流

中途向ICAP中止寫入部分比特流

怎么使用ISE Webpack生成比特流

如何使用Vivado生成特定的部分比特流

請問如何在Vivado中更改比特流文件的位置?

如何從同一實現生成2種類型的比特流(SPI x4和SelectMAP x16)

是否需要在flash上??切換黃金比特流和多重比特流的位置?

匹配位置對比特流隨機性的影響研究

使用加密和身份驗證來保護UltraScale/UltraScale+ FPGA比特流

Renesa RA如何使用SPI來實現高速比特流的發送

Renesa RA如何使用SPI來實現高速比特流的發送

評論