一、引言

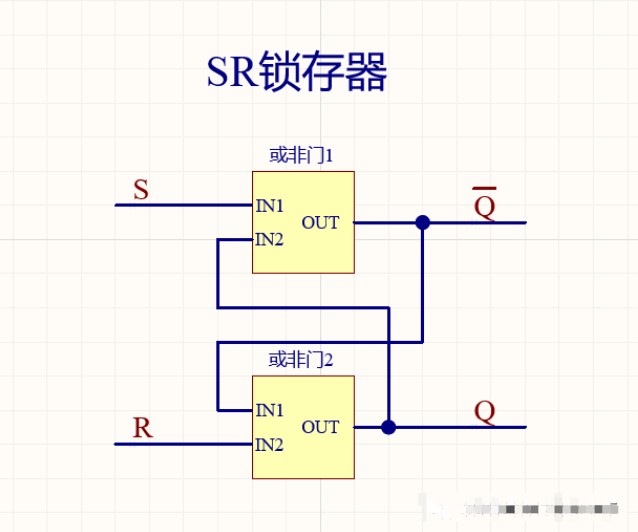

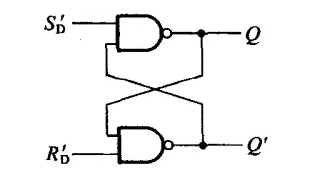

SR鎖存器(Set-Reset Latch)是數字電路中的一種基本存儲元件,用于存儲一個比特(bit)的數據。它由兩個互補的門電路組成,通常是兩個非門(或非門、與非門)構成,通過兩個輸入端(S和R)來控制鎖存器的狀態。盡管SR鎖存器結構簡單且功能強大,但在特定輸入條件下會進入一種被稱為“不定狀態”的特殊狀態。

二、SR鎖存器的基本工作原理

SR鎖存器通過兩個輸入端S(Set)和R(Reset)來控制其輸出狀態。基本的工作原理如下:

- 置位(Set) :當S=1且R=0時,鎖存器被置位,輸出Q=1,Q'=0。此時,S端被稱為置數端。

- 復位(Reset) :當S=0且R=1時,鎖存器被復位,輸出Q=0,Q'=1。此時,R端被稱為清零端。

- 保持(Hold) :當S=0且R=0時,鎖存器保持上一狀態不變。

三、不定狀態的產生原因

SR鎖存器的不定狀態主要源于其輸入端S和R在同時有效(即同時為1)時的特殊行為。在理想情況下,當S和R均為1時,SR鎖存器的輸出狀態應該是確定的。然而,在實際電路中,由于信號傳輸的延遲、器件間的差異以及時序問題等因素,當S和R同時由0變為1時,中間會引入短暫的“01”或“10”這樣的中間狀態。這些中間狀態的具體表現取決于信號傳輸的先后順序和電路的物理特性,因此無法預測和確定。

此外,當S和R同時由有效(1)變為無效(0)時,由于信號傳播速度的差異和電路內部的寄生效應,也可能導致輸出狀態的不確定。這種由輸入變化引起的輸出狀態不確定現象,就是SR鎖存器的不定狀態。

四、不定狀態的表現形式

SR鎖存器進入不定狀態時,其輸出Q和Q'的狀態無法預測。具體來說,Q和Q'可能同時為高電平、同時為低電平,或者一個為高電平而另一個為低電平。這種不確定性會對電路的穩定性和可靠性產生嚴重影響。

在實際應用中,為了避免SR鎖存器進入不定狀態,通常會在設計時采取以下措施:

- 避免S和R同時有效 :在電路設計中,應確保S和R不會同時被置為高電平。這可以通過邏輯門電路的設計來實現,例如使用與門(AND gate)來確保S和R不會同時為1。

- 使用時鐘信號控制 :在更復雜的電路中,可以使用時鐘信號來控制SR鎖存器的輸入變化。這樣,只有在時鐘信號的特定邊沿(如上升沿或下降沿)到來時,S和R的輸入才會被鎖存器接收并處理。這種方式可以有效避免不定狀態的產生。

- 優化電路布局和布線 :合理的電路布局和布線可以減少信號傳輸的延遲和干擾,降低不定狀態發生的可能性。

五、不定狀態的影響與應對措施

SR鎖存器的不定狀態會對電路的穩定性和可靠性產生嚴重影響。在數字系統中,不確定的輸出狀態可能導致數據錯誤、邏輯混亂甚至系統崩潰。因此,必須采取措施來避免或減輕不定狀態的影響。

除了上述的避免S和R同時有效、使用時鐘信號控制以及優化電路布局和布線等措施外,還可以采取以下策略來應對不定狀態:

- 增加狀態檢測電路 :在SR鎖存器的輸出端增加狀態檢測電路,用于檢測輸出是否處于不定狀態。一旦發現不定狀態,可以立即采取措施(如復位電路)來恢復正常的輸出狀態。

- 使用更穩定的鎖存器類型 :在某些對穩定性要求極高的應用中,可以考慮使用更穩定的鎖存器類型(如D鎖存器、JK鎖存器等),這些鎖存器具有更復雜的控制邏輯和更高的穩定性。

六、結論

SR鎖存器作為數字電路中的一種基本存儲元件,在數字系統中發揮著重要作用。然而,其不定狀態的存在對電路的穩定性和可靠性構成了威脅。通過深入理解SR鎖存器的工作原理和不定狀態的產生原因,我們可以采取有效的措施來避免或減輕不定狀態的影響。

-

元件

+關注

關注

4文章

926瀏覽量

36711 -

鎖存器

+關注

關注

8文章

906瀏覽量

41537 -

門電路

+關注

關注

7文章

199瀏覽量

40183 -

數字電路

+關注

關注

193文章

1606瀏覽量

80658

發布評論請先 登錄

相關推薦

sr鎖存器不定狀態的產生原因

sr鎖存器不定狀態的產生原因

評論