組合邏輯電路是數字電路中的一種基本類型,它由邏輯門組成,根據輸入信號的組合產生相應的輸出信號。組合邏輯電路廣泛應用于計算機、通信、控制等領域。設計組合邏輯電路需要遵循一定的步驟,以確保電路的正確性和可靠性。

- 需求分析

需求分析是設計組合邏輯電路的第一步,也是最重要的一步。在這個階段,我們需要明確電路的功能、輸入輸出信號、性能要求等。需求分析的目的是確保電路設計滿足實際應用的需求。

1.1 功能定義

功能定義是需求分析的核心,需要明確電路需要實現的具體功能。例如,一個簡單的邏輯門電路可能只需要實現基本的邏輯運算,如與、或、非等;而一個復雜的數字電路可能需要實現復雜的算法和數據處理。

1.2 輸入輸出信號

輸入輸出信號是電路設計的基礎,需要明確電路的輸入信號和輸出信號。輸入信號可以是數字信號、模擬信號或者混合信號;輸出信號可以是數字信號、模擬信號或者混合信號。同時,還需要明確輸入輸出信號的電平、頻率、幅度等參數。

1.3 性能要求

性能要求是電路設計的重要指標,包括速度、功耗、可靠性等。速度要求是指電路的響應時間,即輸入信號變化到輸出信號變化的時間;功耗要求是指電路在正常工作時消耗的電能;可靠性要求是指電路在各種環境條件下的穩定性和抗干擾能力。

- 邏輯表達式

邏輯表達式是描述電路邏輯關系的數學表達式,通常使用布爾代數表示。在這個階段,我們需要根據需求分析的結果,將電路的功能轉化為邏輯表達式。

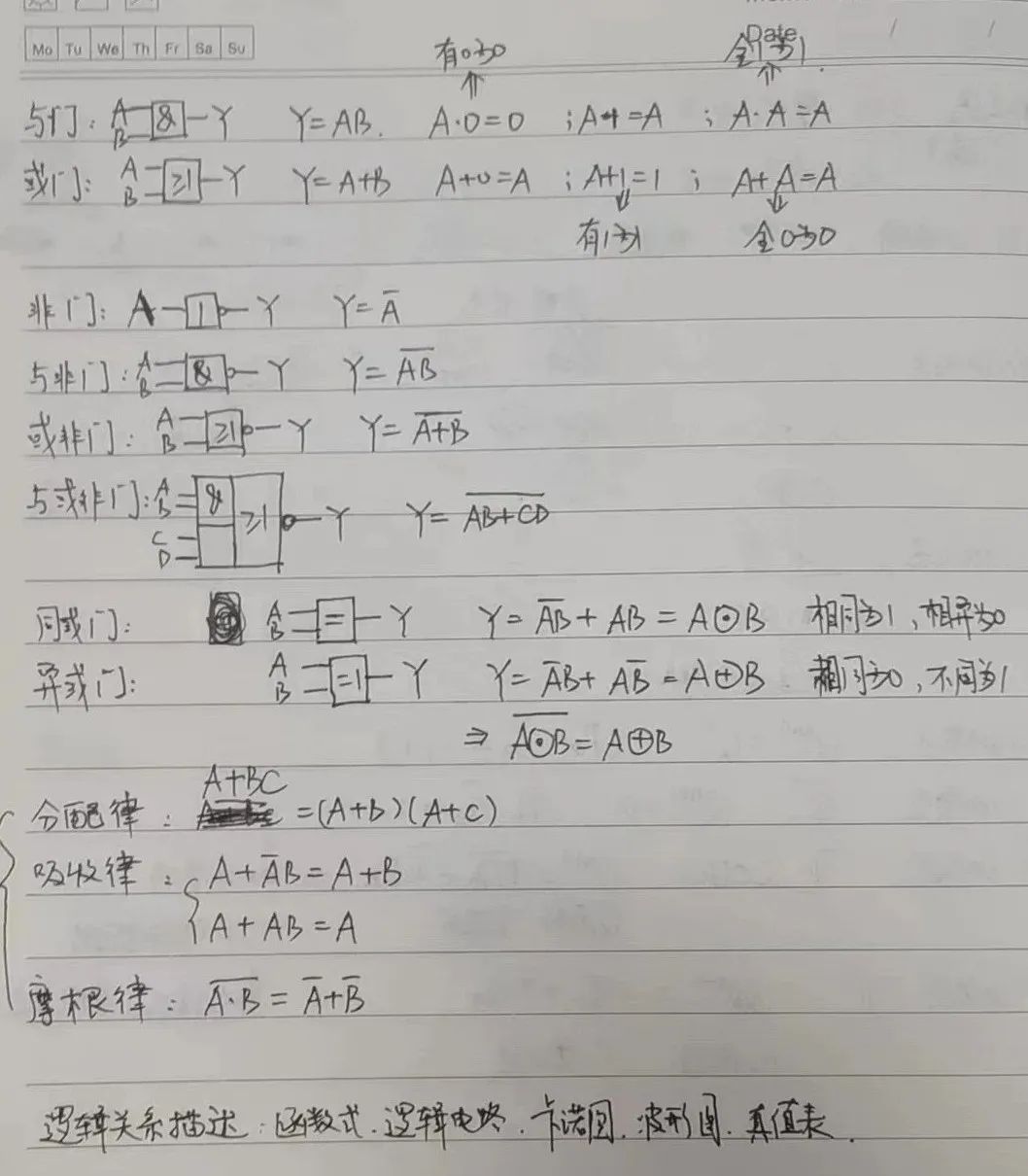

2.1 布爾代數

布爾代數是一種描述邏輯關系的數學方法,包括基本的邏輯運算符(與、或、非等)和邏輯規則(德摩根定律、分配律等)。布爾代數是設計組合邏輯電路的基礎,需要熟練掌握其基本原理和運算規則。

2.2 邏輯函數

邏輯函數是描述電路輸入輸出關系的數學表達式,通常使用布爾代數表示。根據電路的功能,我們可以將邏輯函數表示為輸入信號的函數,如F(A,B,C)。邏輯函數可以是單輸出函數,也可以是多輸出函數。

2.3 邏輯簡化

邏輯簡化是優化邏輯表達式的過程,目的是減少邏輯門的數量,降低電路的復雜度和功耗。邏輯簡化的方法包括卡諾圖法、奎因-麥克勞斯法等。在設計過程中,需要根據實際情況選擇合適的簡化方法。

- 邏輯圖

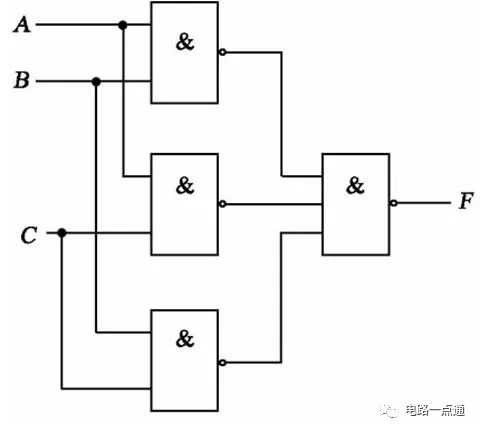

邏輯圖是描述電路結構的圖形表示,包括邏輯門、連線等。在這個階段,我們需要根據邏輯表達式,繪制出電路的邏輯圖。

3.1 邏輯門

邏輯門是實現邏輯運算的基本元件,包括與門、或門、非門等。在邏輯圖中,我們需要根據邏輯表達式,選擇合適的邏輯門,并確定它們的連接方式。

3.2 連線

連線是連接邏輯門的導線,用于傳輸信號。在邏輯圖中,我們需要合理布局連線,以減少信號傳輸的延遲和干擾。

3.3 邏輯圖繪制

邏輯圖的繪制需要遵循一定的規則和標準,如邏輯門的輸入輸出順序、連線的交叉方式等。在繪制邏輯圖時,可以使用專業的繪圖軟件,如Cadence、Altium Designer等。

- 優化

優化是提高電路性能的過程,包括速度優化、功耗優化、面積優化等。在這個階段,我們需要根據電路的實際情況,選擇合適的優化方法。

4.1 速度優化

速度優化是提高電路響應速度的過程,可以通過減少邏輯門的數量、優化連線布局等方式實現。

4.2 功耗優化

功耗優化是降低電路功耗的過程,可以通過選擇合適的邏輯門類型、優化電源管理等方式實現。

4.3 面積優化

面積優化是減小電路占用空間的過程,可以通過優化邏輯門布局、減少冗余連線等方式實現。

仿真是驗證電路設計正確性的過程,通過模擬電路的輸入輸出信號,檢查電路的功能和性能是否滿足設計要求。

5.1 仿真環境

仿真環境是進行電路仿真的軟件平臺,如ModelSim、Vivado等。在仿真環境中,我們可以設置電路的輸入信號、參數等,進行仿真測試。

5.2 仿真測試

仿真測試是模擬電路的輸入輸出信號,檢查電路的功能和性能。在仿真測試中,我們需要設置不同的輸入信號組合,觀察輸出信號的變化,以驗證電路的正確性。

-

數字電路

+關注

關注

193文章

1610瀏覽量

80707 -

數據處理

+關注

關注

0文章

607瀏覽量

28597 -

組合邏輯電路

+關注

關注

6文章

70瀏覽量

14669 -

輸入信號

+關注

關注

0文章

461瀏覽量

12586

發布評論請先 登錄

相關推薦

分析組合邏輯電路的設計步驟

分析組合邏輯電路的設計步驟

評論