機器學習和人工智能日益普及,虛擬機和虛擬組件上的工作負載也隨之不斷增加。為此,行業急需能夠確定工作負載優先次序并保障性能的機制。Compute Express Link(CXL)是處理器與加速器、內存緩沖區、智能網絡接口卡、持久存儲器和固態驅動器等設備之間的開放式行業標準互連接口。CXL基于PCIe靈活的數據帶寬提供了緩存一致性和存儲語義,同時實現比PCIe低得多的延時。

作為圖形處理單元(GPU)、通用圖形處理單元(GP-GPU)、現場可編程門陣列(FPGA)的通用設備互連,CXL采用了PCI-Express或PCIe串行接口。同時,CXL也可以用于傳統上通過DDR并行接口連接到CPU的內存。

CXL協議的新功能支持增強內存池,并且需要分布式內存管理。此外,在設備連接至虛擬機時,CXL還要求在運行時可以對設備進行動態重組和分配,從而增加了多路復用的機會,進而顯著提高了資源利用率并降低成本。

為了滿足上述要求,就需要進一步增強和部署CXL,以提供高可靠性、低延遲負載存取,增強對不同服務質量要求的適應性。

CXL 3.1規范特性

當前的CXL 3.0規范特性可總結如下:

鏈路速度最高達64 GT/s

支持CXL.IO、CXL.Cache和CXL.Mem協議

支持256B和68B FLIT

延遲優化的FLIT

反向無效Snoop

Fabric支持

IDE安全性

當前版本側重于緩存一致性和交換功能,而3.1版本解決了加速器必須保證緩存一致性訪問對等設備時的帶寬瓶頸等問題:

CXL 3.1規范特性

用于加速器的Direct P2P CXL.mem

擴展元數據

CXL fabric中的UIO直接點對點支持

GFAM擴展

可信執行環境安全協議

點對點通信

隨著CXL的發展,內存設備和I/O設備都將具備多主機功能,如此一來便可通過CXL將其部分容量動態分配給各個主機。由于多路復用的機會增加,高度可組合的設計得以高效利用資源,進而降低成本。而這有助于利用CXL技術促進共享內存、消息傳遞和點對點通信,進而加速實現分布式系統。

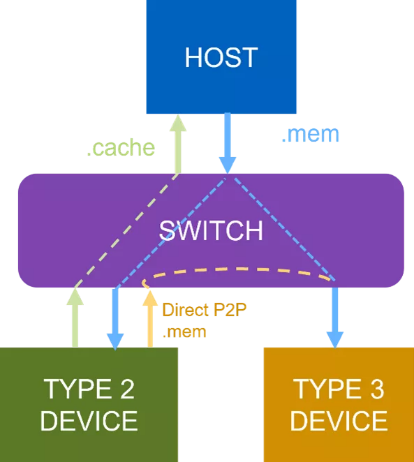

在訪問對等HDM-DB時,如果是通過主機訪問對等HDM,設備將付出高昂的代價并會犧牲帶寬。如果使用UIO(無序IO),則會犧牲一致性。CXL 3.1引入了一種新的非對稱通道來克服此類帶寬損失,從而使Type 1-2加速器能夠以完整的CXL帶寬并保證緩存一致性地訪問對等內存。

可信執行環境安全協議

CXL生態系統正不斷發展,我們需要一個機制來開發一種嚴格的方法,用于控制錯誤并管理CXL的擴展。之前提到過,我們正在設計可組合的系統,其中的組件可隨時連接到虛擬機,但這引起了對于機器或硬件安全性的擔憂。

每臺設備都需要執行相應的功能并進行加密,以便與數據中心的虛擬機交換密鑰。但這個過程可能很復雜,且存在諸多問題。

CXL 3.1引入了一種模型,專注于為直連CXL內存提供可信計算支持。直連內存是指內存設備(“目標”)和主機的CXL RP使用CXL協議進行通信,兩者之間不需要中間層。

CXL 3.1規范中的擴展元數據是什么?

元數據是通過互連來傳輸每個緩存行時所需攜帶的附加信息,不被視為數據,且存儲在緩存層次結構和內存子系統中。

例如,內存標記信息可攜帶作為緩存行的一部分。

256B FLIT模式中引入了Trailer位(最多32位),用于容納此EMD信息。

CXL 3.1規范中的UIO直接點對點支持是什么?

隨著系統的擴展,諸如CXL內存池等概念將引發本地和分布式內存管理的變革。為此,需要一種系統級方法來緩解分布式內存結構中的擁塞和故障問題。CXL標準中的QoS目前僅限于CXL.mem,且無法解決結構擁塞問題。CXL 3.1引入了一種機制,其中UIO請求者/設備可在系統擁塞時訪問另一個目標/設備。有時,CXL交換機支持將UIO訪問路由至與UIO請求者位于同一虛擬機中的HDM。

CXL 3.1驗證所面臨的挑戰

交換機拓撲層出不窮,由交換機驅動的功能也需要系統級的配置和設置。為確保傳輸功能正常運行,需對交換機行為展開驗證。其中一些行為可在事務和數據鏈路層驗證,但對于較為復雜的交換機行為,就需要在多主機和多設備環境中進行驗證。

安全功能涵蓋軟件、固件和硬件。在設計和驗證特定層的實現時,必須了解其將如何滿足整體安全要求。

3.1規范新增了許多特性,使得保持先前版本規范的向后兼容性和功能正確性變得愈加困難。但是,善加利用經過驗證的設計IP和驗證IP卻越來越重要。

新思科技CXL 3.1驗證解決方案

新思科技一直積極參與開發,并與業內領先企業保持緊密合作,致力于為最新CXL 3.1規范的功能特性和用例提供支持。

針對CXL 3.1,新思科技提供了驗證IP(VIP)、測試套件和協議解決方案,由此打造出了一套全面的協議、方法、驗證和效率功能,使開發者能夠加速實現驗證收斂。合作伙伴可利用新思科技廣泛的互連產品組合,提前對設計進行驗證。

新思科技IP使用獨立開發的VIP進行驗證,為各大公司提供出色的CXL解決方案。完整的開箱即用解決方案讓開發者能夠專注于芯片設計特性和差異化,以加快產品上市。

新思科技VIP原生集成了Verdi協議分析器調試解決方案和Verdi性能分析器。為了在SoC上運行系統級有效載荷,需要更快的、基于硬件的流片前解決方案。基于新思科技IP的事務處理器、內存模型、混合和虛擬解決方案可在業界最快的驗證硬件、ZeBu硬件加速解決方案和HAPS原型系統上實現各種驗證和驗證用例。

-

FPGA

+關注

關注

1629文章

21746瀏覽量

603757 -

新思科技

+關注

關注

5文章

798瀏覽量

50345 -

機器學習

+關注

關注

66文章

8421瀏覽量

132703

原文標題:新思科技驗證IP(VIP)如何加速驗證CXL3.1設計?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

新思科技推出全新原生汽車解決方案,高效實現和驗證功能安全機制

新思科技ZeBu Server 4仿真解決方案幫助NEC進行超級計算機驗證

什么是思科CleanAir解決方案?

新思科技發布業界首款全棧式AI驅動型EDA解決方案Synopsys.ai

新思科技發布業界首款集成化混合原型驗證解決方案

新思科技Synphony HLS解決方案

NEC使用新思科技仿真解決方案來驗證超級計算機

DesignWare CXL為SoC提供優化的多芯片IP堆棧

新思科技推出最新IC Validator物理驗證解決方案

新思CXL2.0驗證IP,加速連接新一代互聯技術

新思科技推出新一代開放標準互聯技術CXL

三星已認證新思科技PrimeLib統一庫表征和驗證解決方案

SK hynix公司使用是德科技PCIe測試解決方案驗證計算快速鏈路技術

新思科技設計、驗證和IP解決方案助力Arm全面計算戰略

新思科技PCIe 7.0驗證IP(VIP)的特性

新思科技CXL 3.1驗證解決方案

新思科技CXL 3.1驗證解決方案

評論