串口是傳感器、外設常用的接口,在低速器件中可以通過串口傳輸數據。高速復雜的器件,往往內部存在很多寄存器,這些寄存器的配置一般也是采用串口通信,可以節省IO口。

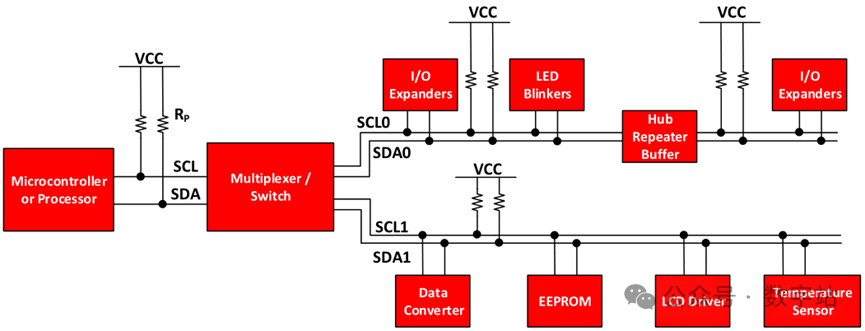

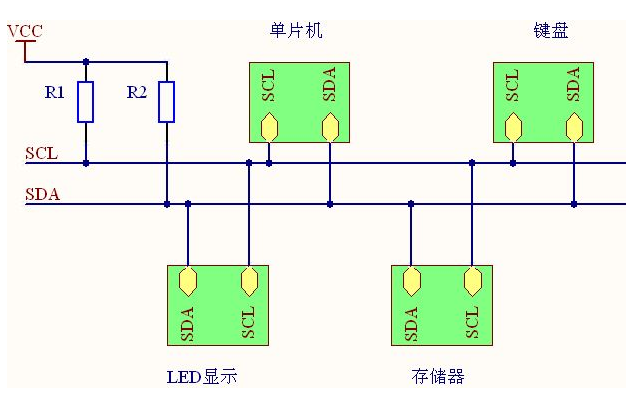

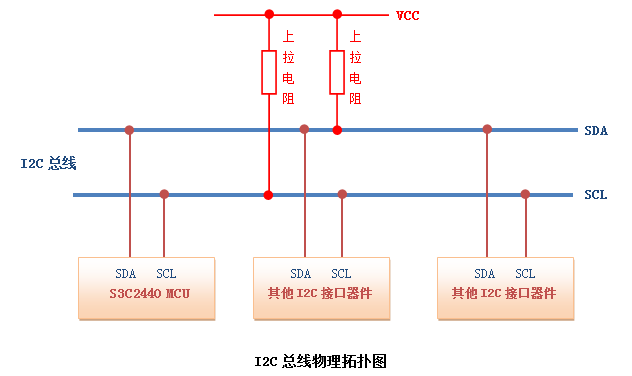

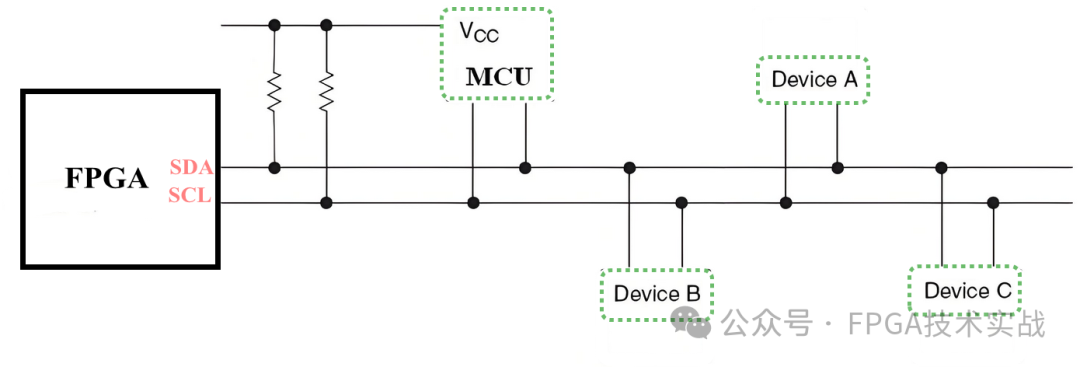

常用串口大致分為UART、IIC、SPI三種,其中IIC時序稍微復雜,卻是最好用的串行接口。如下圖所示,主機通過兩根數據線,就可以與多個外設通信。

圖1 主機控制多個外設

主機想要通過UART與N個外設雙向通信,一般需要2*N個IO口。主機想要通過SPI與N個外設雙向通信,一般需要使用N+3個IO口。而如果使用IIC接口,那么只需要2個IO口。

因此IIC對于節省IO有較大優勢,劣勢在于UART可以全雙工通信,SPI的時鐘線與數據線分開,傳輸速度最快,且UART和SPI的驅動設計一般比較簡單。而IIC由于只靠兩根線驅動多個傳感器,所以需要確認主機與哪個傳感器建立連接(傳輸器件地址),然后在對器件內部寄存器進行讀寫,導致通信速度不可能很高。

01I2C硬件接口

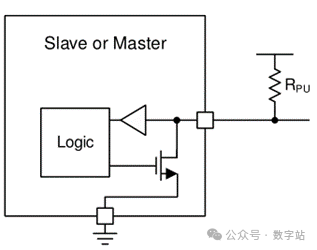

IIC主機或者從機的硬件接口如下圖所示,使用一個開漏/開集(如果是MOS管則漏極開路,如果是三極管則集電極開路)開路,在同一條線上有一個輸入緩沖區,允許數據線用于雙向傳輸數據。

圖2 IIC硬件接口

三角形代表輸入緩沖器,準確的說該接口只能通過FET輸出低電平,高電平依靠外部上拉電阻完成。

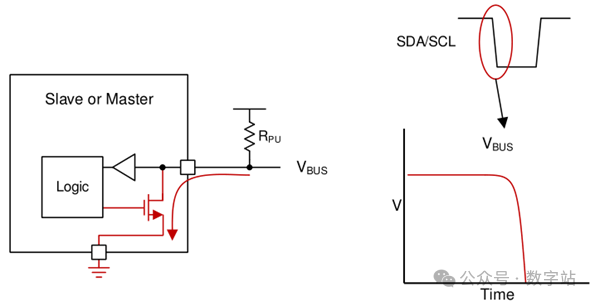

下圖是該接口輸出低電平的信號示意圖,當需要輸出低電平時,FET導通,VBUS下拉與GND連接,此時總線呈現低電平,如圖中紅色部分。

圖3 輸出低電平

圖3 輸出低電平

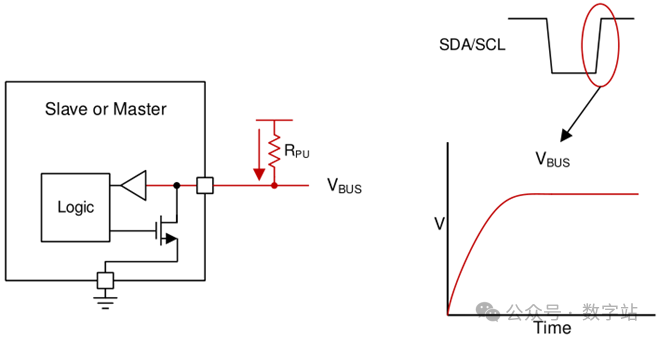

當從機或主機希望發送邏輯高電平時,只能通過關閉下拉場效應管來釋放總線。使得總線浮動,上拉電阻將把電壓拉到電壓軌,表現為高電平。

圖4 輸出高電平

02I2C通信

IIC總線是一個標準的雙向接口,除非從機已被主機尋址,否則從機不能傳輸數據。IIC總線上的每個設備都有一個特定的設備地址,以區分同一IIC總線上的其他設備。許多從設備在啟動時需要配置來設置設備的行為,通常是在主機訪問從機的內部寄存器時完成。

物理IIC接口由串行時鐘(SCL)和串行數據(SDA)線組成,SDA和SCL線路都必須通過上拉電阻連接到VCC。只有當總線空閑時才可以開始數據傳輸,如果SDA和SCL線在停止條件后都為高電平,則總線空閑。

先總體看下經典的IIC讀、寫器件寄存器時序,然后在具體分析起始位、停止位、應答、傳輸數據的SCL和SDA波形。

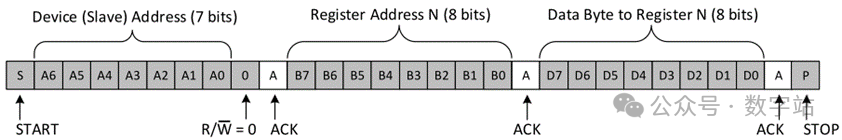

下圖是主機通過IIC寫從機寄存器數據的步驟,首先主機向從機發送起始位,然后發送7位從機器件地址,之后會發送一位讀寫操作信號,從機應答主機(ACK為低電平)后,向從機發送寄存器地址(這個寄存器地址為8位,但是有的器件可能會有16位或者24位寄存器地址,就需要發送三次這種時序)。等待從機應答之后,主機把需要寫入寄存器的數據輸出,等待從機應答后,主機發送停止條件,結束本次通信。注意不管是器件地址還是寄存器地址,亦或者是數據,都是先傳輸高位數據。

圖5 IIC主機向從機寄存器寫入數據

上圖中灰色方塊表示主機發送數據,白色表示從機發送數據。

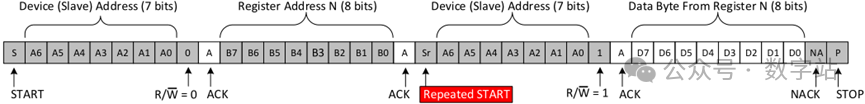

下圖是主機通過IIC讀取從機寄存器數據的步驟,主機依次向從機發送起始位、器件地址、寄存器地址,等待從機應答之后,在次向從機發送起始信號,然后發送器件地址,此時讀寫位位高電平,表示讀出數據,然后從機就會把該器件該寄存器地址的數據依次輸出,數據接收完成后,主機向從機發送不應答指令(如果發送應答指令,則從機會把下個寄存器地址的數據繼續輸出到總線上,實現連續讀取寄存器數據),然后發送停止位,完成寄存器數據的讀取。

圖6 IIC主機向從機寄存器讀出數據

圖6 IIC主機向從機寄存器讀出數據

上圖中灰色方塊表示主機發送數據,白色表示從機發送數據。

在了解了讀寫寄存器的步驟后,在來查看IIC的一些細節時序,由于主機和從機都會在時鐘SCL的高電平采集SDA的狀態,因此在傳輸數據時,SDA在SCL的低電平的時候更新數據,在SCL高電平階段盡量保持不變。

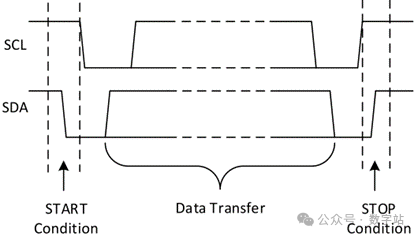

只有兩種情況,SDA會在SCL的高電平期間電平發生變化,即起始位和停止位,時序圖如下所示:

圖7 IIC通信的起始位和停止位時序圖

起始位:SCL為高電平,SDA從高電平變為低電平表示起始位(因為空閑時SDA是高電平,SDA變為低電平代表開始傳輸數據)。

停止位:SCL為高電平時,SDA從低電平變為高電平表示停止位。

重復起始條件(圖6中紅色字體的時序):時序與起始條件一樣,用于代替連續的停止然后開始條件。當總線未空閑時,主機希望啟動新的通信,但不希望發送停止信號釋放總線,就可以直接發送重復起始條件,開啟信號通信。因為停止條件有可能使主機失去對總線的控制(在多主機環境中)。

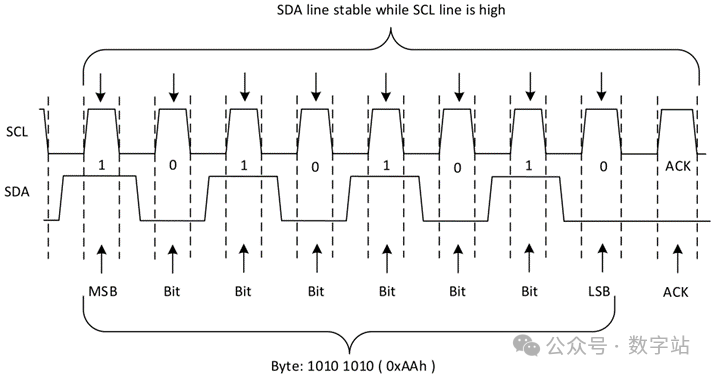

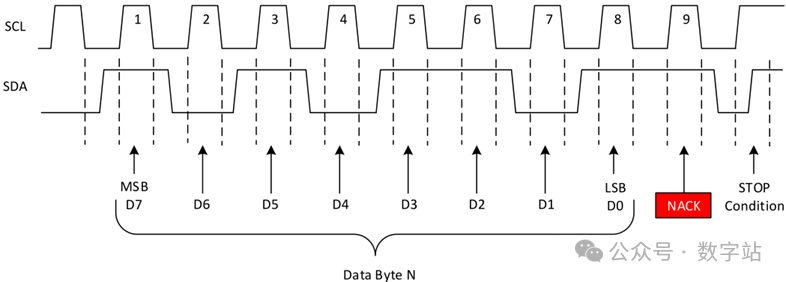

如圖8所示,在SCL的每個時鐘脈沖期間傳輸一個數據位,每次傳輸8位數據后需要從機應。8位數據可以是設備地址、寄存器地址,也可以是寫入或讀取從機的數據。

數據首先傳輸最高有效位(MSB)。在START和STOP條件之間,可以將任意字節的數據從主機傳輸到從機。在傳輸數據過程中SDA必須在SCL低電平時更新狀態,在SCL為高電平時SDA線上的數據必須保持穩定,因為當SCL高時,SDA的變化被解釋為控制命令(START或STOP)。

圖8 單字節數據傳輸時序圖

每個字節(包括地址字節)后面都有一個來自接收方的ACK位,ACK位允許接收方與發送方通信,表明該字節已成功接收,并且可以發送下一個字節數據。

在接收方發送ACK之前,發送方必須釋放SDA線。如下圖9所示,為了發送ACK位,接收方需要在ACK/NACK相關時鐘周期(周期9)的低電平期間拉低SDA線,使SDA線在ACK/ NACK相關時鐘周期的高相位穩定在低電平。設置和保持時間必須考慮在內。

圖9 NACK波形

當SDA在與ACK/NACK相關的時鐘周期內保持高位時,則不應答(NACK)。有幾個條件會導致NACK的產生:

從機無法接收或發送,因為它正在執行一些實時功能,還沒有準備好開始與主機通信。

在傳輸過程中,接收方接收到它不理解的數據或命令。

在傳輸過程中,接收方不能再接收任何數據字節。

主機讀取從機寄存器數據后,通過NACK表示終止從機寄存器數據的讀取。

03總結

IIC接口是開漏/開集輸出的硬件接口,只能主動輸出低電平。當需要輸出高電平時,會釋放總線(對外表現高阻態),被外部上拉電阻上拉到VCC,從而實現高電平,所以上拉電阻必須存在。

SDA在傳輸數據時只能在SCL的低電平期間變化,如果SCL為高電平,SDA從高電平變為低電平,則表示起始位或者重復起始位,SDA從低電平變為高電平則便是停止位。

每當傳輸一字節數據后,接收方需要產生一個應答位(ACK低電平表示應答),之后發送方才能傳輸下一字節數據。

在起始位和停止位之間,可以傳輸任意字節數據,數據可以是器件地址、寄存器地址、寫入或讀取從機的數據。

上述的總結來自于TI的IIC總線手冊,需要該手冊的可以在公眾號后臺回復“I2C手冊”(不包括引號)。

聲明:本文轉載自數字站公眾號

-

傳感器

+關注

關注

2552文章

51274瀏覽量

755048 -

寄存器

+關注

關注

31文章

5358瀏覽量

120773 -

I2C

+關注

關注

28文章

1491瀏覽量

124080 -

串口

+關注

關注

14文章

1557瀏覽量

76712 -

IIC總線

+關注

關注

1文章

66瀏覽量

20330

原文標題:I2C基礎協議詳解

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

I2C總線協議的基礎知識

I2C總線協議及其應用

i2c總線相關知識

I2C總線協議的基礎知識資料總結免費下載

I2C總線協議的基礎知識

I2C總線協議的基礎知識

評論