本節介紹的AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

書上講的AXI比較具體,本節呢不打算落入俗套,從應用角度解釋AXI。如果需要深入研究AXI時序,那完全可以從 ?topic=/com.arm.doc.set.amba/ind.。。 下載最權威的規格書,而不是通過別人寫的書來獲得這些內容(要學習一手材料,不要別人嚼過的)。

Zynq是以ARM作為核心的,運行時也是第一個“醒”過來,然后找可執行代碼,找到后進入FSBL(第一引導階段),接著找配置邏輯部分的bit文件,找到后就叫醒PL按照bit中的方式運行,再接著找可執行代碼,進入SSBL(第二引導階段),這時就可以初始化操作系統的運行環境,引導像Linux這樣的大型程序,隨后將控制權交給Linux。Linux運行時可以跟PL進行數據交互。注意了,就在這時候,數據交互的通路,就是我們本節要講的AXI總線。

說白了,AXI就是負責ARM與FPGA之間通信的專用數據通道。

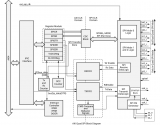

ARM內部用硬件實現了AXI總線協議,包括9個物理接口,分別為AXI-GP0~AXI-GP3,AXI-HP0~AXI-HP3,AXI-ACP接口。如下圖黃圈所示。

可以看到,只有兩個AXI-GP是Master Port,即主機接口,其余7個口都是Slave Port(從機接口)。主機接口具有發起讀寫的權限,ARM可以利用兩個AXI-GP主機接口主動訪問PL邏輯,其實就是把PL映射到某個地址,讀寫PL寄存器如同在讀寫自己的存儲器。其余從機接口就屬于被動接口,接受來自PL的讀寫,逆來順受。

這9個AXI接口性能也是不同的。GP接口是32位的低性能接口,理論帶寬600MB/s,而HP和ACP接口為64位高性能接口,理論帶寬1200MB/s。

有人會問,為什么高性能接口不做成主機接口呢?這樣可以由ARM發起高速數據傳輸。答案是高性能接口根本不需要ARM CPU來負責數據搬移,真正的搬運工是位于PL中的DMA控制器。

位于PS端的ARM直接有硬件支持AXI接口,而PL則需要使用邏輯實現相應的AXI協議。Xilinx提供現成IP如AXI-DMA,AXI-GPIO,AXI-Datamover都實現了相應的接口,使用時直接從XPS的IP列表中添加即可實現相應的功能。

有時,用戶需要開發自己定義的IP同PS進行通信,這時可以利用XPS向導生成對應的IP。xps中用戶自定義IP核可以擁有AXI-Lite,AXI4,AXI-Stream,PLB和FSL這些接口。

后兩種由于ARM這一端不支持,所以不用。

AXI-Lite具有輕量級,結構簡單的特點,適合小批量數據、簡單控制場合。不支持批量傳輸,讀寫時一次只能讀寫一個字(32bit)。

AXI4接口和AXI-Lite差不多,只是增加了一項功能就是批量傳輸,可以連續對一片地址進行一次性讀寫。

上面兩種均采用內存映射控制方式,即ARM將用戶自定義IP編入某一地址進行訪問,讀寫時就像在讀寫自己的片內RAM,編程也很方便,開發難度較低。代價就是資源占用過多,需要額外的讀地址線、寫地址線、讀數據線、寫數據線、寫應答線這些信號線。

另外一種AXI接口就是AXI-Stream,這是一種連續流接口,不需要地址線(很像FIFO,一直讀或一直寫就行)。對于這類IP,ARM不能通過上面的內存映射方式控制(FIFO根本沒有地址的概念),必須有一個轉換裝置,例如AXI-DMA模塊來實現內存映射到流式接口的轉換。AXI-Stream適用的場合有很多:視頻流處理;通信協議轉換;數字信號處理;無線通信等。其本質都是針對數值流構建的數據通路,從信源(例如ARM內存、DMA、無線接收前端等)到信宿(例如HDMI顯示器、音頻輸出等)構建起連續的數據流。這種接口適合做實時信號處理。

有了上面的這些官方IP和向導生成的自定義IP,用戶其實不需要對AXI時序了解太多(除非確實遇到問題),因為Xilinx已經將和AXI時序有關的細節都封裝起來,用戶只需要關注自己的邏輯實現即可。

-

AXI

+關注

關注

1文章

127瀏覽量

16631

發布評論請先 登錄

相關推薦

AXI VIP設計示例 AXI接口傳輸分析

怎么使用AXI CDMA從OCM/DDR寫入BRAM

AXI接口協議詳解

一文詳解ZYNQ中的DMA與AXI4總線

你必須了解的AXI總線詳解

怎么樣利用AXI Quad SPI快速打通Linux至PL端SPI從設備?

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI學習路線,從握手協議開始

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

從應用角度詳解什么是AXI

從應用角度詳解什么是AXI

評論