【序文】

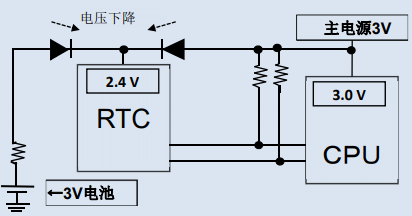

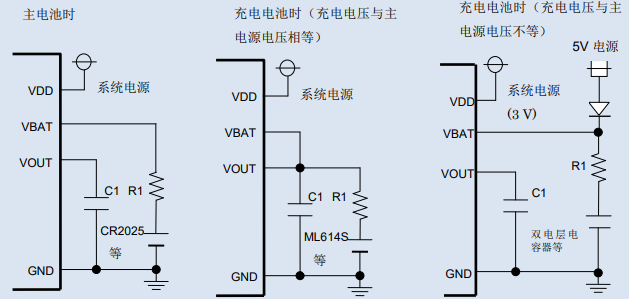

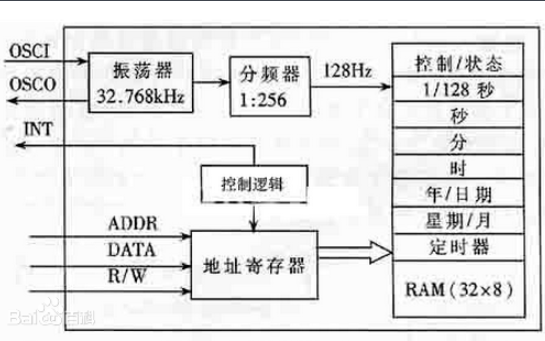

通常,實時時鐘必須隨石英晶體振蕩頻率而隨時更新日歷數據和時間數據。為此,需要使用備用電池保護數據以應對主電源的切斷及停電。在這種電池備用電路中,主電源和電池的轉換需在適當時間內進行。部分系統為此采用了專用的電源管理 LSI,而大部分系統為追求簡便則采用由兩只二極管構成的或門電路【圖 1】。在此解說這種二極管或門電路特有的技術性課題。

【1】電池能量損耗

考慮二極管所造成的損耗時可列舉出兩大特性。其一是正向壓降(VF)特性,另一項是反向泄漏電流(IR)特性。一般情況下所產生的 VF為 0.6V 左右,當主電源為 3.0V 時,通過二極管后的電壓為 2.4V。這種電壓下降意味著向充電電池和雙電層電容器(以下稱為“電容器”)等充電的電壓下降。結果有可能導致電池充電電壓下降而縮短其壽命。

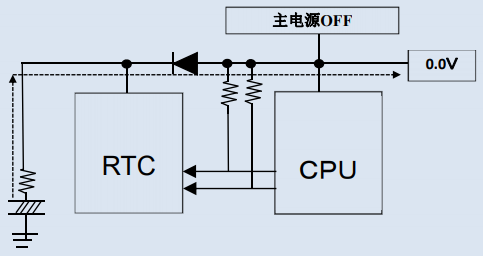

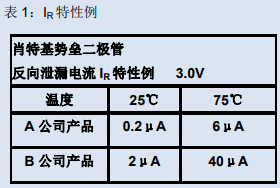

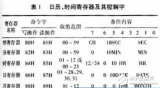

由于上述原因,不少技術人員選擇使用 VF 較小的肖特基勢壘二極管。肖特基勢壘二極管的結構特征導致其 VF 量小,各家公司均推出了這項產品。但是,通常 VF和 IR之間為二律背反的關系,即 VF小的二極管的 IR大。IR的增大將在切斷主電源時引發問題。切斷主電源后,泄漏電流從電池流向電壓為 0V 的電源。這正是被稱為反向泄漏的理由(圖 2)。而且,IR具有溫度特性,溫度越高越呈現二次方增長的趨勢(表 1)。由于上述背景,設計人員需要根據所開發產品的溫度規格范圍并考慮到 VF和 IR選擇最為均衡的二極管,但實際上很難找到所有條件均與系統要求相匹配的二極管(圖 2)。

【2】時鐘數據受損風險

在前一項中已經說明了因二極管的 VF而使 CPU 和實時時鐘的電源電壓之間出現電位差。若 CPU 在這種狀態下訪問實時時鐘,來自 CPU 的輸入電壓有可能超過實時時鐘的額定輸入電壓。超過額定數值后,一般的 CMOS 工藝半導體產品不少會出現內部寄存器位數無規則變化的現象。額定輸入除了適用于輸入接口以外,時鐘輸出的使能輸入以及 CMOS 時鐘輸出端子的上拉對象也可能適用同樣的額定輸入電壓,因此需要進行充分的確認。CMOS 半導體產品的輸入最大額定值一般在 VDD+0.3V 以下。這時需把二極管的 VF 控制在 0.3V 以內,所以必然將選擇使用肖特基勢壘二極管。這就產生了前項所提到的 IR的問題(圖 2)。

圖 1:通常使用二極管或門電路的電源開關電路

圖 2:切斷主電源時因 IR所造成的泄漏(虛線)

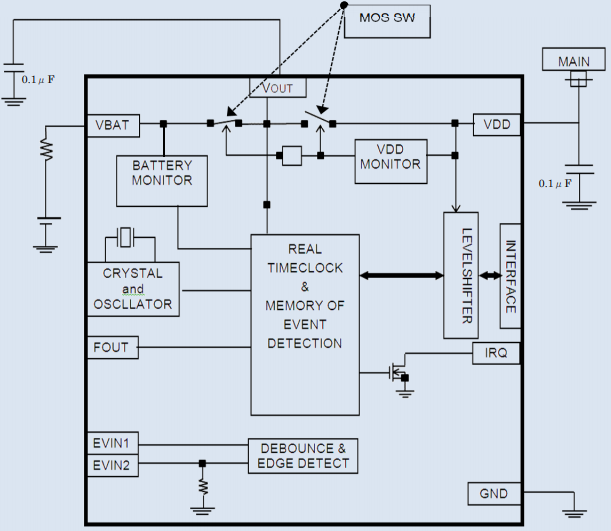

【3】RX-8035/435 中搭載的電源開關電路

本電源開關電路是針對上述二極管或門電源開關電路的設計風險而提供的解決方案。開關元件中沒有使用晶體管或二極管,而采用了 PMOS 的開關。VF被控制在 0.12V 以內,通常狀態下的 IR在 30nA 以下。實時時鐘以外必須準備的電子部品僅為連接 VDD和 VOUT端子的 0.1μF 旁路電容器共計兩只而已。

以下介紹原電池、二次電池和雙電層電容器的連接方法。

-

芯片

+關注

關注

455文章

50812瀏覽量

423581 -

實時時鐘

+關注

關注

4文章

245瀏覽量

65781 -

供電電源

+關注

關注

0文章

62瀏覽量

16359

發布評論請先 登錄

相關推薦

實時時鐘芯片DS3231應用筆記,使用指南,FAQ全集

介紹一款低功耗小體積的實時時鐘芯片

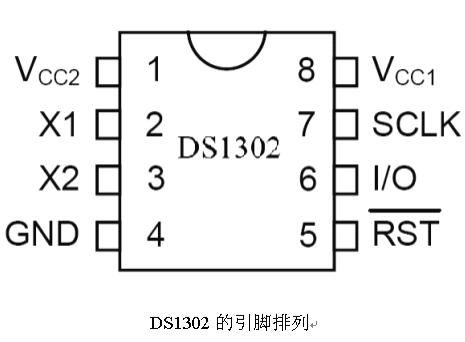

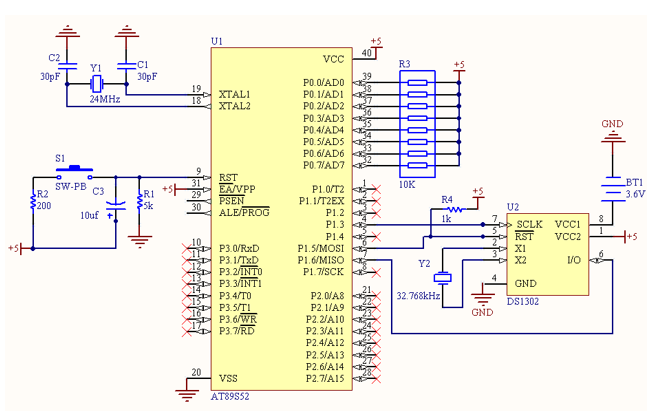

DS1302實時時鐘芯片原理圖分享

NuMicro? 家族中那些系列的芯片支持實時時鐘(RTC)控制器?

實時時鐘芯片DS1302應用資料

基于實時時鐘芯片X1228的電源控制器設計

實時時鐘芯片應用

實時時鐘芯片DS12887原理

實時時鐘芯片的應用資料詳細說明

實時時鐘芯片M41T62主要特性介紹

實時時鐘芯片應用技術(針對芯片供電電源切換問題的解決方案)

實時時鐘芯片應用技術(針對芯片供電電源切換問題的解決方案)

評論