改變企業命運的前沿技術

本期Kiwi Talks 將講述Chiplet技術是如何改變了一家企業的命運并逐步實現在高性能計算與數據中心領域的復興。

當我們勇于承擔可控的風險、積極尋求改變世界的前沿技術時,AMD 才會越來越好。

——AMD 董事會主席及首席執行官 Lisa Su 博士

開端:Why Chiplet?

2017年對于AMD公司來說是一個非常關鍵的轉折點。在那之前的10年,AMD都面臨著強勁的競爭對手,糟糕的財務負擔。 那一年AMD實現了突破式的創新,以全新的Chiplet架構誕生 EPYC第一代處理器,標志著AMD在高性能計算領域的復興,也是其在服務器市場上的重要里程碑。

回顧2017年,Global Foundries 從AMD剝離,這意味著公司從一家擁有晶圓廠的公司變成芯片設計公司。

在被問及是否因為晶圓協議才被迫選擇Chiplet賽道時,首席執行官Lisa Su回應的答案:“完全不是,我們當時的想法是,我們需要為處理器市場帶來一些與眾不同的東西,因此制造這些良率不高、價格昂貴的巨型芯片并不是大家想要的答案。”

source:ieeetv

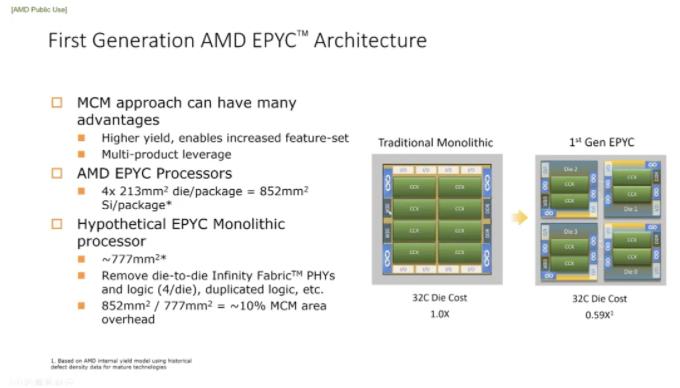

第一代EPYC Zen-1架構的服務器產品是由4個同樣結構的Die(都含有計算核、DDR內存和I/O功能,I/O主要包括PCIe、以太網、CPU片間互連等)通過 IFOP(Infinity Fabric on Package,一種片內互連物理層技術)相連而成。 雖然當時AMD的Chiplet設計取得商業化成功,提升了CPU的市場份額,但Chiplet的技術發展一直面臨著各種挑戰。誠然,第一代產品整體的設計與制造降低了成本,采用的2D MCM設計改善了產品性能并增加了靈活性,然而增加芯片數目確會導致更大的片上系統(soc),由于組件之間的距離變大,導致了產品性能的延遲。

在7,8年前,要尋找到最合適的連接小芯片的封裝技術也同樣面臨難題。這是一個復雜的等式,涉及成本、性能、帶寬密度、功耗和制造能力。

在當時,大批量、低成本地生產它們和擁有封裝工藝技術是兩碼事。為了堅持Chiplet的道路,AMD在制造工藝方面投入了大量的資金。

同年,NVIDIA創始人兼CEO黃仁勛在2017年Computex發布了 Tesla V100,號稱是當年史上最強的GPU加速器。雖然 Tesla V100 在性能上極其優秀,但仍存在不少缺點。比如芯片面積過大——高達 815 平方毫米,而過大的芯片面積,加上英偉達在該款芯片上巨額的研發投入(約30億美金)直接導致 Tesla V100 的價格異常昂貴,售價高達 14.9 萬美元。如此高的售價讓很多用戶望而卻步。 這也印證了隨著芯片面積的增大,制造成本越發昂貴,后續行業紛紛為了實現降本都轉向了Chiplet的設計架構。

進階:I/O Die架構的誕生

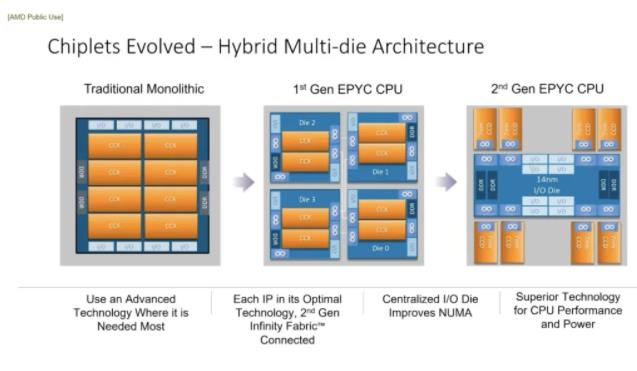

Central I/O Die 的架構,成功地提高處理器性能的同時,也提供了更高的能效比和更好的成本效益。

2018年AMD發布了下一代Zen 2 EPYC CPU。Zen 2架構的EPYC Rome 包括8個CCD(Core Chiplet Die)和1個IOD(I/O Die),CCD中包括CPU核心、緩存,后者包括各類控制器和輸入輸出處理器使,通過Infinity Fabric技術實現Chiplet之間的高速連接,從而構建出具有大量核心的高性能處理器。這種設計允許每個核心芯片擁有獨立的L3緩存,并且可以獨立地進行性能擴展和優化。

source:ieeetv

AMD后續推出的Zen3和Zen 4 EPYC CPU均沿用了I/O Die 的架構,成功地在提高處理器性能的同時,也提供了更高的能效比和更好的成本效益。

AMD的Zen3/ Zen4架構CPU,采用CCD(compute)和CIOD(memory interface + I/O)組合的形式進行不同Chiplets功能拆解。AMD Zen 4 EPYC 采用12個CDD+1個IO Die的方式,每個CDD包含12個核心,從而讓其達到了96核心的設計。

目前,IO Die架構逐步成為Chiplet主流的一種形態被應用。例如Huawei Lego架構采用的是compute die(compute + memory interface)和I/O die組合的形式,不同的Chiplets的數量和組合形式都可以靈活搭配,從而組合出多種不同規格的云端高性能處理器產品。

奇異摩爾作為國內首批自研I/O Die互聯芯粒的公司,其2.5D通用IO Die互聯芯粒集成了如D2DDDRPCIeCXL等大量存儲、互聯接口,最高可以支持10+Chiplets,提供更好的性能、更高的帶寬、更低的延遲及功耗,構建全球領先的一流算力平臺。

復興:高性能計算和數據中心市場

“我們非常重視高性能計算和人工智能的 GPU 發展。實際上,這可能是我們開啟的一個非常重要的弧線,我們一直都在研究 GPU,這是下一個重大機遇。AMD的chiplet 策略可以構建一個高度模塊化的系統,可稱之為集成的 CPU 和 GPU,或者說它更像是實現了人們需要的令人難以置信的 GPU 功能。”Lisa Su在接受外媒訪談時表示。

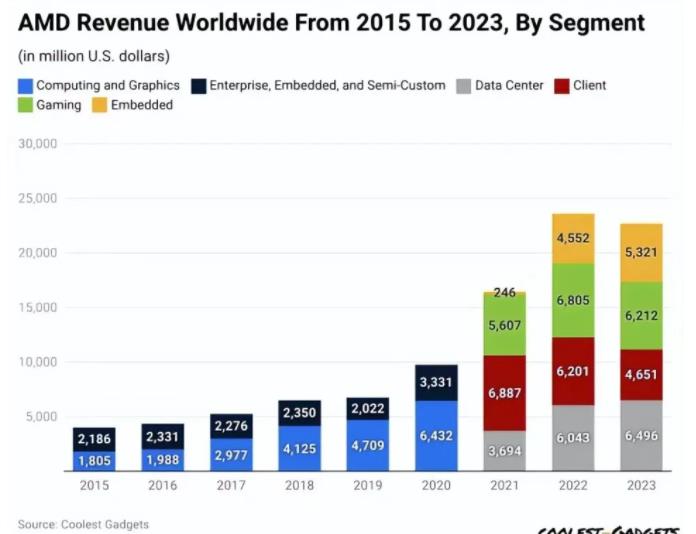

正如Lisa描述的一樣,AMD這幾年聚焦于HPC和數據中心并交出了斐然的成績單。2020年, AMD官宣推出Instinct MI 100 加速卡全面進軍高性能計算領域。在接下來的幾年中,AMD不斷升級其AI加速卡的性能。

圖:2023年Datacetner已經成為AMD全球收入來源最大的板塊

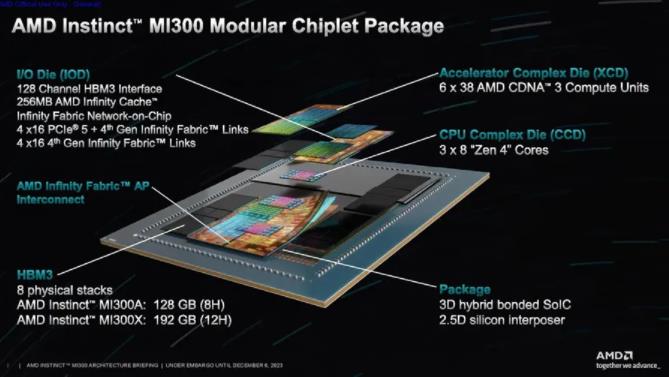

2023年,AMD又推出了高性能GPU加速卡即Instinct MI300. Lisa 坦言AMD將AI視為第一戰略重點,AI存在大量的市場機會,而最大機遇來自數據中心。MI300系列已成為AMD歷史上收入增長最快的產品。Instinct MI300 是 AMD 建立未來數據中心/ HPC級APU 的重要布局,結合了 AMD 的 CPU 和 GPU 技術的優點。

值得注意的是,AMD從Zen3 架構開始就實現了3D fabric封裝工藝,而I/O die作為系統基礎設施的一部分,通過AMD Infinity Fabric技術與其他芯片進行互連,發揮著關鍵作用。在某些配置中,例如頂配版本,可能會包含4個I/O die,它們基于6nm工藝制造,并且可能包含I/O控制器、IP塊以及可能的緩存。

3D Base die(可理解為基于3D封裝的I/O Die)較2.5D IO die面積更大,除了IO die中的互聯模塊,還可以把原本集成在SoC中的Power、SRAM、I/O等非數字功能模塊拆分并拼搭進去,從而構成一個高度集成并節能的多核異構計算架構,同時實現上層的邏輯芯片面積最大化和芯片單位面積的最小化。在互聯方面,3D Base die支持水平方向和垂直方向的異構芯片互連。垂直方向,通過TSV、microbump等3D互連技術與頂層邏輯芯粒、substrate垂直通信,從而以最小限度實現die與die之間的互連、片外連接,顯著提高芯粒集成密度。

“

Kiwi Base Die 是奇異摩爾基于Chiplet及3D IC架構所自研的基礎互聯芯粒。Kiwi Base Die 以高性能片上網絡Kiwi Fabric 為互聯核心,整合了PCle、HBM等高速互聯接口,并搭配大容量的片上近存,可實現高效的片內數據傳輸調度與存儲。客戶可將其他功能單元垂直堆疊在Kiwi Base Die之上,通過 3D Die2Die 接口實現芯粒間的高速互聯。

突破解耦:開源的芯世界

AMD Lisa Su在采訪中表明“ 如果你看看今天的半導體行業,你會發現我們和競爭對手既有競爭的地方,也有合作的地方。行業沒有一種萬能的解決方案,因此模塊化和開放性將允許生態系統在他們想要創新的地方進行創新。所以,比如英特爾,我們確實在某些領域競爭,但我們也在某些領域合作。英特爾是 UALink 聯盟的一部分,他們也是超級以太網聯盟UEC的一部分。”

AMD作為領先的國際芯片公司,倡導行業的開放開源,通過聯合生態伙伴建立國際互聯標準。

“目前國內的Chiplet生態處于‘半開放生態’;一是大量產品開始采用Chiplet技術,二是行業中誕生了一些專門從事Chiplet的企業,無論是提供特定芯粒,還是將已有芯片產品中的某些功能模塊(芯粒)單獨分離出來,以獨立的Chiplet形式提供給其他企業使用。奇異摩爾就在此列。”奇異摩爾聯合創始人兼產品和解決方案副總裁祝俊東此前在接受第一財經采訪時提及。

未來科技還會出現很多有夢想有堅持的企業如奇異摩爾,依托Chiplet架構,不斷探索下一代高性能計算及AI網絡的互聯芯粒技術。

寫在最后

摩爾在其 1965 年關于芯片、晶體管以及芯片設計未來的開創性論文中寫道,他最終能夠預見到芯片制造商將芯片分解成更小的部分,以使它們更容易制造。這也是半導體鼻祖對于未來芯片架構的一個神奇的預測,也將預示行業對Chiplet技術賦予厚望,從而創造一個更簡單、更開源的芯世界。

-

amd

+關注

關注

25文章

5531瀏覽量

135290 -

服務器

+關注

關注

12文章

9518瀏覽量

86730 -

高性能計算

+關注

關注

0文章

84瀏覽量

13543 -

chiplet

+關注

關注

6文章

444瀏覽量

12735 -

奇異摩爾

+關注

關注

0文章

52瀏覽量

3599

原文標題:Kiwi Talks | 突破與解耦:Chiplet技術讓AMD實現高性能計算與服務器領域復興

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論