十多年來,Cadence 對 PCIe 技術(shù)的堅定承諾和支持,在業(yè)界有目共睹。我們深知強大 PCIe 生態(tài)系統(tǒng)的重要性,并感謝 PCI-SIG 提供的平臺。在 PCI-SIG 開發(fā)者大會迎來 32 周年之際,Cadence 宣布面向 HPC/AI 市場推出完整的 PCIe 7.0 IP 解決方案。

▋ PCIe 標準為何如此重要?

從 GPIO 等最簡單的構(gòu)建塊到最先進的高速接口,IP 子系統(tǒng)是整個芯片制造生態(tài)系統(tǒng)的命脈。而推動 IP 發(fā)展的一個關(guān)鍵因素便是工業(yè)界和學術(shù)界在接口標準和協(xié)議制定上的合作。PCI-SIG 引領(lǐng)了一些關(guān)鍵定義和合規(guī)規(guī)范的制定,并確保了接口 IP 的互操作性。

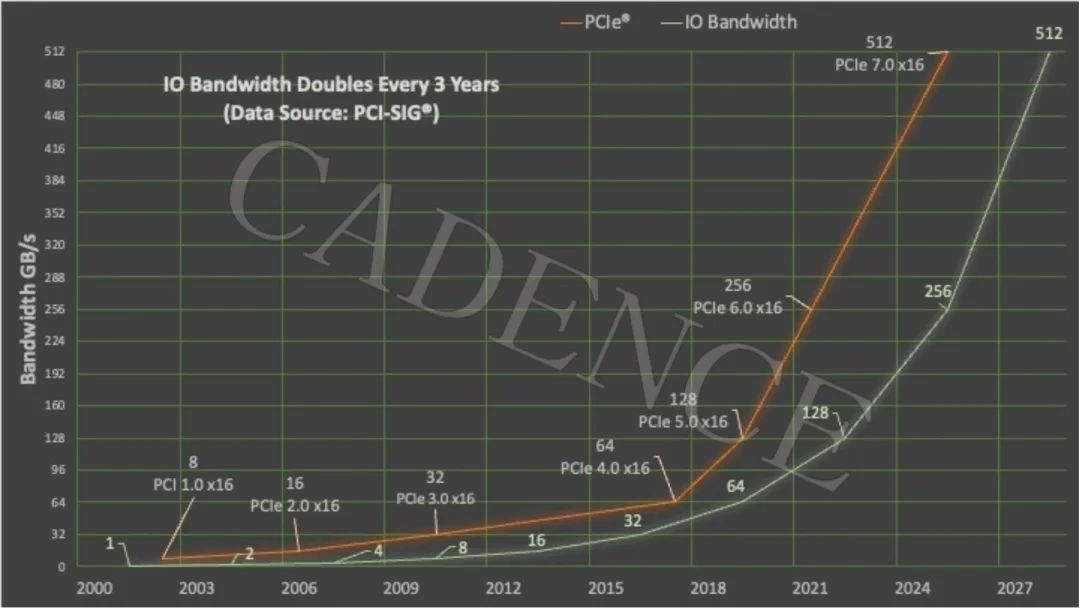

HPC/AI 市場不斷要求高吞吐量、低延遲和低功耗,這推動著技術(shù)的進步,促使 PCIe 技術(shù)持續(xù)發(fā)展,可服務(wù)于未來幾代。作為 PCI-SIG 的成員,Cadence 能夠盡早獲知規(guī)范的變化和最新合規(guī)標準等重要信息。PCIe 7.0 及更高規(guī)范將助推市場不斷擴展,而我們期待幫助我們的客戶使用 Cadence IP 解決方案構(gòu)建一流的尖端 SoC。

圖 1:PCIe 數(shù)據(jù)傳輸速率變化(來源:PCI-SIG)

▋ 今年的開發(fā)者大會有何新看點?

在 2024 開發(fā)者大會上,PICe 7.0 標準成為焦點,Cadence 今年展示了面向 PCI 7.0 的一整套 IP 子系統(tǒng)解決方案。

▋ Cadence 有何與眾不同之處?

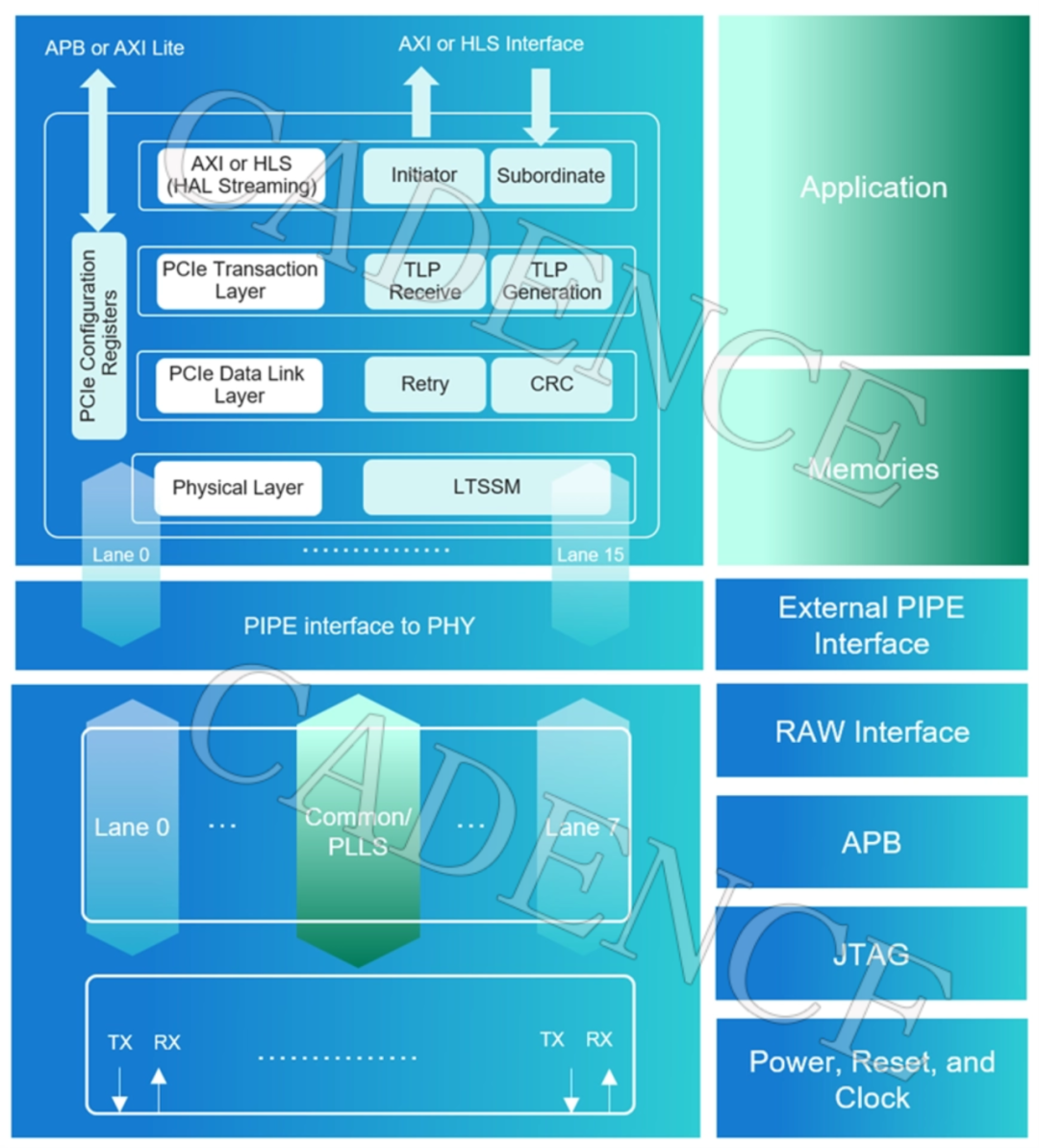

Cadence 始終堅持為測試芯片構(gòu)建一個完整的子系統(tǒng),包括 8 通道 PHY 和一個完整的 8 通道控制器。在測試芯片中添加一個控制器,可以顯著提高特性分析和壓力測試的效率和粒度,同時使我們能夠展示與真實系統(tǒng)的互操作性。此外,我們還可以將整個協(xié)議棧作為一個 8 通道的解決方案進行測試,其中涵蓋客戶實際使用的諸多應(yīng)用。這種方法能夠幫助客戶大大降低 SoC 設(shè)計相關(guān)風險。

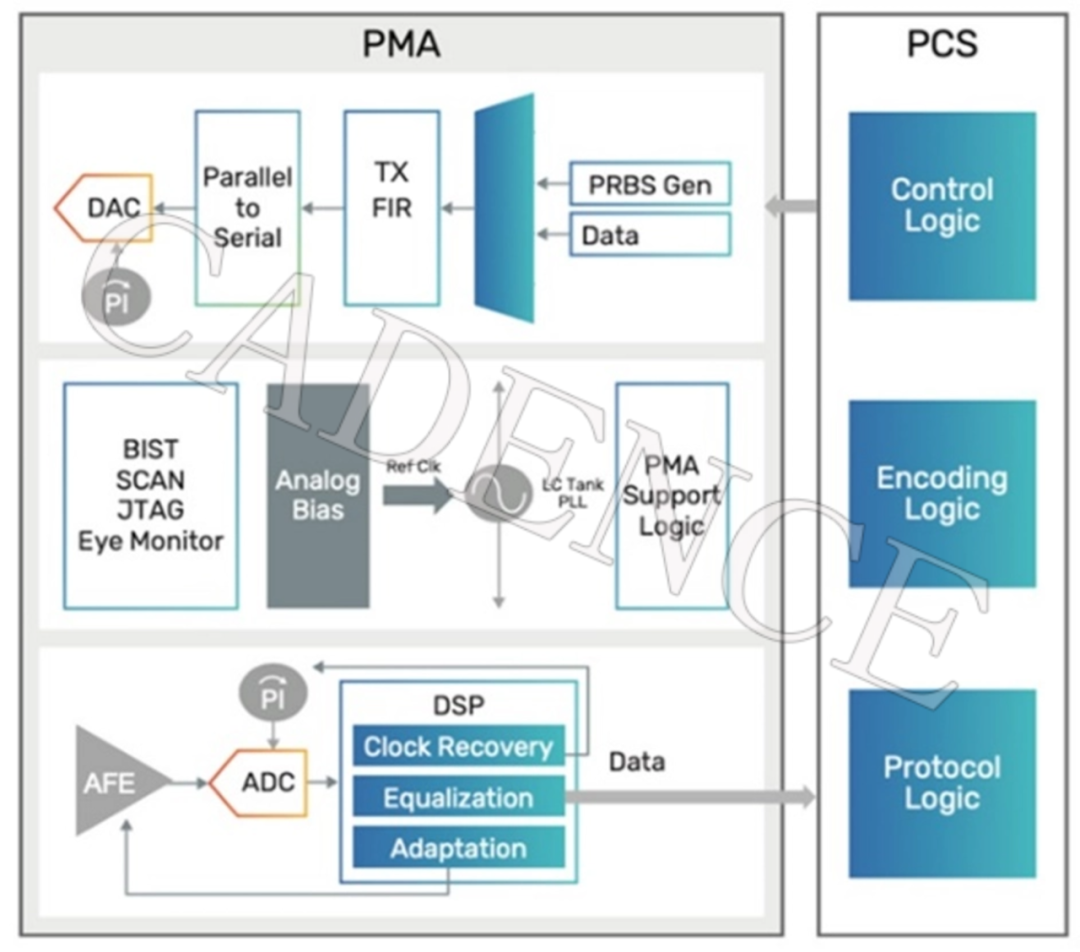

圖 2:Piper——Cadence 面向 PCIe 7.0 的 PHY IP

圖 3:業(yè)界首款面向 PCIe 7.0 的 IP 子系統(tǒng)

這適用于哪個市場?

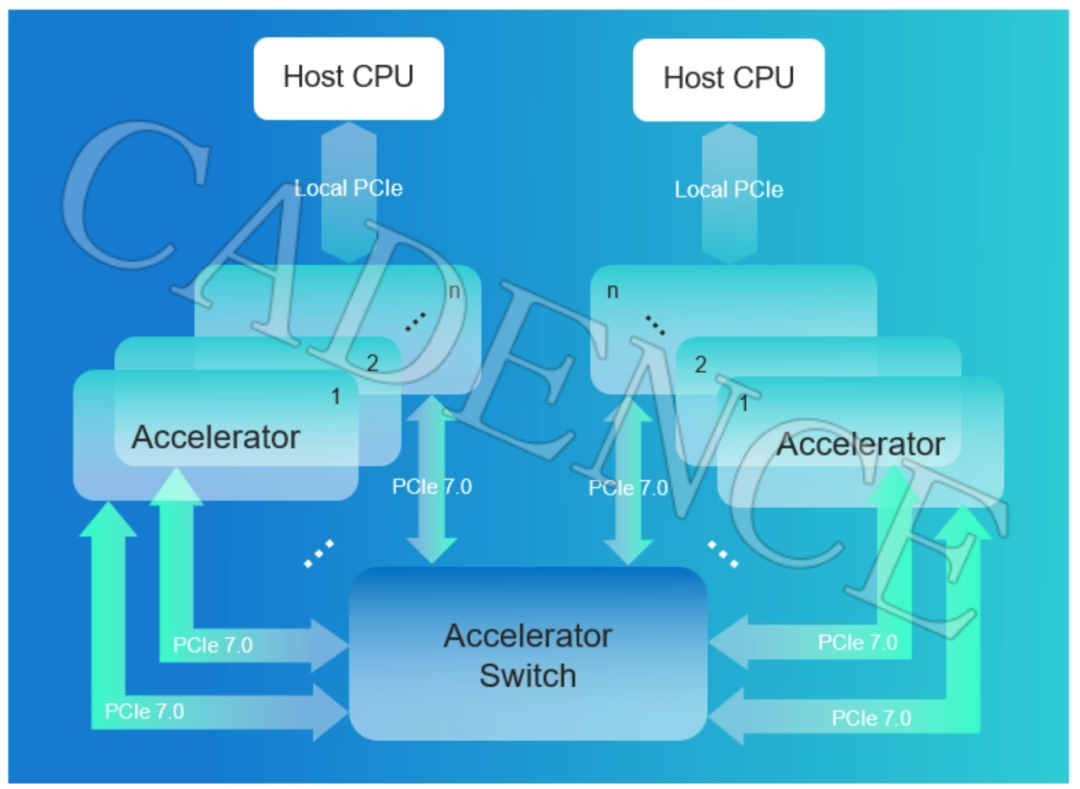

如今,加速計算已成為主流,PCIe 鏈路在系統(tǒng)中的作用隨之愈發(fā)凸顯。在服務(wù)器或計算集群內(nèi),要跨多個圖形處理器(GPU)或加速器擴展復(fù)雜的計算任務(wù),實現(xiàn) GPU 之間的直接通信至關(guān)重要。業(yè)內(nèi)逐漸認識到,要實現(xiàn)高性能計算,需要可擴展的開放式架構(gòu)。隨著 AI 和數(shù)據(jù)密集型應(yīng)用的發(fā)展,對這種技術(shù)的需求可能增加,因此 PCIe 7.0 將成為下一代接口 IP 的關(guān)鍵部分。

下圖展示了 PCIe 7.0 的潛在用例。

圖 4:PCIe 7.0 用例

▋ 光纖鏈路為何如此重要?

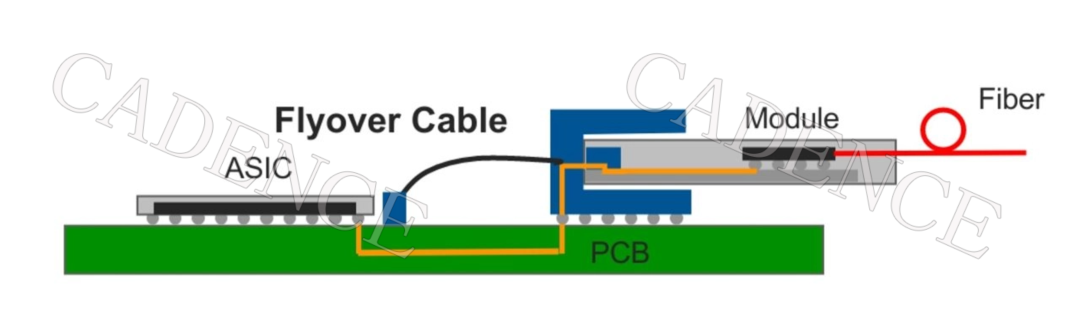

如今,訓(xùn)練 AI/ML 模型需要多個數(shù)據(jù)中心協(xié)作,而這些數(shù)據(jù)中心的地理位置又越來越分散,因此要求光纖網(wǎng)絡(luò)能夠有效應(yīng)對因傳輸距離變長而導(dǎo)致帶寬增加的問題。然而,將信號從 A 點傳輸?shù)?B 點便已消耗掉所有預(yù)算功耗,已沒有足夠的功耗來運行實際的 CPU 和 GPU,因此光模塊很快就會遇到功耗瓶頸。在這種情況下,非重定時的線性拓撲結(jié)構(gòu)便可發(fā)揮所長。與傳統(tǒng)的基于數(shù)字信號處理(DSP)的重定時光學解決方案相比,線性可插拔光學器件(LPO)鏈路可顯著降低模塊功耗和延遲,這對于提升 AI 性能至關(guān)重要。而且,由于功耗和冷卻要求有所降低,從基于 DSP 的解決方案切換到 LPO 還可顯著節(jié)約成本,減少開支,但于此同時,重定時器/DSP 將不再適用,而是需要一個功能強大的高性能 ASIC 來驅(qū)動光學器件。

為了展示 Cadence IP 的穩(wěn)健性,我們演示了面向 PCIe 7.0 的子系統(tǒng)測試芯片板能夠通過外部環(huán)回模式配置的非重定時光電鏈路成功發(fā)送和接收 128GT/s 信號,并留有多個數(shù)量級的裕度。

圖 5:ASIC 驅(qū)動線性光學器件示例

合規(guī)是關(guān)鍵

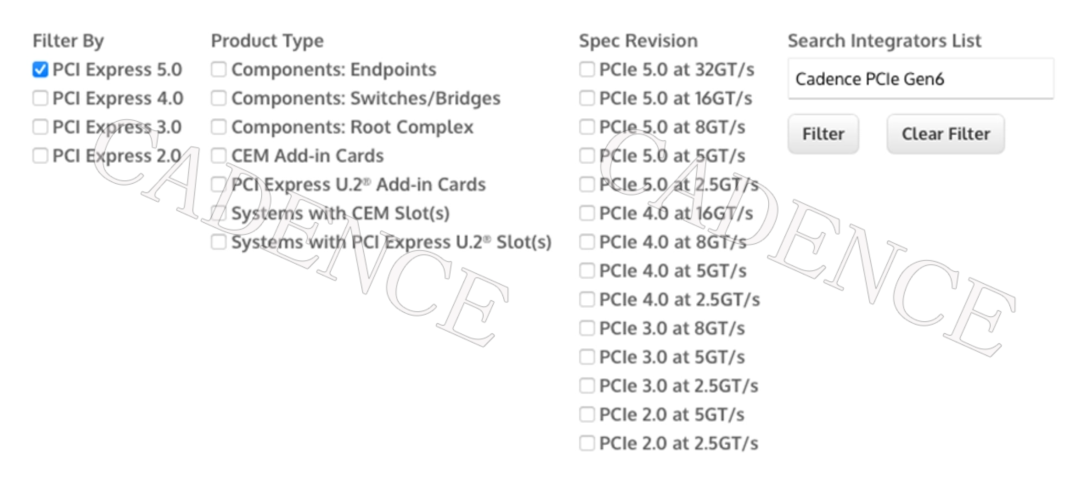

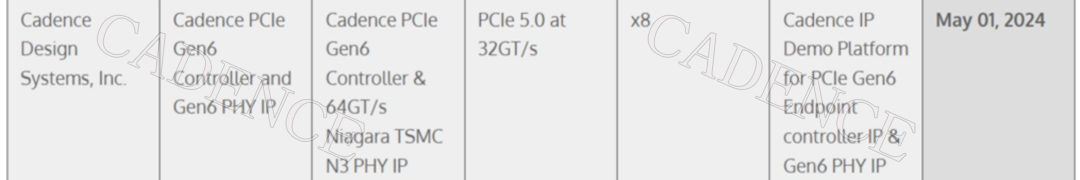

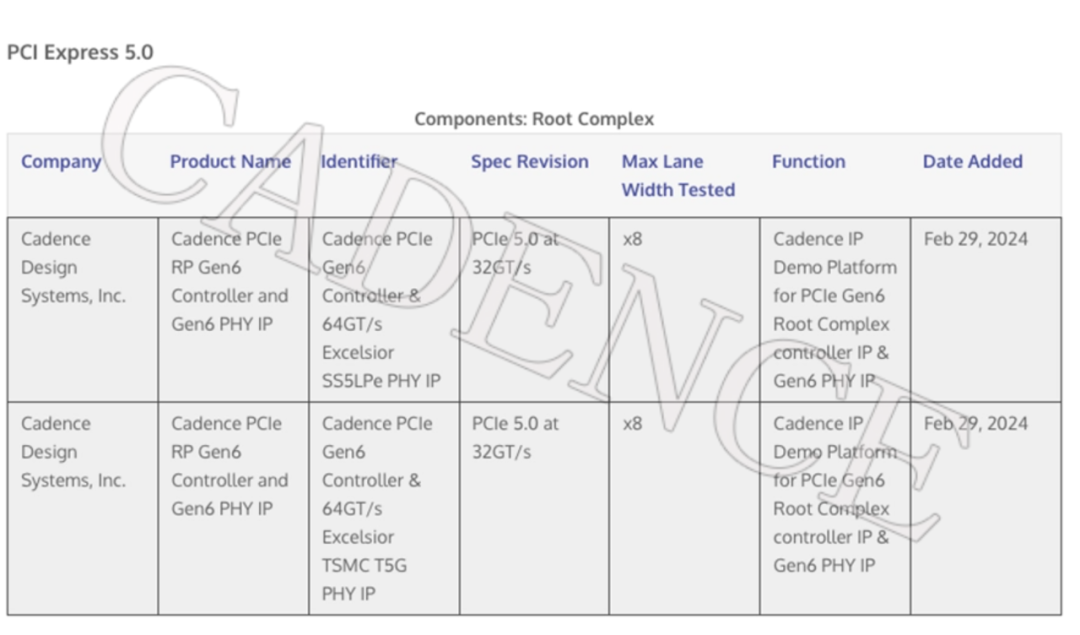

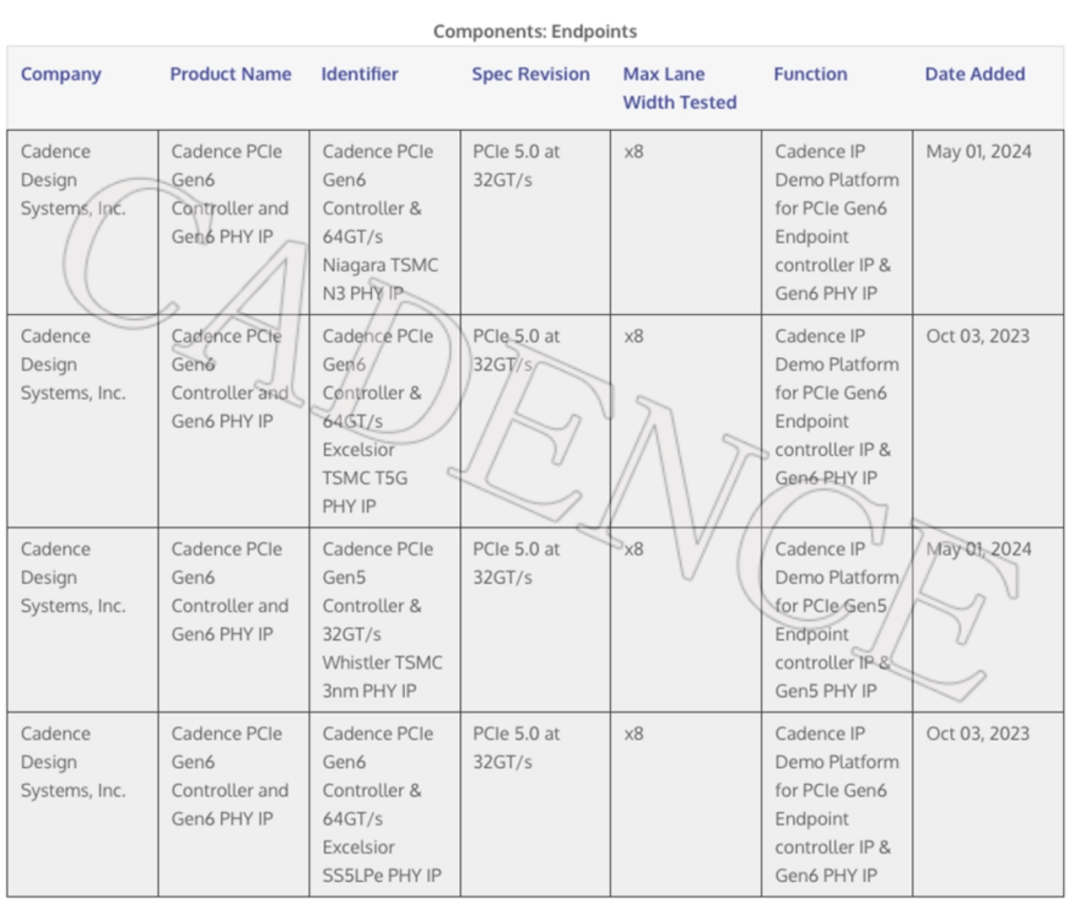

對 PCIe 6.0,目前官方合規(guī)計劃尚未啟動。這是 SIG 的常規(guī)做法,即在規(guī)范獲批幾年后啟動合規(guī)計劃,以便生態(tài)系統(tǒng)有充足的時間來準備初始產(chǎn)品,并讓測試和設(shè)備供應(yīng)商有足夠的時間來啟動和運行他們的硬件/軟件。目前,PCIe 6.0 只能通過最高 PCIe 5.0 級別(SIG 支持的最高官方合規(guī)性測試套件)的官方認證。我們已經(jīng)向 SIG 提交了針對多個工藝節(jié)點的 PCIe 6.0 IP 子系統(tǒng)解決方案,它們均被列為合規(guī)產(chǎn)品。您可以登錄 pcisig.com 網(wǎng)站,在 Developers->Integrators 列表下查詢。具體如下所示:

PCI-SIG 開發(fā)者大會的其他看點

在 6 月 12 日和 13 日舉辦的 PCI-SIG 開發(fā)者大會上,Cadence 進行了以下演示:

Cadence 面向 PCIe 7.0 的 IP 通過非重定時光學器件發(fā)送和接收 128GT/s 信號的強大性能

使用示波器測量 Cadence 面向 PCIe 7.0 的 IP 的功能,詳細說明其穩(wěn)定的電氣性能和裕度

Cadence 面向 PCIe 6.0 接口的 IP 的可靠性,使用測試設(shè)備表征 PHY 接收器的質(zhì)量

Cadence 面向 PCIe 6.0 的 PCI-SIG 兼容 IP 子系統(tǒng),在功耗和性能方面進行了優(yōu)化

作為 PCI Express 領(lǐng)域的領(lǐng)軍人物,Cadence 的 Anish Mathew 了分享他對“UIO ECN 對 PCIe 控制器設(shè)計和性能的影響”這個重要話題的寶貴見解,重點介紹了 Cadence 設(shè)計團隊在實現(xiàn)這一目標方面所取得的進展。

圖 6:Cadence UIO 實現(xiàn)總結(jié)

總 結(jié)

Cadence 于 2023 PCI-SIG 開發(fā)者大會期間展示了 PCIe7.0-Ready IP,將繼續(xù)引領(lǐng) PCIe IP 的開發(fā),面向 PCIe 7.0 提供支持先進節(jié)點的完整解決方案。預(yù)計這些解決方案將于明年初發(fā)布。Cadence 以 PCI-SIG 的成員身份為豪,將繼續(xù)為市場提供包括 PHYs、控制器、軟件和驗證 IP 在內(nèi)的完整解決方案,并大量投資于 PCIe 項目。Cadence 是首家提供面向 PCIe 3.0、4.0、5.0 和 6.0 的完整子系統(tǒng)解決方案的 IP 供應(yīng)商,擁有業(yè)內(nèi)領(lǐng)先的功耗、性能、面積(PPA )。我們很榮幸能夠繼續(xù)提供面向 PCIe 7.0 的最新 IP 子系統(tǒng)解決方案,為 PPA 和上市時間設(shè)定新的基準。

關(guān)于 Cadence

Cadence 是電子系統(tǒng)設(shè)計領(lǐng)域的關(guān)鍵領(lǐng)導(dǎo)者,擁有超過 30 年的計算軟件專業(yè)積累。基于公司的智能系統(tǒng)設(shè)計戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設(shè)計概念成為現(xiàn)實。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計算、5G 通訊、汽車、移動設(shè)備、航空、消費電子、工業(yè)和醫(yī)療等最具活力的應(yīng)用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產(chǎn)品。Cadence 已連續(xù)十年名列美國財富雜志評選的 100 家最適合工作的公司。

-

芯片

+關(guān)注

關(guān)注

459文章

51726瀏覽量

430975 -

接口

+關(guān)注

關(guān)注

33文章

8822瀏覽量

152632 -

Cadence

+關(guān)注

關(guān)注

65文章

942瀏覽量

143170 -

PCIe

+關(guān)注

關(guān)注

16文章

1291瀏覽量

83990

原文標題:Cadence 在 2024 PCI-SIG 開發(fā)者大會上展示完整的 PCIe 7.0 解決方案

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Cadence首個DDR4 Design IP解決方案在28納米級芯片上得到驗證

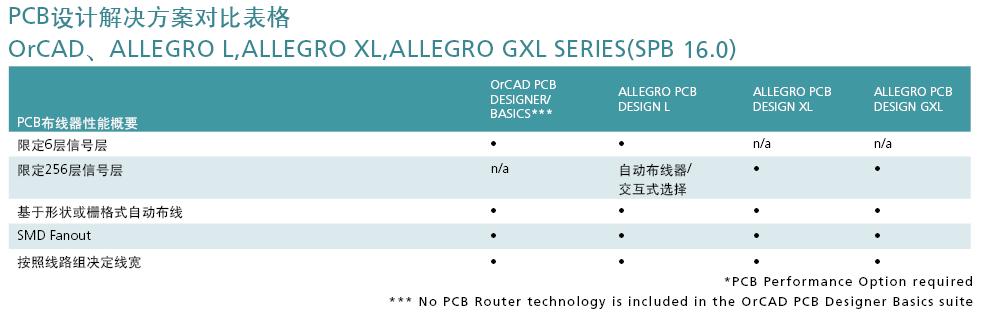

Cadence PCB設(shè)計解決方案

CADENCE PCB設(shè)計解決方案提供完整的設(shè)計環(huán)境

Voltus-Fi定制型電源完整性解決方案

CADENCE PCB設(shè)計技術(shù)方案

楷登電子發(fā)布PCIe 6.0規(guī)范Cadence IP

Cadence針對PCIe 6.0的完整IP解決方案

Cadence推出15種新驗證 IP(VIP)解決方案

力科將推出(PCIe)完整性新協(xié)議分析和流量生成解決方案

Cadence 于 2023 PCI-SIG 開發(fā)者大會期間展示 PCIe7.0-Ready IP

新思科技推出業(yè)界首款PCIe 7.0 IP解決方案

新思科技發(fā)布PCIe 7.0 IP解決方案,賦能AI與HPC前沿設(shè)計

新思科技推出業(yè)界首款PCIe 7.0 IP解決方案

新思科技PCIe 7.0驗證IP(VIP)的特性

評論