與同類FPGA相比,Agilex 7 FPGA可為OpenCores公開發布的設計提供超過一個速度等級的內核性能提升。

簡 介

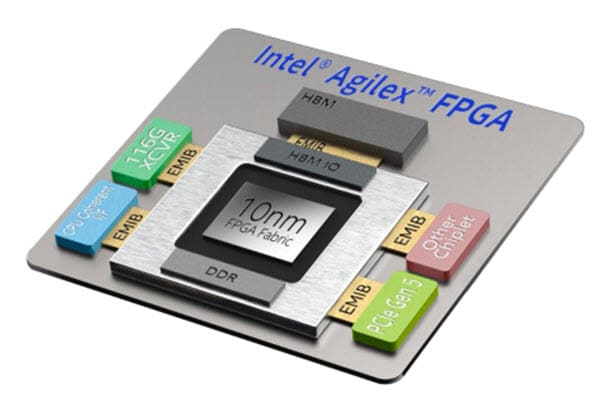

本文介紹了一種對Agilex 7 FPGA產品家族的內核性能進行基準測試的方法,旨在清晰地展示相關方法和數據,以便感興趣的讀者可以重新生成和分析這些結果。

背景:FPGA和SoC的基準測試

當前,可編程邏輯行業尚無標準的指標評測方法。為此,使用了嚴格的內部分析,并廣泛地采用了不同的設計組合,以充分了解、量化可編程邏輯產品相比前代產品/行業同類產品的性能。這些設計從不同的細分市場收集而來,包括高性能計算、圖像和視頻處理、有線和無線通信以及消費類產品等。此外,這些設計還使用了多種實施技術,包括來自行業同類產品的ASIC和FPGA。通過使用廣泛的設計套件,致力于確保結果準確無誤,且能夠代表客戶設計與Quartus Prime Software Suite等FPGA設計工具之間的復雜交互。為了使用客戶設計,已在轉換設計方面投資了大量資源,以便能夠與廣泛的合成工具和電子設計自動化(EDA)廠商合作。同時還確保功能予以保留,并針對特定FPGA廠商進行了適當的代碼優化,這點是必需的,因為開發設計時通常會針對特定FPGA對設計進行優化。

在性能比較方面,采用的是盡力而為法,目的是顯示可實現的最佳結果。盡力而為編譯方法實驗需要比默認按鈕(push-button)編譯更長的單獨編譯時間,而且,在該方法中,每項設計需要進行超過一次的編譯。

借助這種方法,確定了Agilex 7 FPGA和SoC可提供比7納米FPGA行業同類產品更高的內核性能,測量指標為在設計套件的每項設計中,針對速度關鍵型時鐘路徑所能實現的最大fMAX。

性能差異在13%-25%左右(具體數據取決于不同的設計),大約相當于一個或兩個速度等級優勢,一個速度等級通常被定義為10%-15%?的性能差異。這些結果有力證明了Agilex 7 FPGA作為最高性能10納米FPGA產品家族的地位。然而,由于這些結果是專有設計獲得的,所以只能就這項分析分享有限的詳情,這最終會限制這些信息對可編程邏輯用戶的有用性。

通過基于OpenCores的性能比較提高透明度

為了克服在理解可編程邏輯性能方面的挑戰,使用已發布的OpenCores(www.opencores.org)設計進行指標評測。OpenCores提供了開源硬件知識產權(IP)內核。這項指標評測旨在幫助可編程邏輯用戶:

了解性能評估過程中使用的具體設計,包括這些設計具體到寄存器傳輸級(RTL)描述的詳細信息

自己重新生成分析結果

仔細查看分析結果,以更好地了解Agilex 7 FPGA性能和器件利用率,以及這些性能優勢對于特定設計的意義

這項基于OpenCores的分析的范圍小于使用的內部分析,因為前者專注于受時間約束的比較。分析并不全面,但分析結果說明了實施相似設計,或實施與設計示例套件所用功能相似的功能設計時,Agilex 7 FPGA相比行業同類器件的相對性能。

OpenCores標記方法

OpenCores設計只使用了目標設備中的一小部分資源,只使用這一小部分資源并非用戶的慣例,也達不到他們所期望的目標。此外,隨著設備資源逐漸被耗盡,以及設計變得更難以放置和路由,不斷增加的利用率通常會對可實現的最高fMAX產生不利影響。為了模擬設備利用率對可編程邏輯性能的影響,OpenCores設計執行了大量編譯,而且每次都會在前一次編譯的基礎上添加更多OpenCores實例。為了增加可編程邏輯設備的設計尺寸,每項OpenCores設計都在FPGA中重復進行了實例化(對同一內核進行多次標記):

每次標記都并行實施

添加I/O包裝程序邏輯以減少更大設計所需的I/O引腳數

內核與包裝程序邏輯之間不存在時間關鍵路徑

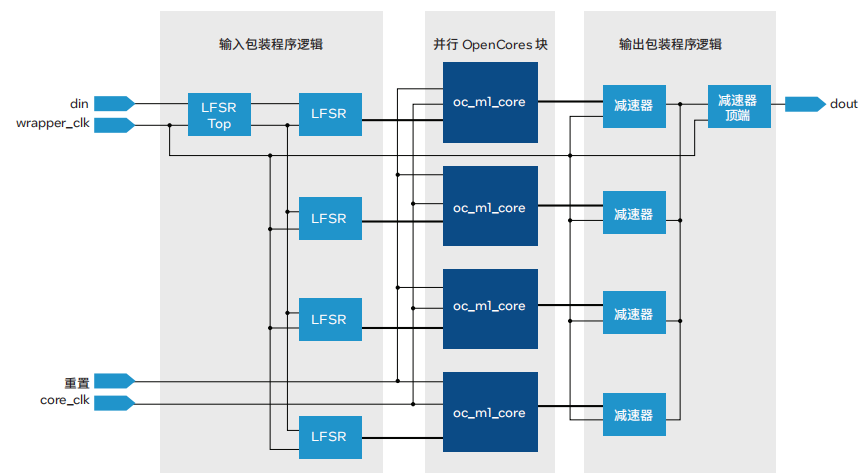

包裝程序邏輯提供了盡可能少的開銷。圖1顯示了標記過程

圖1. 在FPGA中對oc_m1_core設計進行了四次實例化

OpenCores標記和基準測試方法

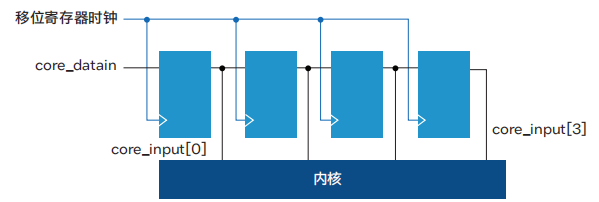

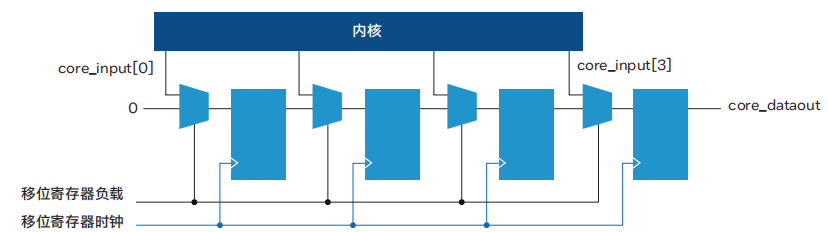

隨著OpenCores設計標記數量增加(因此設計尺寸不斷增加),I/O引腳和全局時鐘等資源變得有限。為了避免引腳用盡,每個OpenCores設計都包裹在移位寄存器中,以便一個物理引腳能夠為內核的所有輸入引腳提供信息,以及內核的所有輸出引腳都將信息輸入到可加載的移位寄存器中。圖2和圖3分別顯示了輸入和輸出移位寄存器。移位寄存器尺寸取決于I/O引腳數量,移位寄存器的數量取決于FPGA中實施的OpenCores設計數量。

圖2. 輸入移位寄存器實施

圖3. 輸出移位寄存器實施

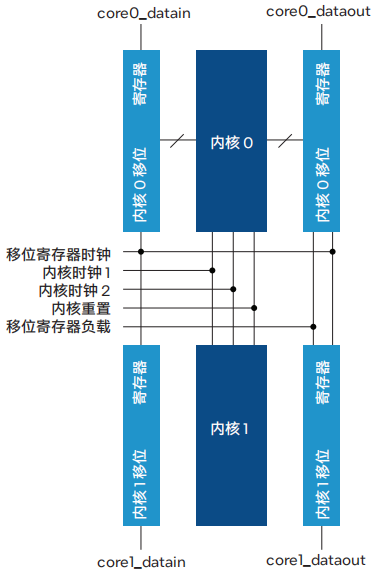

為了避免全局時鐘資源耗盡,一個引腳直接為所有OpenCores設計提供全局時鐘和重置信號。例如,如果一個內核需要兩個時鐘(即內核時鐘1與內核時鐘2)以及一個重置信號,內核時鐘1的所有實例由一個引腳提供,內核時鐘2的所有實例由另一個不同的引腳提供,重置信號的所有實例由第三個引腳提供。借助該方法,所有OpenCores設計都擁有相同的時鐘和重置信號(請參見圖4)。

圖4. 共享時鐘和重置信號的雙核實施

在FPGA中,包裝程序邏輯將所有OpenCores設計相連接后,為確保包裝程序邏輯(即移位寄存器)和OpenCores設計之間不存在關鍵路徑。為了實現這一目標,創建了錯誤的路徑,同時通過為內核時鐘和包裝程序邏輯時鐘設置不同的無關時鐘域,消除了時間路徑。然后,這些設計工具可將內核和移位寄存器分開優化。在設備和設計工具允許的情況下,對OpenCores設計進行了盡可能多的實例化,且無編譯錯誤。

軟件工具、設置與約束

為了開展這項研究,使用了分析時可用的所需FPGA開發工具的最新版本:

Quartus Prime Software Suite版本22.4

把工具安裝并運行于Linux64設備之上。這些可編程邏輯工具提供的設置在設計性能、邏輯資源使用、編譯時間和內存使用之間進行了折中。需要注意的是,某些設計可能使用特定設置生成最佳結果,但這并不意味著該設置適用于另一項設計。此外,用于指引EDA工具的用戶約束可改善結果。即便使用代表客戶設計的設計集,指標評測結果也會因軟件設計和應用約束的不同而存在顯著差異。對于本文介紹的比較,使用了盡力而為的編譯模式,并設置了較為嚴格的時間約束。為了確定每項設計的嚴格時間約束,對每個OpenCores設計時鐘應用了頻率約束,以確定每個時鐘剛好無法滿足的約束。通過不斷增加約束直至無法滿足,確定了基礎約束。然后,通過將基礎約束值乘以最少1.3的系數,確定了嚴格約束。下面部分介紹了為每項設計應用的約束。

結 語

Agilex 7 FPGA家族實現了更高的fMAX值,范圍在3%到41%之間,幾何平均值為20%。性能優勢相當于一到兩個速度等級。此外,結果表明,在利用率較高的情況下,Agilex 7 FPGA性能穩定性更好,在這種情況下,Hyperflex 架構能提供更高的性能,讓您可以更充分地利用可用邏輯。

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603319 -

寄存器

+關注

關注

31文章

5343瀏覽量

120348 -

內核

+關注

關注

3文章

1372瀏覽量

40289 -

soc

+關注

關注

38文章

4165瀏覽量

218243 -

Agilex

+關注

關注

0文章

11瀏覽量

3746

原文標題:Agilex ? 7 FPGA在OpenCores中展示性能優勢

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于Altera Agilex? 7 400G Ethernet IP 與FPC202芯片控制使用手冊

貿澤開售用于PCIe 4.0 設計的Intel Agilex F系列FPGA開發套件

深度解讀:Intel最新的FPGA Agilex

Agilex FPGA,現代FPGA技術的核心力量

英特爾Agilex FPGA家族全系列概述表

解密英特爾? Agilex? FPGA家族的八大特性

基于英特爾?AGILEX? FPGA和SOC FPGA的BittWare加速“雙星”發布

全新英特爾Agilex D系列FPGA和SoC適用于中端FPGA應用

全新英特爾? Agilex? FPGA 和 SoC 家族產品解析

英特爾? Agilex? D系列FPGA和SoC適用于中端FPGA應用

英特爾Agilex FPGA的優勢和特性

英特爾Agilex 3 FPGA產品家族介紹

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

將AFE7769DEVM與Hitek Agilex eSOM7 FPGA連接

Agilex 7 FPGA和SoC的基準測試

Agilex 7 FPGA和SoC的基準測試

評論