電子發燒友網報道(文/吳子鵬)英特爾CEO基辛格此前表示,摩爾定律并沒有失效,只是變慢了,節奏周期正在放緩至三年。當然,摩爾定律不僅是周期從18個月變為了3年,且開發先進制程成本高昂,經濟效益也變得越來越差。在這種情況下,超越摩爾逐漸成為打造高算力芯片的主流技術。

超越摩爾是后摩爾定律時代三大技術路線之一,強調利用層堆疊和高速接口技術將處理、模擬/射頻、光電、能源、傳感等功能單元集成在一個系統內,實現系統性能的提升,并降低大型SoC的開發成本。當前,先進封裝技術路線非常多,且各家公司主攻方向不同,呈現百花齊放、百家爭鳴的狀態。

近日,在博聞創意會展(深圳)有限公司主辦的elexcon2024深圳國際電子展上,專門設立了主題為“系統級封裝SiP”的專業論壇,會議內容涵蓋Chiplet芯片設計與測試、Chiplet互聯標準與生態、2.5D/3D IC封裝技術和SiP封裝量產方案等。

博聞創意會展(深圳)有限公司主辦的

elexcon2024深圳國際電子展“系統級封裝SiP”論壇

Chiplet異構集成的機遇和挑戰

如上所述,先進封裝是指封裝更多的集成電路 (IC) 以提高性能的多種創新技術,包括扇出 (FO) 型封裝、晶圓級芯片規模封裝 (WLCSP)、倒裝芯片球柵陣列 (fcBGA)、倒裝芯片CSP (fcCSP)、系統級封裝 (SiP) 和2.5D/3D堆疊封裝等。因此,在先進封裝發展過程中,Chiplet(芯粒)異構集成是重要的底層技術之一。

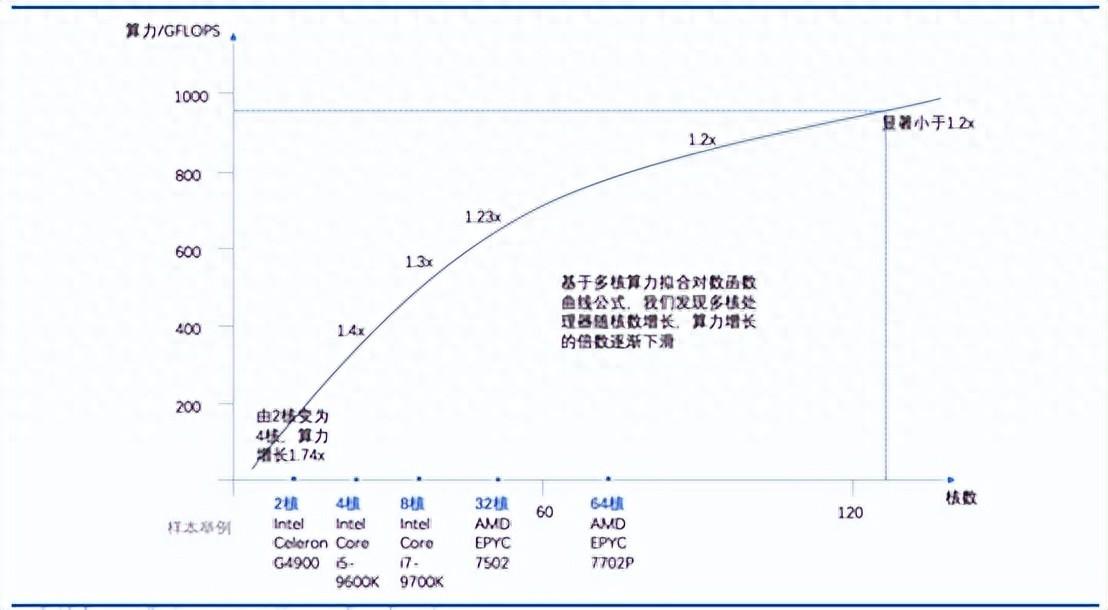

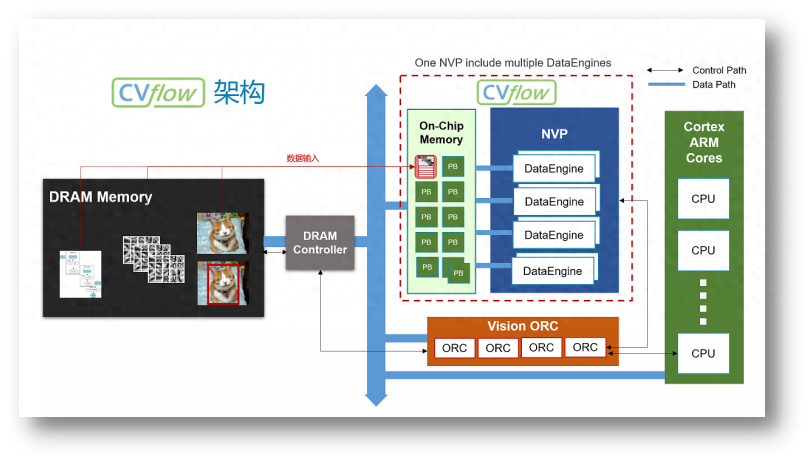

與傳統單片器件相比,Chiplet的設計和制造流程明顯不同。芯和半導體聯合創始人&總裁代文亮博士在elexcon2024深圳國際電子展“系統級封裝SiP”論壇上演講時表示,Chiplet異構集成正在推動高效能算力升級。傳統單片器件的方式存在“存儲墻”的問題,數據讀取不僅延遲高,而且會產生額外的功耗和熱量,通過將3DIC Chiplet、HBM和異構集成芯片技術融合,能夠實現更高效能的算力架構體系。

芯和半導體聯合創始人、總裁 代文亮博士

因此,Chiplet異構集成在當前大型SoC的設計制造過程中被廣泛采用,代文亮博士在演講中列舉了幾個例子,包括英特爾Gaudi 3、AMD Instinct MI300X加速器和英偉達Blackwell 200等。簡單解讀一下英特爾Gaudi 3,這是英特爾子公司Habana Labs推出的下一代Gaudi高性能人工智能加速器。英特爾Gaudi 3使用2.5D CoWoS封裝來鏈接四個HBM2內存堆棧,每個堆棧8 GB,總共32 GB內存,聚合帶寬為1 TB/s。

代文亮博士稱,高算力終端正在讓Chiplet異構集成系統加速下沉,包括數據中心領域的數據處理存儲、AI訓練和推理、數據交換傳輸等需求,AI終端領域的意識識別響應、數據處理存儲等需求,以及智能汽車領域的自動駕駛ADAS、智能座艙體驗等需求,都廣泛采用了Chiplet異構集成系統。不過,他也強調,目前Chiplet異構集成系統尚處于產業早期,生態還不太成熟,需要頭部芯片廠商、行業組織機構和下游應用廠商攜手努力,共同完善產業生態建設。

從產業發展現狀來看,目前Chiplet異構集成在Die to Die互聯標準、先進封裝和材料等方面都沒有形成統一的行業標準。比如在Die to Die互聯標準方面,目前UCIe、BoW、AIB、XSR、CCITA等標準都有行業巨頭在推動,企業在打造Chiplet異構集成系統時需要盡可能多地考慮這些標準,以提升功能Die的普適性。

當然,也有機構在推動Chiplet異構集成在Die to Die互聯標準上的統一,那就是UCIe產業聯盟。UCIe的全稱是Unified Chiplet Interconnect Express,定義了提供高帶寬、低延遲、高效率、低成本的Die間互聯的協議,用于CPU/CPU之間,CPU/Accellerator之間以及CPU和IO Die之間的互聯。

UCIe產業聯盟由英特爾牽頭,聯合了臺積電、三星、日月光(ASE)、AMD、Arm、高通、谷歌、Meta(Facebook)、微軟等行業巨頭,目前共有超過120多家公司加入。在elexcon2024深圳國際電子展“系統級封裝SiP”論壇上,阿里云智能集團首席云服務器架構師和研發總監、CXL和UCIe董事會成員陳健為大家詳細介紹了UCIe協議的迭代以及UCIe 2.0里面的重要更新。

阿里云智能集團首席云服務器架構師和研發總監、CXL和UCIe董事會成員 陳健

陳健稱,UCIe主要注重四大關鍵維度的演進,分別是:

·帶寬密度

減少IO對硅片面積的影響,滿足AI對高算力密度的需求。

·靈活性

高效支持自定義協議。

·可靠性

確保SiP的使用壽命。

·可測性

滿足單硅片和多硅片的測試要求。

這些特性在UCIe 2.0規范更新中都得到了體現。今年8月初,UCIe產業聯盟正式推出了UCIe 2.0規范,增加了對可管理性標準化系統架構的支持,并從整體上解決了SiP生命周期中從排序到現場管理的多個小芯片的可測試性、可管理性和調試(DFx)的設計挑戰。引入可選的可管理性特性和UCIe DFx架構(UDA),其中包括每個芯片內用于測試、遙測和調試功能的管理結構,實現了與供應商無關的芯片互操作性,為SiP管理和DFx操作提供了靈活統一的方法。

同時,UCIe 2.0規范不僅顯著提高了帶寬密度和能效,還全面兼容了前代版本UCIe 1.1和UCIe 1.0,為行業用戶提供了更加靈活和強大的解決方案。

先進封裝和Chiplet異構集成相輔相成

在打造高算力芯片的過程中,Chiplet異構集成和先進封裝技術屬于是相互配合、相互促進。Chiplet異構集成是以小芯片的方式滿足人工智能、網絡、自動駕駛、高端PC 和高端游戲等領域的高算力需求,要將這些小芯片融合在一起,就離不開先進封裝技術。因而,先進封裝正在成為將多個Die集成到單個封裝中的關鍵解決方案。

同時,Chiplet異構集成也在影響先進封裝技術的發展,比如基板封裝(Substrate packaging)、硅中介層封裝(Silicon-interposer packaging)是應用于Chiplet異構集成的重要封裝技術。目前,產業界正在積極探索玻璃基板和玻璃中介層。如果是將硅中介層換成玻璃中介層,就可以將芯片集成到大型封裝中,同時提供更好的平整度,這對于HPC和AI應用程序至關重要。

當然,目前晶圓代工廠和封測廠商對于先進封裝的理解會有區別,因此提供的先進封裝方案也會有差異。市場主流當屬臺積電,目前該公司IC先進封裝主要有TSMC-SoIC、InFO、CoWoS等,其中InFO是一種先進的扇出型晶圓級封裝(FOWLP)技術,直接在芯片的外圍形成更多的I/O連接點,技術拓展包括InFO-PoP、InFO-oS、InFO-LSI等;CoWoS是一種先進的2.5D封裝技術,將多個不同功能的芯片首先封裝到中介層上,然后將該結構封裝在基板上,技術拓展包括CoWoS-S、CoWoS-R、CoWoS-L;TSMC-SoIC是3D IC封裝方案,采用了無凸點的直接鍵合技術,主要包括CoW(Chip-on-Wafer)和WoW(Wafer-on-Wafer)兩種形式。

在elexcon2024深圳國際電子展“系統級封裝SiP”論壇上,日月光半導體制造股份有限公司資深副總陳光雄在《異質整合的創新與發展》主題報告中也介紹了日月光公司的先進封裝方案。

日月光半導體制造股份有限公司資深副總陳光雄

陳光雄首先談到了日月光的VIPack平臺先進封裝技術。VIPack由六大核心封裝技術支柱組成,透過全面性整合的生態系統協同合作,包括基于高密度RDL的FOPoP、FOCoS、FOCoS-Bridge、FOSiP,以及基于硅穿孔(TSV)的2.5D/3D IC和Co-Packaged Optics。

其次,陳光雄介紹了日月光的SiPack平臺,屬于SiP 2.0平臺,主要優化了尺寸、整合度、成本、開發周期、電性能和可靠性。具體表現為:

·減小尺寸,減少布局和組件數量,簡化最終用途設計;

·減少封裝、測試和包裝成本;

·實現更靈活的模塊化設計;

·降低系統總成本;

·帶來更好的系統可靠性;

·增強環境和系統內的EMI屏蔽。

陳光雄舉例稱,借助日月光的SiPack平臺,客戶可以將原來55*112mm的PCB方案,縮小成一個18*18mm的先進封裝方案,方案面積顯著縮小,系統功率密度顯著提升。

結語

根據Yole的統計數據,2023年全球先進封裝市場規模約為439億美元左右,同比增長19.62%。同時,預測數據顯示,2024年全球先進封裝市場份額將在整個封裝市場中達到49%,預計將在2025年正式超越傳統封裝。

先進封裝和Chiplet異構集成是打造高算力芯片的關鍵手段。當然,目前還處于產業初期,主要圍繞晶圓代工巨頭和封裝巨頭展開,未來將輻射到整個IC行業,進一步釋放這個組合的潛力。在博聞創意會展(深圳)有限公司主辦的elexcon2024深圳國際電子展上,我們也清晰地看到,廠商在尋求統一,這樣技術的前景才會更好。

-

摩爾定律

+關注

關注

4文章

634瀏覽量

79026 -

AI芯片

+關注

關注

17文章

1887瀏覽量

35018 -

chiplet

+關注

關注

6文章

432瀏覽量

12593 -

UCIe

+關注

關注

0文章

46瀏覽量

1632 -

先進封裝

+關注

關注

2文章

404瀏覽量

246

發布評論請先 登錄

相關推薦

億鑄科技熊大鵬探討AI大算力芯片的挑戰與解決策略

AI網絡物理層底座: 大算力芯片先進封裝技術

名單公布!【書籍評測活動NO.43】 算力芯片 | 高性能 CPU/GPU/NPU 微架構分析

大模型時代的算力需求

AI應用致復雜SoC需求暴漲,2.5D/Chiplet等先進封裝技術的機遇和挑戰

COMPUTEX 2024:江波龍以大容量存儲賦能AI時代

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

評論