DDS是直接數(shù)字式頻率合成器(Direct Digital Synthesizer)的英文縮寫,是一項關鍵的數(shù)字化技術。與傳統(tǒng)的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉(zhuǎn)換時間等優(yōu)點。先說明一下,要產(chǎn)生真正的模擬信號,需要接A/D轉(zhuǎn)換芯片,這次主要是產(chǎn)生FPGA發(fā)出的數(shù)字信號(在modelsim中以模擬量查看)。

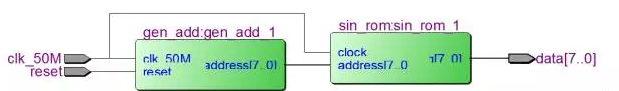

首先先看一下整體的連接圖:

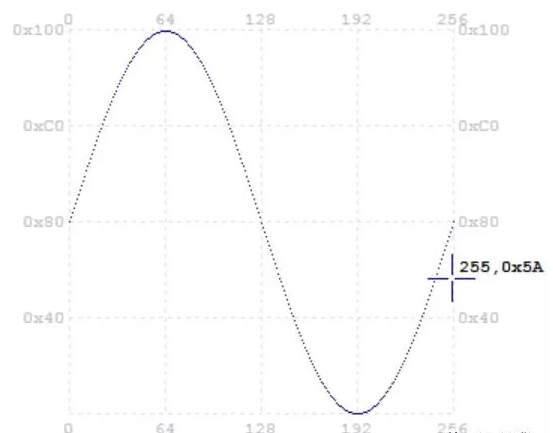

其中sin_rom模塊是存儲正弦波形數(shù)據(jù)的rom(rom調(diào)用quartusip核),深度256,寬度8位,我們用產(chǎn)生好的mif文件(可以利用mif_make2010這個軟件產(chǎn)生,也可以利用c語言matlab產(chǎn)生但要注意文件格式)去初始化rom,假如我們采用mif_make2010產(chǎn)生mif文件,波形如下:

其中行坐標是是0-255,表示rom的256個存儲單元,縱坐標表示的是每個存儲單元的數(shù)值大小,波峰為0xFF;波谷為0x00,即我們依次從rom的第一個地址讀,一直讀完,從rom中讀出的數(shù)據(jù)就是正弦波形的數(shù)字量表示。所以程序中我們只需控制地址的產(chǎn)生就可以達到調(diào)相調(diào)頻的目的,所以設置了gen_add模塊。

調(diào)相原理:由于0-255個單元對應的相位是0-360度,所以我們只需調(diào)整初始相位的單元就可以到達調(diào)相的目的,例如假如初始單元就是0,那我們的波形就是標準的正弦波,如果我們的初始單元為64,那我們的波形就是余弦波。

調(diào)頻原理:我們調(diào)整地址產(chǎn)生的頻率快慢就可以調(diào)整波形頻率。假如我們時鐘50M,每個時鐘上升沿從rom中讀取一個數(shù)據(jù),由于一個周期的sin波形是有256個點組成,所以我們相當于256個時鐘產(chǎn)生一個完整的sin波,即周期為256*(1/50M);頻率為50M/256;

從頻率表達式我們可以看出波形的頻率一是跟時鐘有關,二是跟存儲的rom單元數(shù)有關,我們上述采用的是256個單元,所以產(chǎn)生的頻率為50M/256=195.3Khz,這是我們順序從rom中讀取數(shù)據(jù),即地址每個時鐘加一產(chǎn)生的頻率,若我們的每個時鐘地址加2(步長),則我們的產(chǎn)生的頻率則為原來的2倍,即2*50M/256=195.3*2。但我們想一想如果我們的的rom深度數(shù)256,那產(chǎn)生的頻率分辨率最高也就是50M/256即195.3Khz,,而且我們產(chǎn)生的頻率只能是195.3Khz的整數(shù)倍,這個有點難以接受。我們自然想到可以增大rom的位數(shù)來提高分標率,這個當然可以,但是我們rom都是提前固定的,有沒有其他辦法呢?

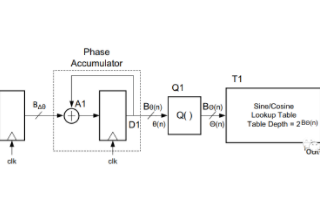

假如我們設定一個32的寄存器address_temp,我們只把address_temp的前八位真正的交給rom讀數(shù)據(jù),這樣相當于減慢了地址的變化速度,但我們實際上提高了頻率分辨率,現(xiàn)在的分辨率為50M/2^32=0.011hz,同樣我們產(chǎn)生的頻率只能是0.011hz的倍數(shù),但是我們可以認為任何整數(shù)都可是0.011的倍數(shù),假設步長為span_fre,則產(chǎn)生的頻率為span_fre*50M/2^32;這有點類似之前的應用篇(三)精準分頻,事實上它的原理就來源于此。

同理我們根據(jù)頻率來調(diào)節(jié)步長即可。

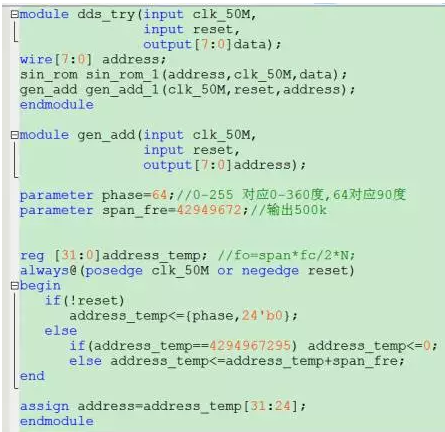

程序如下:

仿真結(jié)果如下:

從結(jié)果我們可以看為起始相位為90度即cos波形,(雖然我們rom中存儲的是sin波形的數(shù)據(jù)),頻率為500k,注意data的顯示格式是一定設置為無符號的模擬量。當我們把phase改為0時結(jié)果如下:

可以看出此時起始相位為0度,為sin波形。

-

FPGA

+關注

關注

1629文章

21754瀏覽量

604231 -

DDS

+關注

關注

21文章

634瀏覽量

152728 -

ModelSim

+關注

關注

5文章

174瀏覽量

47290

發(fā)布評論請先 登錄

相關推薦

我了解的DDS

基于FPGA的DDS怎么控制幅值?

FPGA+DA怎么實現(xiàn)調(diào)相呢,不是數(shù)字調(diào)制

FPGA控制DDS輸出調(diào)頻信號時,頻譜儀上只出來一個下限值,沒有調(diào)頻

怎么實現(xiàn)基于FPGA+DDS的正弦信號發(fā)生器的設計?

基于FPGA的DDS調(diào)頻信號的研究與實現(xiàn)

QPSK調(diào)制器的FPGA實現(xiàn)

基于FPGA的DDS信號源設計與實現(xiàn)

間接調(diào)頻調(diào)相電路

FPGA配合NIOS技術的精確調(diào)頻發(fā)生器

基于FPGA的DDS設計

基于DDS技術的多路同步信號源的設計

解析Vivado如何調(diào)用DDS的IP進行仿真

基于FPGA的DDS IP實現(xiàn)線性調(diào)頻信號的設計方案

FPGA應用技巧和訣竅:模擬DDS(調(diào)頻調(diào)相)

FPGA應用技巧和訣竅:模擬DDS(調(diào)頻調(diào)相)

評論