AI已經從技術走向應用,改變了我們的生活和工作方式。近些年,AI算力芯片領域群雄逐鹿,通過對芯片、算力與AI三者發(fā)展迭代過程的理解,我們發(fā)現高能效比的算力、通用的軟件棧以及高度優(yōu)化的編譯器,是我們的AI算力產品邁向成功的必要條件。

進迭時空作為計算芯片企業(yè),我們對RISC-V架構CPU進行高度定制,不斷挖掘其在計算中的潛力,在RISC-V生態(tài)強大的軟件棧與CPU領域成熟的編譯器的基礎上對RISC-V DSA進行聯合優(yōu)化并提供軟硬一體的計算解決方案,給AI領域帶來高效、易用的算力。

Banana Pi BPI-F3

GPGPU作為HPC領域(通用算力)的DSA打開了AI的大門

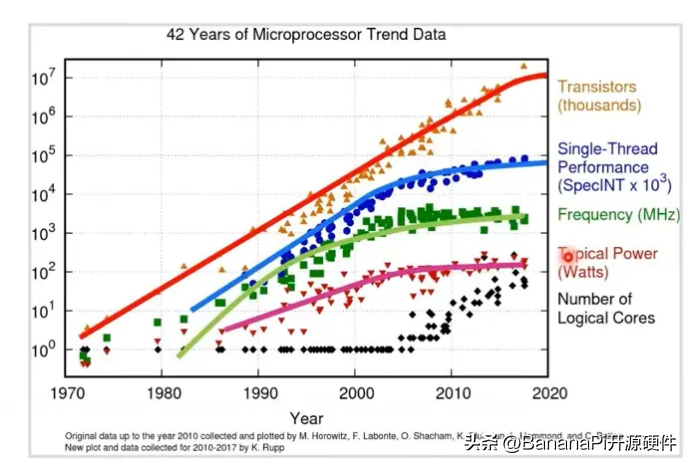

在上世紀80年代到90年代之間,隨著科技的迅速發(fā)展,CPU的性能每隔約18到20個月就會翻倍。這便是英特爾(Intel)創(chuàng)始人之一戈登·摩爾提出的摩爾定律(Moore's Law)的核心內容。其含義是,每隔大約18個月,同一款軟件在新發(fā)布的CPU處理器上的運行速度都能直接翻倍。

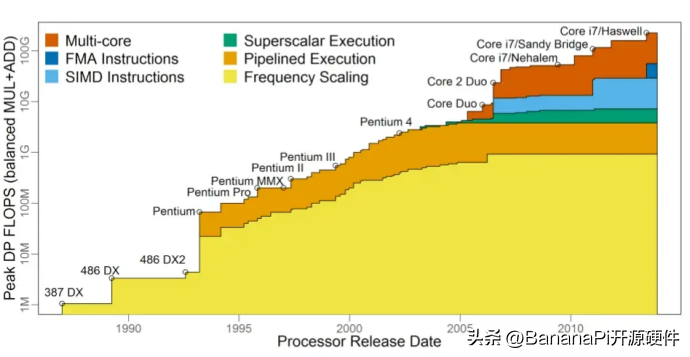

大約在2004年5月份,轉折點出現了。當時,Intel取消了他們新一代單核處理器的開發(fā)工作,而將注意力轉向了雙核處理器的設計。稍晚的同年,Herb Sutter撰寫了著名的《The Free Lunch Is Over(不再有免費午餐)》,主要表達了這樣一個觀點:除非軟件的開發(fā)采用多核多線程的設計,否則就無法再像過去那樣每隔一年多時間就獲得一倍的加速效果。正如下圖所示,CPU處理器的單核計算性能開始接近一個平臺區(qū)間,通過增加晶體管密度提升計算性能的方法已經顯得力不從心,因為芯片尺寸的不斷縮小總會遇到其物理極限。這意味著要獲得更高的性能提升,就需要采用新的方法。

添加圖片注釋,不超過 140 字(可選)

圖一:42年間的微處理器趨勢數據

隨著晶體管數量增加到一定程度,CPU單核性能的增加開始衰減并面臨瓶頸

在摩爾定律效應放緩的后摩爾時代,持續(xù)提升處理器性能的重要技術理念是Domain-Specific Architectures(DSA)。DSA利用可編程的專用集成電路(ASICs)來加速特定高強度的處理器負載,例如圖形渲染、AI神經網絡的前向推理計算以及提高巨量網絡數據的吞吐等。

架構的定義包含指令集架構與微架構。指令集架構是軟件與硬件對話的接口,類似于詞典中的詞條,而軟件程序則是使用這些詞條編寫的書籍。

添加圖片注釋,不超過 140 字(可選)

圖二:架構設計哲學

DSA的理念是通過面向特定領域的架構設計來縮小應用范圍,從而實現更高的性能或更好的能效比,同時保持可編程的靈活性。

? 面向領域的架構設計可以以較低的成本獲取較高的算力,以滿足算力需求。

? 指令集架構的可編程性帶來了相對通用的算力,為下一代算法的應用和覆蓋更廣泛的領域提供了無限的可能。

DSA的概念由2017年圖靈獎得主Henessy和Patterson提出,并在題為《創(chuàng)新體系結構將迎來新的黃金時代》的演講中進行了闡述。我們最熟悉的DSA之一可能是顯卡(Graphics Processing Unit即GPU),它在游戲、影音娛樂等領域中扮演著重要角色。

NVIDIA公司于1999年發(fā)布其標志性產品GeForce256時首次提出了GPU的概念。其實質是為了加速計算3D虛擬世界的渲染,從而降低CPU的負載。GPU技術的進步推動了顯卡殺手級游戲引擎的激進發(fā)展,到如今,游戲畫面的逼真程度已經堪比真人版電影。

時間來到2006年,NVIDIA發(fā)布了GeForce 8800 GTX(核心代號G80),與G80一同發(fā)布的還有著名的CUDA(compute unified device architecture),并提供了驅動程序和C語言擴展。

CUDA的發(fā)展至今,區(qū)別于開放計算語言(OpenCL跨平臺并行編程的獨立開放標準),開發(fā)人員可以使用流行的語言(C、C++、Fortran、Python、MATLAB等)編寫CUDA程序,并使用幾個基本的關鍵字即可將并行性添加到他們的代碼中,而不僅僅局限于使用C語言。盡管理論上OpenCL的運行時編譯能夠帶來更高的執(zhí)行效率,但實際上由于CUDA是由同一家開發(fā)執(zhí)行其功能的硬件的公司開發(fā),所以后者能更好地匹配GPU的計算特性,從而提供更好的性能。

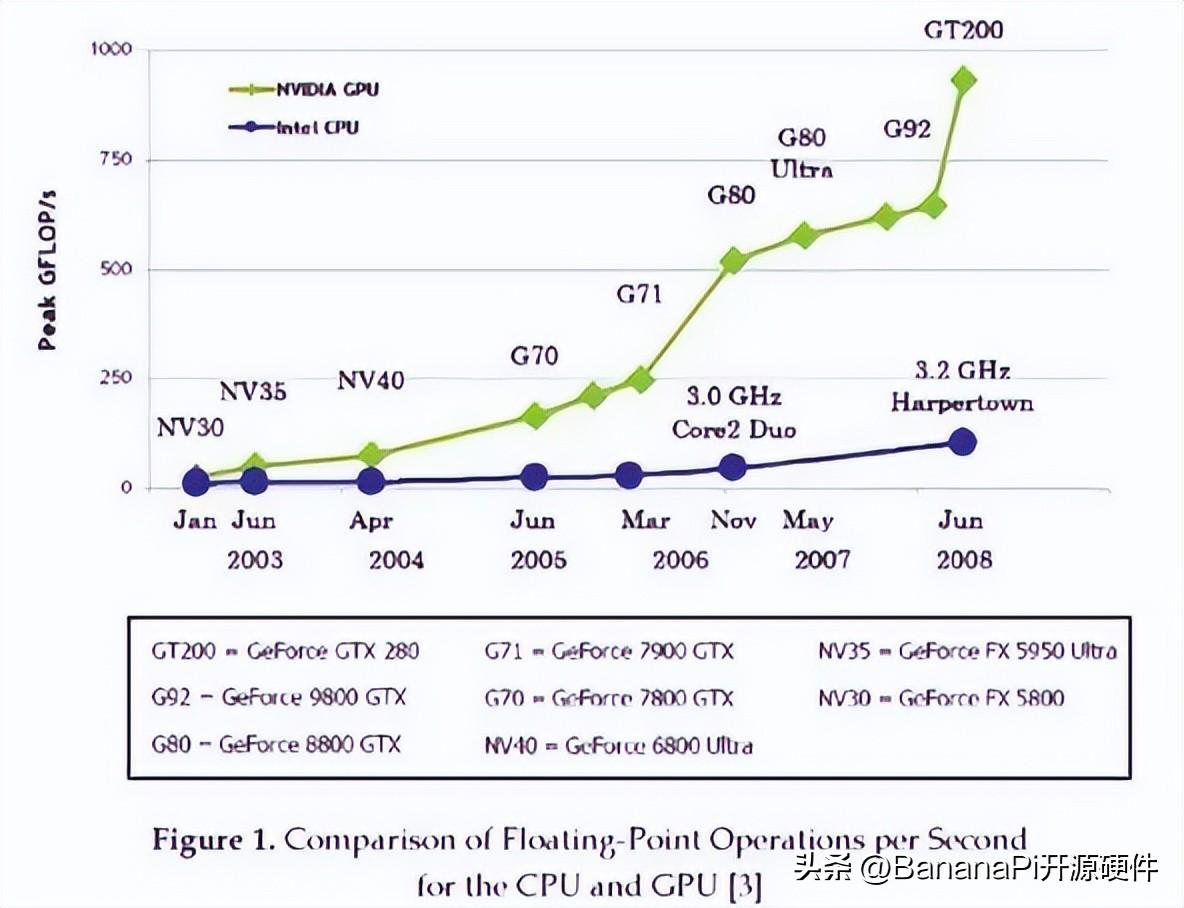

CUDA便捷的編程模型和優(yōu)秀的編譯器使得硬件資源能夠被更充分地利用,從而拓展了GPU的應用領域。如圖三所示,G80核心能夠提供與同時期以CPU為中心的高性能處理器相當甚至更高的計算能力。這一優(yōu)點引起了高性能計算(High-Performance Computing HPC)社區(qū)的關注,并加入到CUDA的生態(tài)系統(tǒng)中進行研究。此外,NVIDIA公司還提供了cuBLAS、cuRAND、cuSPARSE、cuSolver、cuFFT、NPP等一系列實用高效的計算庫,進一步擴充了NVIDIA的算力生態(tài)。

添加圖片注釋,不超過 140 字(可選)

圖三:同時期CPU、GPU浮點算力對比

2012年,多倫多大學的Alex Krizhevsky發(fā)布了一種新的深度神經網絡(DNN,也可稱為深度卷積神經網絡CNN)。該模型名為AlexNet,在ImageNet圖像比賽中取得了歷史上最佳成績。其top-5錯誤率僅為15.3%,而第二名的錯誤率則高達26.2%。這一結果震驚了世界,AI競賽從此開始進入新的階段。AlexNet擁有60 million個單精度浮點參數,存儲到磁盤上需要240MB的空間。作者表示,受限于顯存和算力,這已經是他在兩塊GTX 580 3GB GPU上能夠實現的極限了。他相信,如果有更快的GPU,他可以得到更好的分類結果。

從那時起,幾乎所有的AI研究員都開始使用GPU進行算法領域的探索與突破。與此同時,GPU的架構設計也越來越傾向于提供除了3D能力以外的通用算力,這種設計理念被稱為General-Purpose GPU(GPGPU)。

2011年,TESLA GPU計算卡發(fā)布,標志著NVIDIA正式將用于計算的GPU產品線獨立出來。憑借其架構上的優(yōu)勢,GPU在通用計算及超級計算機領域逐漸取代CPU成為主角。

隨著GPU技術的發(fā)展,AI算法研究也突飛猛進。2014年前后,香港中文大學的Sun Yi等人將卷積神經網絡應用在人臉識別領域,采用20萬訓練數據,在LFW數據集上首次達到超過人類水平的識別精度。2015年10月,AlphaGo擊敗樊麾,成為第一個無需讓子即可在19路棋盤上擊敗圍棋職業(yè)棋手的電腦圍棋程序,創(chuàng)造了歷史,并于2016年1月發(fā)表在知名期刊《自然》。

在2022年圣誕節(jié)前夕,所有硅谷公司都經歷了一場震撼教育——11月30日,OpenAI發(fā)布了聊天機器人ChatGPT。它可以自動生成文章和詩歌,像人類一樣通過自然的互動回答問題。其性能之高震撼了世界,點燃了生成式AI的熱潮。

在CES 2023上,奔馳宣布成為美國首家獲得L3自動駕駛認證的廠商。AI算法在越來越多的領域的能力上接近甚至超越人類,這意味著AI可以幫助降低人們的負擔,釋放人類潛力,同時也帶來商機與產業(yè)化的機會。

添加圖片注釋,不超過 140 字(可選)

通用算力、專用算力,GPGPU與AI DSA相向而行,殊途同歸。

在2014年,世界上第一款supercomputer on a module, Jetson TX1問世,TX1采用256個NVIDIA Maxwell架構CUDA cores 提供了超過1 TeraFLOPs性能。旨在能夠為當時最新視覺計算應用提供所需的性能和能效。定位為Deep Learning, Computer Vision, Graphics、GPU Computing的嵌入式平臺。

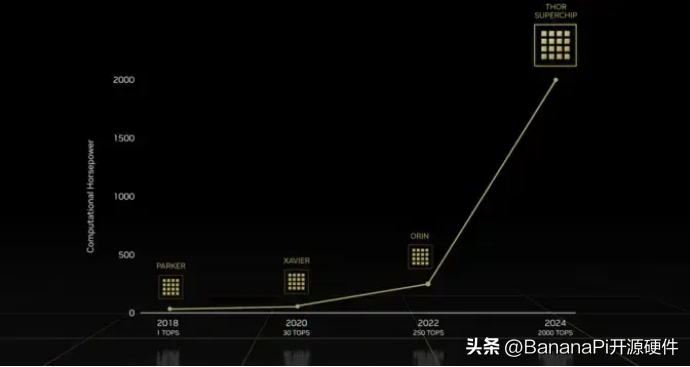

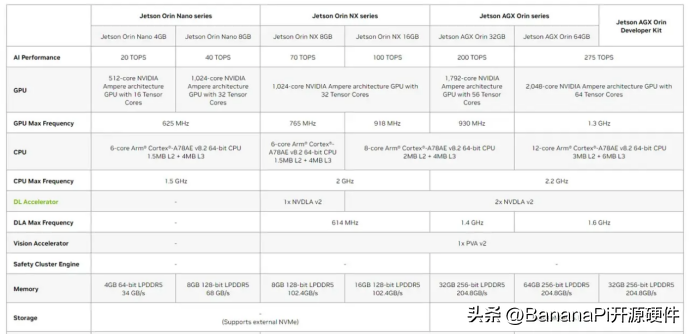

圖四:NVIDIA邊緣AI平臺路線圖

該系列產品從2018年的1T算力的TX1一路發(fā)展到2024年預計發(fā)售的擁有2000T算力的THOR平臺。值得注意的是在XAVIER與ORIN平臺上有超過一半的標稱算力是由DLA提供。

圖五:Jetson Orin Technical Specifications

采用DLA可以加速部分計算密集的算子。與采用GPGPU計算相比,在損失部分推理精度的前提下,采用DLA加速推理計算不僅速度更快,而且能耗更低。然而,這并非免費午餐。首先,要同時利用GPGPU與DLA兩塊算力,軟件上就需要精巧的異步設計,以實現CPU負載、編解碼模塊、圖像處理模塊、GPGPU以及DLA五者的流水化并行處理。然而,在THOR這代自動駕駛平臺產品中,DLA提供的算力甚至直接被砍掉,其原因目前尚不清楚。但根據NVIDIA的官方文檔顯示,DLA支持約15種主要AI算子的執(zhí)行,不支持的算子類型將回退到GPGPU進行運算。筆者推測,可能是基于TensorCore指令拓展獲得的算力有更強的通用性和可編程性,能夠更好地滿足業(yè)界的需求。

TensorCore實際上也是一種DSA的設計理念的體現。隨著AI算法的多年發(fā)展,業(yè)界也逐漸意識到AI的算力需求逐漸收斂到了矩陣計算能力上。通過專用的指令加速矩陣乘法計算,從而加速AI計算,這一理念已被業(yè)界廣泛接受。

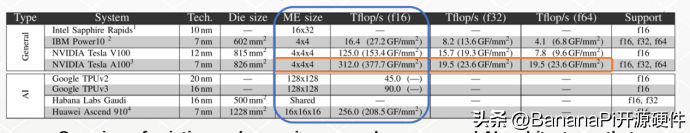

圖六:通用及專用架構的矩陣加速引擎設計

THOR平臺的CUDA引入了Transformer Engine,用于加速基于attention機制的DL算法,這正是目前備受關注的ChatGPT網絡模型的重要組成部分。此外,THOR平臺還引入了對8-bit floating point (FP8) 精度的支持,這是INT8的替代品,能夠在同等的位寬下提供更高的精度。NVIDIA在其Edge平臺產品線上開始放棄專有的定制化大算力,逐步在通用算力的基礎上增加領域的定制化。這與其發(fā)布會上反復強調的提高開發(fā)效率、加快軟件迭代、算法迭代的目標相吻合。

GPU也是一種DSA,其發(fā)展證明了DSA取得的成功。DSA、GPU、AI,這是個互相成就的故事。NVIDIA的GPGPU硬件的成功與其CUDA生態(tài)豐富的算力軟件包、易于使用的編程接口、優(yōu)秀的編譯器密不可分。因此,對于DSA算力硬件來說,這些都是走向商業(yè)成功的必要條件。

自TX1推出以來,對標TX1的競品層出不窮。TX1的算力來自于GPGPU,而更加客制化的ASIC,利用卷積操作的空間局部性進行數據復用的精妙設計,在達到同等甚至更高算力的同時硬件成本更低。最普遍的設計是一個高能效比的CPU小核如Arm Cortex A7/A53加固化的2D圖像處理(CV)模塊與固化的神經網絡處理(DNN/NPU)模塊。

然而,由于小CPU的計算能力受限,其主要負責應用軟件的任務調度部分。AI應用的前處理(非DNN算法模型部分)主要由2D圖像處理模塊承接。然而,前處理是非常碎片化的算法,除了個別的插值、顏色域轉換功能,幾乎所有圖像處理軟件都會用到,其他所需功能非常廣泛。這包括OpenCV的核心函數、圖像處理函數,其中每個大類中的子方法又會有若干個,無法確定哪些功能需要被固化。這還不包括3D數據處理能力與特征描述子的使用。算法廠商的需求各不相同,固化的多了會浪費面積,固化的少了產品開發(fā)的難度將大幅提升。

ONNX是一種專為機器學習設計的開放式文件格式,用于存儲訓練好的模型,使得來自不同人工智能框架訓練的網絡模型可以以相同的格式進行存儲。ONNX的規(guī)范及代碼主要由微軟、亞馬遜、Facebook和IBM等公司共同開發(fā)。以NVIDIA的AI軟件生態(tài)中最著名的DNN推理開發(fā)工具庫TensorRT為例,5.1版本支持87個ONNX算子,到了7.1版本支持的ONNX算子數量增加至108個。由于功能高度固化的ASIC無法支持新增的算子計算類型,這將越來越限制算法的迭代。對于在此基礎上進行AI產品開發(fā)的算法工程師來說,這幾乎等同于在戴著鐐銬跳舞。

Google公司研發(fā)了張量處理單元(TPU),TPU v1于2015年投入生產,并被谷歌內部用于其應用程序。TPU是一種專為AI領域提供算力的ASIC,利用了神經網絡對于數值精度不敏感的特性,其核心思想是采用低精度矩陣Systolic Array提供巨大算力,同時提供滿足AI需求的最小化運算功能。TPUv1的云服務從未對用戶開放使用,而TPUv2以及后續(xù)版本被廣泛應用于谷歌的搜索排序、語音識別、以圖搜圖、谷歌翻譯等領域。

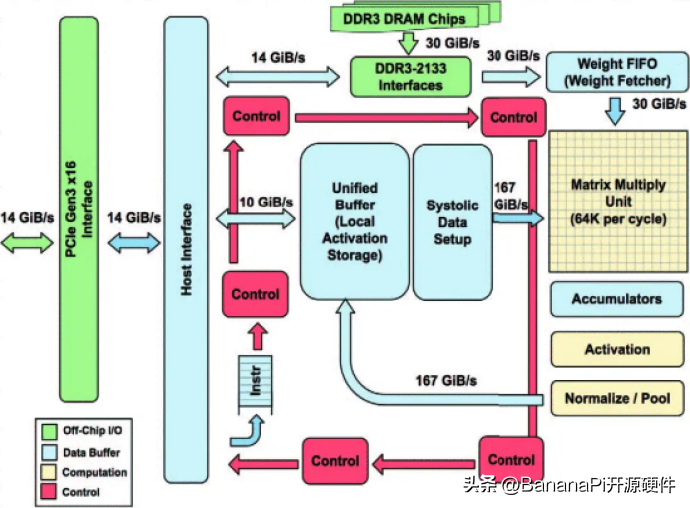

圖七:TPUv1架構圖

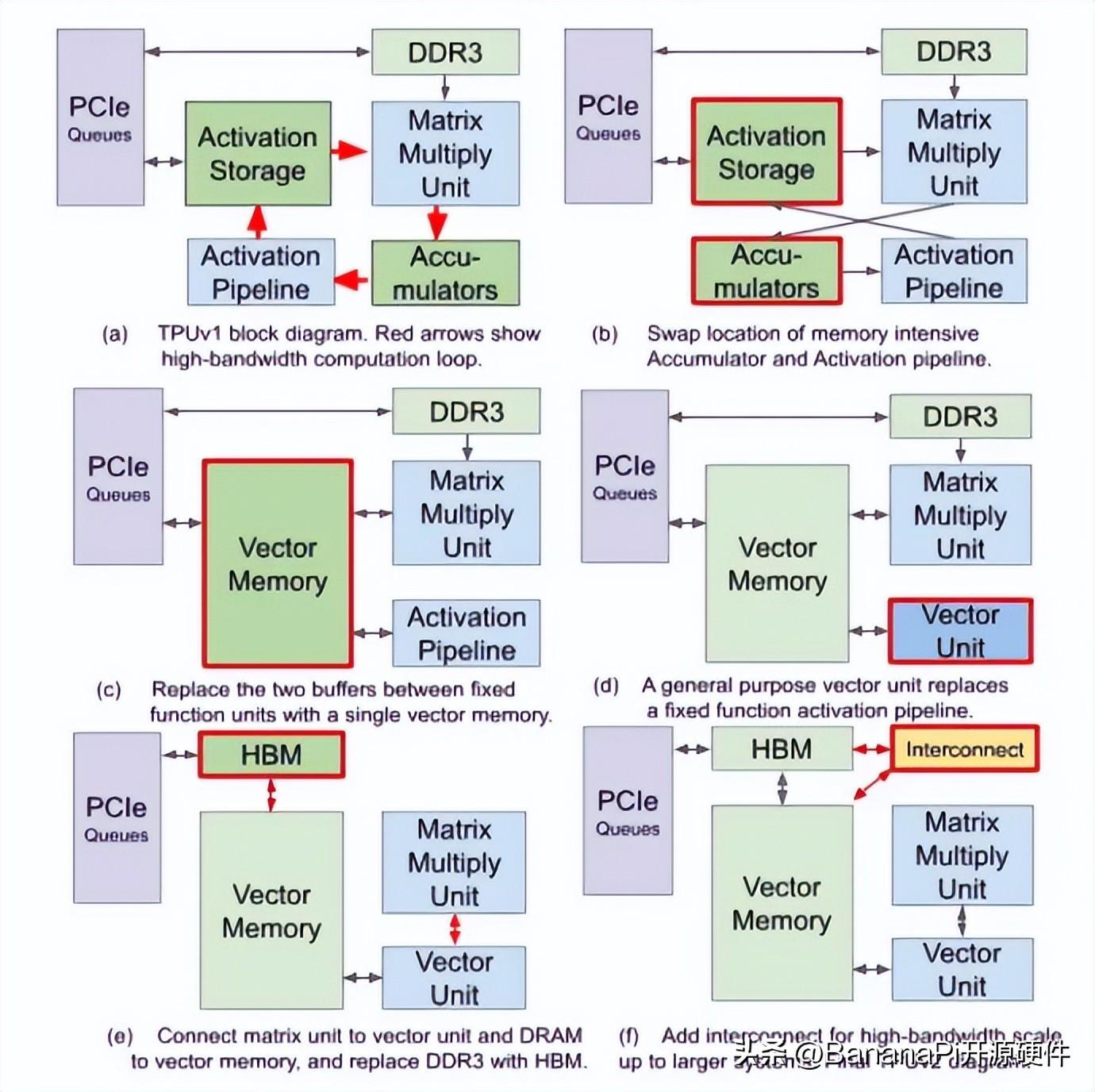

在TPUv1版本的硬件架構圖上,我們可以看到Matrix Multiply模塊提供了每時鐘64K次操作的超大算力,緊隨其后的是Activation(激活)、Normalize/Pool(歸一化/池化)等運算。到了TPUv2,通用的Vector單元取代了v1版本中activation pipe中的固定功能。

圖八:TPUv1到TPUv2數據通路的轉變

在數據中心內運行了一年多的TPU后,谷歌發(fā)現它們?yōu)闄C器學習提供了數量級更好的每瓦優(yōu)化性能,相當于未來七年左右的快速進步(相當于三代摩爾定律)。這是谷歌CEO對TPU的評價。

在2021年,David Patterson對TPU十年的演進進行了總結,其中指出DSA既要專門優(yōu)化,又要保持靈活性。TPUv2引入的通用算力為TPU提供了更強大的功能,不僅局限于TPUv1的模型推理,還能進行模型訓練,這往往需要更復雜的運算。谷歌通過XLA(一種用于TPU的高度定制優(yōu)化的機器學習編譯器)為用戶提供云服務,為特別是在這一生態(tài)系統(tǒng)下的用戶提供了便捷的通用編程接口,從而提升了用戶體驗。

DSA成功帶來的啟示

通過以上成功案例,我們可以發(fā)現GPGPU和TPU的迭代都有一個共同點,那就是它們通過越來越高度的架構定制,帶來了越來越強大的專用算力,同時保留或新增通用的算力。通過高度優(yōu)化的編譯器和豐富的軟件棧,用戶能夠輕松地充分利用硬件算力。顯然,在CPU平臺上,通用算力、編譯器和軟件棧都是最豐富、最成熟的。因此,對于CPU而言,“Domain-specific architecture design is all you need”。

RISC-V DSA能否把AI算力做好

GPU的發(fā)展?jié)M足了大型DNN網絡的內存帶寬和計算能力的需求。由于計算能力的提高和可用數據量的增加,DNN已經演變成更寬、更深的架構。DNN中的層數可以達到數萬層,參數達數十億,研究人員很難在硬件資源(例如內存、帶寬和功耗)有限的便攜式設備中部署DNN。迫切需要在資源受限的邊緣設備(例如手機、嵌入式設備、智能可穿戴設備、機器人、無人機等)中有效部署DNN的方法。因此,AI科學家們又開展了AI模型小型化的研究,即用最少的參數量、最少的計算量去達到想要的模型精度。因此,ShuffleNet、MobileNet、網絡架構搜索(NAS)算法等輕量級神經網絡結構開始被推出,能夠在很少的參數量上達到與大參數量模型接近的精度。同時,神經網絡的參數剪枝、參數量化、緊湊網絡、知識蒸餾、低秩分解、參數共享、混合方式等壓縮技術與計算加速技術開始成為研究的熱門。

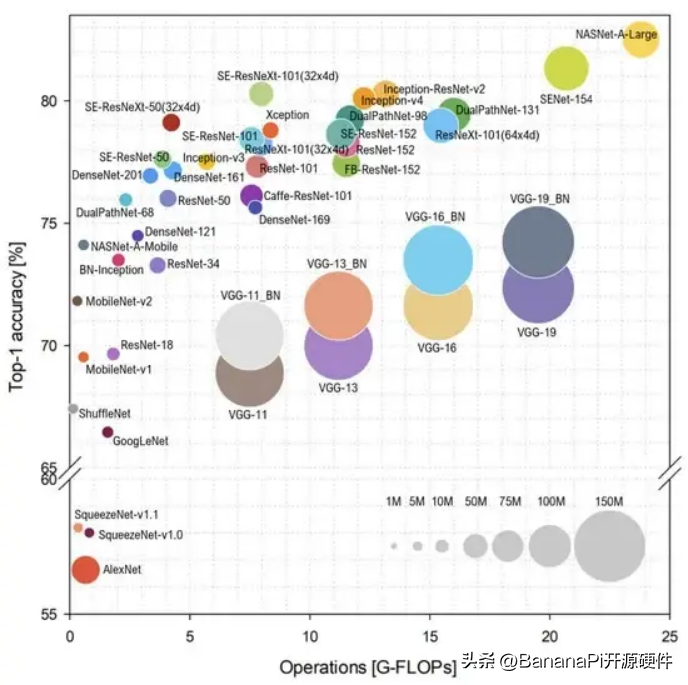

圖九:圖像分類模型性能與模型算力對應關系

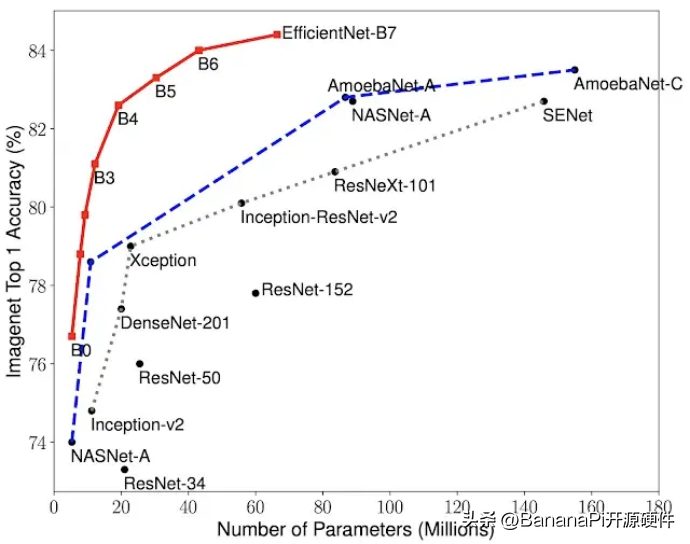

圖十:圖像分類模型性能與模型大小對應關系

EfficientNet-B0是AutoML MNAS開發(fā)的基線網絡,而Efficient-B1到B7是基線網絡擴展得到的。特別地,EfficientNet-B7達到了最新的84.4% top-1 / 97.1% top-5精度,同時比現有最好的CNN小8.4倍。

與此同時,AI科學家們也發(fā)現提升模型參數量帶來模型精度提升的效應在減弱。如圖九所示,在圖像分類的任務上,模型的精度隨著參數量的提升越來越接近85% Top-1準確率的平臺。這意味著在成熟的視覺領域,我們獲得一定AI能力所需的算力需求是趨于收斂的。因此,給定任務、給定模型、給定圖像處理的幀率,我們可以確定我們的算力需求。完成指定領域的任務,最終的算力需求是可以被定義并趨同的。

這一切意味著AI不再是超級算力、超級計算機上獨享的能力。AI將會在任何地方,這同時也對我們的通用處理器發(fā)起了挑戰(zhàn)。

DSA可以有效、高效地完成領域任務,然而C++編程、CPU上的經驗可能就無法被利用上。在David Patterson的十大經驗教訓中也提到DSA的軟件棧目前不及CPU,在編譯器領域還不夠成熟。因此,如果DSA能夠利用CPU的豐富且成熟的軟件棧優(yōu)勢,將會是一種強大的組合。

例如,CUDA提供了多種常用編程語言的支持,并通過關鍵字拓展的方式進行并行軟件編程,加上其本身卓越的通用計算能力,使得其開發(fā)生態(tài)越來越壯大。有些實力雄厚的客戶甚至放棄使用TensoRT,通過自身的GPGPU技術積累開發(fā)出適合自身業(yè)務需求的更高效的軟件,比NVIDIA提供的TensoRT性能提高了一倍。

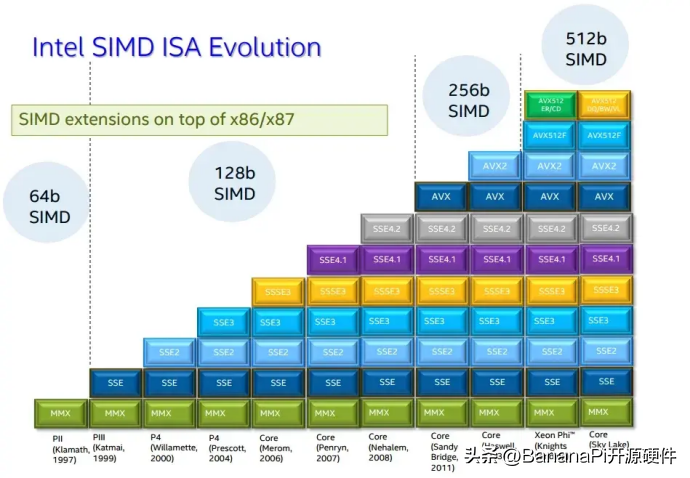

那么我們何不在CPU上提供AI算力呢?正如過去在CPU上長出適合多媒體處理的算力一樣。在過去的時代,即使在頻率提升緩慢的情況下,CPU上的浮點能力由于SIMD拓展得到了巨大的提升,并隨著SIMD數據并行寬度的提升而有一個線性的增長。

圖十一:Intel處理器發(fā)布年份與算力峰值構成

圖十二:SIMD計算指令的位寬發(fā)展

近年來,Intel x86 CPU處理器上的SIMD由64bit的MMX(Multi Media eXtension,多媒體擴展指令集)增長到了512bit的數學拓展AVX512與AI拓展VNNI,使得在四核Core i7-1185G7 @ 3.00GHz的處理器上可以獲取3Tops的算力。提供了AI所謂的MAC能力,加之本身的通用SIMD計算能力是可以有效COVER如智能機器人、智能視頻、語音終端設備等AI場景。但此等SOC做AI終端過于奢侈,且定位還是通用而不是AI DSA。

Intel最新的AMX矩陣拓展架構、Arm架構下的SME矩陣拓展架構以及IBM的AMM指令集更是將CPU能提供的AI算力又提升了一個臺階。在架構代號為Sapphire Rapids的server級處理器上可以通過AMX獲得每時鐘周期1024個mac是VNNI拓展提供的算力的8倍(128個mac每時鐘周期)。

圖十三:Intel矩陣指令拓展相較于向量指令拓展提升巨大

CPU上完全可以長出使能AI應用大算力,正如過去長出了適合多媒體處理的算力。

為什么是RISC-V?

如果要對CPU架構進行領域定制,需要獲取對應的架構級授權(Architectural License)。區(qū)別于IP Core的授權,架構級授權特指指令集(ISA)授權,允許客戶自行定制優(yōu)化。

關于CPU業(yè)界兩大陣營x86與ARM的架構授權的情況是什么樣的呢?x86的專利主要掌握在英特爾和AMD這兩家公司手中,到目前為止國內沒有任何一家廠商擁有x86的架構級授權,海光信息與兆芯采用的是 x86 架構 IP 內核授權模式。海思、飛騰均已經獲得 ARMv8架構的永久授權。盡管 ARM 此前表態(tài) ARMv9 架構不受美國出口管理條例(EAR)約束,華為海思等國內CPU產商依然可獲授權,但是ARMv9不再提供永久授權,采用 ARM 架構仍有長期隱患。而且即使在擁有ARM架構級授權的情況下做出指令集定制與改動,也必須經由ARM參與支持修改才可以,否則將觸發(fā)違約條款。

RISC-V 因其相對精簡的指令集架構(ISA)以及開源寬松的 BSD 協議使得Fabless可以基于RISC-V架構進行任意的架構拓展與定制。相信RISC-V DSA可以利用其經典的CPU的編程模型與相對低成本獲取的AI算力,加之標準RISC-V Vector拓展提供的通用算力,能夠給AI嵌入式場景下1-10T算力需求范圍的AI產業(yè)應用帶來全新的商業(yè)化硬件方案。

-

芯片

+關注

關注

455文章

50798瀏覽量

423501 -

cpu

+關注

關注

68文章

10860瀏覽量

211727 -

RISC-V

+關注

關注

45文章

2277瀏覽量

46157 -

banana pi

+關注

關注

1文章

113瀏覽量

3021 -

AI算力

+關注

關注

0文章

72瀏覽量

8674

發(fā)布評論請先 登錄

相關推薦

如何快速上手進迭時空K1 RISC-V開發(fā)板:Banana Pi BPI-F3

Banana Pi BPI-F3 進迭時空RISC-V架構下,AI融合算力及其軟件棧實踐

香蕉派 BPI-CanMV-K230D-Zero 采用嘉楠科技 K230D RISC-V芯片設計

Banana Pi BPI-CanMV-K230D-Zero :AIoT 應用的 Kendryte K230D RISC-V

Banana Pi BPI-F3 進迭時空 SpacemiT K1 RISC-V板 運行OpenWRT

RISC-V架構

RISC-V芯片企業(yè) 進迭時空完成Pre A+ 輪融資

香蕉派發(fā)布RISC-V架構BPI-F3開發(fā)板

Banana Pi BPI-F3 進控時空SpacemiT K1芯片場景功耗測試

Banana Pi BPI-F3 進迭時空 RISC-V K1芯片開發(fā)板支持8G/16G內存

RT-Thread攜手進迭時空:共建RISC-V實時計算生態(tài)

進迭時空引領AI CPU創(chuàng)新,Key Stone K1芯片訂單破萬

業(yè)內首顆8核RISC-V終端AI CPU量產芯片K1,進迭時空與中國移動用芯共創(chuàng)AI+時代

RISC-V架構下DSA-AI算力的更多可能性:Banana Pi BPI-F3進迭時空

RISC-V架構下DSA-AI算力的更多可能性:Banana Pi BPI-F3進迭時空

評論