Silicon Labs PCI Express Gen 4時鐘為數(shù)據(jù)中心和消費類產(chǎn)品設(shè)計確立新的性能標(biāo)桿

新型Si522xx PCIe時鐘系列產(chǎn)品提供業(yè)界領(lǐng)先的抖動性能、電源效率和單芯片集成度

Silicon Labs(亦稱“芯科科技”,NASDAQ:SLAB)日前宣布針對PCI Express? (PCIe?) Gen 1/2/3/4應(yīng)用推出一系列具有業(yè)界最低抖動、最高集成度、最低功耗的時鐘發(fā)生器產(chǎn)品。Silicon Labs新型Si522xx PCIe時鐘發(fā)生器滿足PCIe Gen 4的嚴(yán)格要求且提供20%的抖動裕度,同時為PCIe Gen 3抖動規(guī)格提供60%的抖動裕度。開發(fā)人員現(xiàn)在可以信心十足地采用Silicon Labs PCIe時鐘設(shè)計出符合PCIe標(biāo)準(zhǔn)的解決方案,而且可以獲得最大限度的抖動裕度,降低產(chǎn)品開發(fā)風(fēng)險。請點擊“閱讀原文”探索完整的產(chǎn)品發(fā)布新聞!

憑借兼容PCIe Gen 4和高達(dá)12路時鐘輸出,Si522xx時鐘非常適合在數(shù)據(jù)中心應(yīng)用中提供低抖動PCIe時鐘生成和分發(fā),無需添加額外的獨立時鐘緩沖器。除了提供一流的抖動裕度外,Si522xx時鐘完全符合PCIe Gen 4通用時鐘和獨立展頻分離參考(SRIS)架構(gòu)。

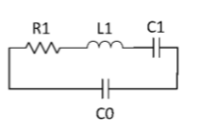

Si522xx器件輸出驅(qū)動器利用了Silicon Labs創(chuàng)新的推挽式HCSL技術(shù),消除了采用傳統(tǒng)恒流輸出驅(qū)動器技術(shù)的PCIe時鐘所需的片外終端電阻。內(nèi)部電源濾波能夠防止電源噪聲降低時鐘抖動性能,器件數(shù)量和占板面積與競爭解決方案相比減少30%。

設(shè)計電池供電應(yīng)用(例如數(shù)碼相機(jī))的開發(fā)人員特別關(guān)注功耗。2路輸出的Si52202時鐘特別針對低功耗1.5-1.8V應(yīng)用進(jìn)行了優(yōu)化,為PCIe應(yīng)用提供業(yè)界最低功耗。它采用小尺寸3mmx 3mm 20-QFN封裝,器件尺寸比競爭解決方案小45%。

Silicon Labs時鐘產(chǎn)品高級營銷總監(jiān)James Wilson表示:“Silicon Labs持續(xù)推動PCI Express時鐘的創(chuàng)新、性能和集成度。隨著Si522xx系列產(chǎn)品的發(fā)布,我們現(xiàn)在可以完全滿足整個PCIe應(yīng)用需求,覆蓋從服務(wù)器和存儲到工業(yè)和消費類應(yīng)用。”

由于時鐘抖動是所有PCIe應(yīng)用的關(guān)鍵設(shè)計參數(shù),Silicon Labs為開發(fā)人員提供了免費的PCIe Gen 1/2/3/4抖動測量工具,請瀏覽網(wǎng)站:www.silabs.com/pcie-learningcenter

Si522xx PCIe時鐘發(fā)生器系列產(chǎn)品已經(jīng)量產(chǎn),可提供樣片,支持多種輸出路數(shù)選項。Si52212、Si52208和Si52204時鐘提供12、8和4路100MHzPCIe時鐘輸出,以及1路25MHzLVCMOS參考時鐘輸出。Si52202時鐘支持2路100MHz PCIe時鐘輸出。樣片可在2周內(nèi)發(fā)貨,量產(chǎn)產(chǎn)品可在4周內(nèi)發(fā)貨。

Silicon Labs新型Si52204-EVB開發(fā)套件提供快速、方便的PCIe時鐘評估。有關(guān)Si522xx PCIe時鐘系列產(chǎn)品或訂購樣片和開發(fā)套件的更多信息,請瀏覽網(wǎng)站:https://www.silabs.com/products/timing/clocks

-

Silicon

+關(guān)注

關(guān)注

0文章

134瀏覽量

38595 -

時鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

200瀏覽量

67302

原文標(biāo)題:【新品】PCIe Gen 4時鐘刷新數(shù)據(jù)中心性能標(biāo)竿!

文章出處:【微信號:SiliconLabs,微信公眾號:Silicon Labs】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

高性能抖動衰減器和時鐘發(fā)生器的推薦晶體、TCXO和OCXO參考手冊(之一)

CDCE421A全集成、寬范圍、低抖動晶體振蕩器時鐘發(fā)生器數(shù)據(jù)表

CDCE925,CDCEL925低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

CDCEx937低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

CDCE(L)913低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

CDCM61004四路輸出、集成VCO、低抖動時鐘發(fā)生器數(shù)據(jù)表

CDCM61002兩路輸出、集成VCO、低抖動時鐘發(fā)生器數(shù)據(jù)表

LMK05318B超低抖動時鐘發(fā)生器數(shù)據(jù)表

LMK03318超低噪聲抖動時鐘發(fā)生器系列數(shù)據(jù)表

具有兩個獨立PLL、八路輸出、集成EEPROM的LMK03328超低抖動時鐘發(fā)生器數(shù)據(jù)表

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

CDCE6214Q1TM超低功耗時鐘發(fā)生器數(shù)據(jù)表

CDCE6214-Q1超低功耗時鐘發(fā)生器數(shù)據(jù)表

毫微微時鐘網(wǎng)絡(luò)同步器、抖動衰減器和時鐘發(fā)生器RC32112A 數(shù)據(jù)表

FemtoClock2抖動衰減器和時鐘發(fā)生器RC325008A數(shù)據(jù)手冊

業(yè)界最低抖動、最高集成度、最低功耗的時鐘發(fā)生器

業(yè)界最低抖動、最高集成度、最低功耗的時鐘發(fā)生器

評論