多年前,無線時代(Beamsky)發布了一篇文章關于DDR布線指導的一篇文章,當時在網絡上很受歡迎,有很多同行參與了轉載。如今看來,那篇文章寫得不夠好,邏輯性不強,可操作性也不強。

在近幾年的硬件產品開發中,本人總結出了一套DDR布線方法,具有高度的可行性,于是本人再次編寫一份這樣的文章,除了講述DDR布線規則,還想講述一下布線過程,采用本人的布線過程可以少走很多彎路。本文即將講到的所有方法,無線時代(Beamsky)都經過實際檢驗。

DDR布線通常是一款硬件產品設計中的一個重要的環節,也正是因為其重要性,網絡上也有大把的人在探討DDR布線規則,有很多同行故弄玄虛,把DDR布線說得很難,我在這里要反其道而行之,講一講DDR布線最簡規則與過程。

如果不是特別說明,每個步驟中的方法同時適用于DDR1,DDR2和DDR3。PCB設計軟件以Cadence Allgro 16.3為例。

第一步,確定拓補結構(僅在多片DDR芯片時有用)

首先要確定DDR的拓補結構,一句話,DDR1/2采用星形結構,DDR3采用菊花鏈結構。

拓補結構只影響地址線的走線方式,不影響數據線。以下是示意圖。

星形拓補就是地址線走到兩片DDR中間再向兩片DDR分別走線,菊花鏈就是用地址線把兩片DDR“串起來”,就像羊肉串,每個DDR都是羊肉串上的一塊肉,哈哈,開個玩笑。

第二步,元器件擺放

確定了DDR的拓補結構,就可以進行元器件的擺放,有以下幾個原則需要遵守:

原則一,考慮拓補結構,仔細查看CPU地址線的位置,使得地址線有利于相應的拓補結構

原則二,地址線上的匹配電阻靠近CPU

原則三,數據線上的匹配電阻靠近DDR

原則四,將DDR芯片擺放并旋轉,使得DDR數據線盡量短,也就是,DDR芯片的數據引腳靠近CPU

原則五,如果有VTT端接電阻,將其擺放在地址線可以走到的最遠的位置。一般來說,DDR2不需要VTT端接電阻,只有少數CPU需要;DDR3都需要VTT端接電阻。

原則六,DDR芯片的去耦電容放在靠近DDR芯片相應的引腳。

以下是DDR2的元器件擺放示意圖(未包括去耦電容),可以很容易看出,地址線可以走到兩顆芯片中間然后向兩邊分,很容易實現星形拓補,同時,數據線會很短。

以下是帶有VTT端接電阻的DDR2元器件擺放示意圖,在這個例子中,沒有串聯匹配電阻,VTT端接電阻擺放在了地址線可以到達的最遠距離。

以下是DDR3元器件擺放示意圖,請注意,這里使用的CPU支持雙通道DDR3,所以看到有四片(參考設計是8片)DDR3,其實是每兩個組成一個通道,地址線沿著圖中綠色的走線傳遞,實現了菊花鏈拓補。

地址線上的VTT端接電阻擺放在了地址線可以到達的最遠的地方。同樣地,數據線上的端接電阻也放置在了靠近DDR3芯片的位置,數據線到達CPU的距離很短。同時,可以看到,去耦電容放置在了很靠近DDR3相應電源引腳的地方。

第三步,設置串聯匹配電阻的仿真模型

擺放完元器件,建議設置串聯匹配電阻的仿真模型,這樣對于后續的布線規則的設置是有好處的。

點擊Analyze?SI/EMI Sim?Model Assignment,如下圖。

然后會出來Model Assignment的界面,如下圖:

然后點擊需要設置模型的器件,通常就是串聯匹配電阻,分配或創建合適的仿真的模型,如果不知道如何創建,請在互聯網上搜索或發郵件給無線時代(Beamsky)。

分配好仿真模型之后的網絡,使用Show Element命令,可以看到相關的XNET屬性,如下圖:

第四步,設置線寬與線距

1. DDR走線線寬與阻抗控制密切相關,經常可以看到很多同行做阻抗控制。對于純數字電路,完全有條件針對高速線做單端阻抗控制;但對于混合電路,包含高速數字電路與射頻電路,射頻電路比數字電路要重要的多,必須對射頻信號做50歐姆阻抗控制,同時射頻走線不可能太細,否則會引起較大的損耗,所以在混合電路中,本人往往舍棄數字電路的阻抗控制。到目前為止,本人設計的混合電路產品中,最高規格的DDR是DDR2-800,未作阻抗控制,工作一切正常。

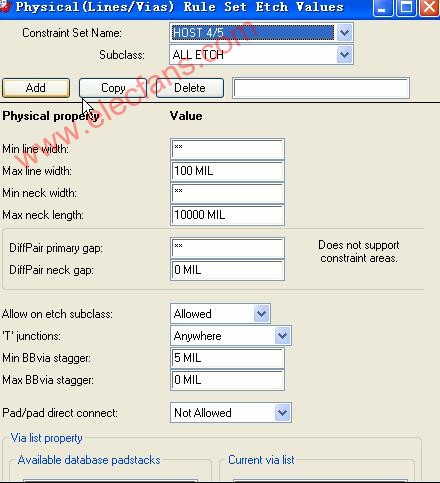

2. DDR的供電走線,建議8mil以上,在Allegro可以針對一類線進行物理參數的同意設定,我本人喜歡建立PWR-10MIL的約束條件,并為所有電源網絡分配這一約束條件,如下圖。

3. 線距部分主要考慮兩方面,一是線-線間距,建議采用2W原則,即線間距是2倍線寬,3W很難滿足;二是線-Shape間距,同樣建議采用2W原則。對于線間距,也可以在Allegro中建立一種約束條件,為所有DDR走線(XNET)分配這樣的約束條件,如下圖:

4. 還有一種可能需要的規則,就是區域規則。Allegro中默認的線寬線距都是5mil,在CPU引腳比較密集的時候,這樣的規則是無法滿足的,這就需要在CPU或DDR芯片周圍設定允許小間距,小線寬的區域規則,如下圖:

第五步,走線

走線就需要注意的內容比較多,這里只做少許說明。

-

所有走線盡量短

-

走線不能有銳角

-

盡量少打過孔

-

保證所有走線有完整的參考面,地平面或這電源平面都可以,對于交變信號,地與電源平面是等電位的

-

盡量避免過孔將參考面打破,不過這在實際中很難做到

-

走完地址線和數據后,務必將DDR芯片的電源腳,接地腳,去耦電容的電源腳,接地腳全部走完,否則在后面繞等長時會很麻煩的

下圖是完成的DDR走線,但尚未繞等長:

第六步,設置等長規則

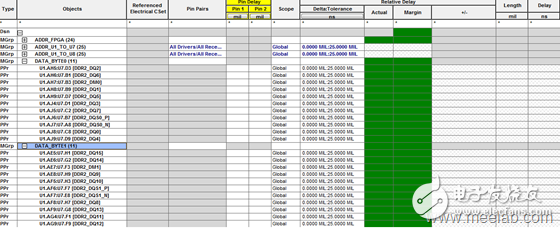

對于數據線,DDR1/2與DDR3的規則是一致的:每個BYTE與各自的DQS,DQM等長,即DQ0:7與DQS0,DQM。等長,DQ8:15與DQS1,DQM1等長,以此類推。

DDR2數據線等長規則舉例

DDR3數據線等長規則舉例

地址線方面的等長,要特別注意,DDR1/2與DDR是很不一樣的。

對于DDR1/2,需要設定每條地址到達同一片DDR的距離保持等長,如下圖:

對于DDR3,地址線的等長往往需要過孔來配合,具體的規則均綁定在過孔上和VTT端接電阻上,如下圖。可以看到,CPU的地址線到達過孔的距離等長,過孔到達VTT端接電阻的距離也等長。

補充一點,很多時候,地址線的等長要求不嚴格,這一點我還沒有嘗試過。在本人設計的這些產品中,地址線,數據線都做了25mil的Relative Propagation Delay的等長規則設定。關于等長規則設定的細節在這里不再贅述,有興趣的話,可以發郵件給無線時代(Beamsky)。

第七步,繞等長

完成等長規則的設定后,最后一步也是工作量最大的一步:繞等長。

在這一步,我認為只有一點規則需要注意:盡量采用3倍線寬,45度角繞等長,如下圖:

繞等長完成后,最好把DDR相關網絡鎖定,以免誤動。

到這里,DDR走線就已經完成了,在本人設計過的三,四十種產品中,都是按照上面的規則與過程完成的,DDR2最高規格是DDR2-800,512MB,DDR3最高規格是DDR3-1600,1GB,都可以很穩定的工作,無論性能還是可靠性,都未曾出過問題。

-

DDR

+關注

關注

11文章

712瀏覽量

65341 -

Cadence

+關注

關注

65文章

921瀏覽量

142139 -

布線

+關注

關注

9文章

772瀏覽量

84330

原文標題:DDR布線最簡規則與過程,很全很專業!

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Allegro布線規則的設置

DDR布線規則及一些布線過程總結

DDR布線規則及一些布線過程總結

評論