電源完整性的隱性殺手

在現(xiàn)代高速電子設(shè)計中,電源完整性(Power Integrity,PI)問題已成為影響系統(tǒng)性能的關(guān)鍵因素之一。在電源完整性問題中,同步開關(guān)噪聲(Simultaneous Switching Noise,SSN)是一個經(jīng)常被提及但又容易被忽視的重要概念。 同步開關(guān)噪聲(SSN),又被稱為地彈(Ground Bounce)或數(shù)字噪聲(Digital Noise),是指在數(shù)字電路中,當(dāng)大量輸出驅(qū)動器同時切換狀態(tài)時產(chǎn)生的電源噪聲。這個現(xiàn)象主要發(fā)生在集成電路的電源與地平面之間,通常在高速數(shù)字電路和系統(tǒng)中尤為明顯。

同步開關(guān)噪聲產(chǎn)生的原因

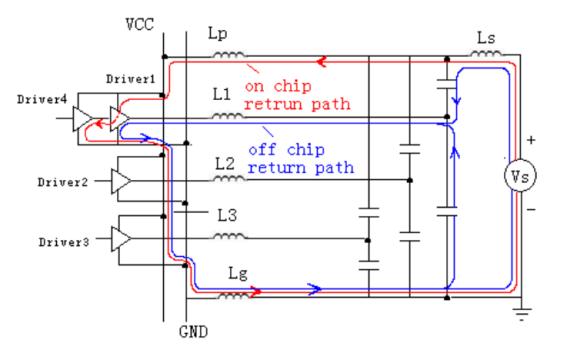

大量的芯片同步切換時,產(chǎn)生的瞬態(tài)電流在電源或地平面上產(chǎn)生大量噪聲,因此 SSN 也被稱為 Δi 噪聲。當(dāng)信號從低電平切換到高電平時,需要從電源模塊吸收能量,電流開始流動,但因?yàn)槲覀兊幕ミB設(shè)計不是理想的,電源走線上會有阻抗,阻擋電流立刻到達(dá)芯片引腳。另外寄生電感也會使電路在開關(guān)電流的存在下帶來電壓波動,形成電壓噪聲。I/O 開關(guān)速度越快,瞬時電流變化越快,在電流回路上產(chǎn)生的噪聲越大。這種噪聲會通過電源系統(tǒng)傳播,帶來的電源完整性問題影響整個系統(tǒng)的性能。

同步開關(guān)噪聲的影響

·信號完整性:SSN 會對信號完整性產(chǎn)生嚴(yán)重影響,導(dǎo)致信號過沖、下沖、抖動等問題,甚至可能引發(fā)誤碼。

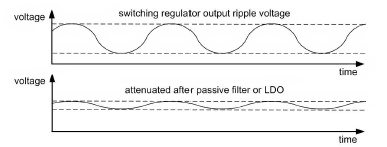

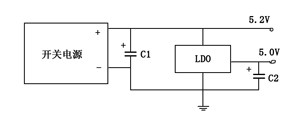

·電源完整性:SSN 會在電源系統(tǒng)中引起瞬態(tài)電壓跌落,導(dǎo)致電源不穩(wěn)定,影響敏感的模擬和數(shù)字電路的正常工作。

·電磁干擾(EMI):由于 SSN 會在電源平面上產(chǎn)生高頻噪聲,這種噪聲很容易通過 PCB 板的走線或電纜輻射出去,增加系統(tǒng)的電磁輻射水平。

如何減少同步開關(guān)噪聲的負(fù)面影響

·增加電源與地平面的耦合,減小寄生電感。

·使用多層板設(shè)計,將電源與地平面相互疊加,提高電源平面的平滑性。

·在關(guān)鍵位置放置去耦電容,尤其是靠近驅(qū)動器或IC的電源引腳處,提供局部電源。

·采用星形拓?fù)浣Y(jié)構(gòu),將電源從電源輸入端到各個負(fù)載分配得當(dāng),減少電流突變對其他電路的影響。

·采用電源完整性仿真工具進(jìn)行預(yù)先評估和優(yōu)化設(shè)計。

如何使用仿真工具優(yōu)化設(shè)計

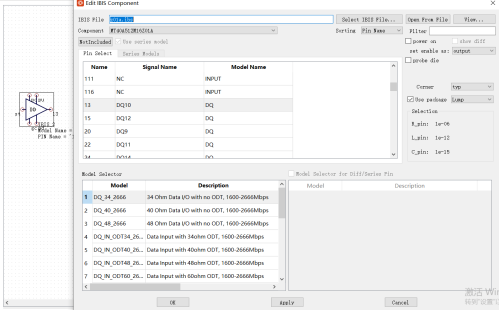

使用巨霖 SIDesigner,可以對 IBIS 模型開放供電接口,引入 SSN 的分析。

在 SIDesigner 的 IBIS 模型“IC”中,導(dǎo)入 IBIS 文件和模型,去勾選 power on,即可用外接供電。

結(jié)合設(shè)計師的電源電路設(shè)計,搭配 SIDesigner 內(nèi)嵌的高精度硅驗(yàn)證 TJSPICE 仿真引擎對高速電路進(jìn)行預(yù)仿真,通過波形結(jié)果觀察并測量 SSN 情況,進(jìn)行設(shè)計迭代優(yōu)化。

歡迎從官網(wǎng)申請試用我們的軟件,過程中的任何疑問可聯(lián)系support技術(shù)人員,期待與您的交流!

-

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1605瀏覽量

80622 -

仿真分析

+關(guān)注

關(guān)注

3文章

105瀏覽量

33659 -

同步開關(guān)噪聲

+關(guān)注

關(guān)注

0文章

3瀏覽量

8633

原文標(biāo)題:同步開關(guān)噪聲(SSN)簡介及仿真分析

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

開關(guān)電源產(chǎn)生的噪聲的原因與解決方案

開關(guān)電源特點(diǎn)及噪聲產(chǎn)生原因

開關(guān)電源產(chǎn)生的噪聲

紋波和噪聲產(chǎn)生的原因

開關(guān)電源產(chǎn)生噪聲的原因

開關(guān)電源產(chǎn)生紋波和噪聲的原因和測量方法

開關(guān)電源噪聲產(chǎn)生的原因

電源完整性之同步開關(guān)噪聲SSN

同步開關(guān)噪聲產(chǎn)生的原因和影響

同步開關(guān)噪聲產(chǎn)生的原因和影響

評論