在高性能應用中,例如通信、無線基礎設施、服務器、廣播視頻以及測試和測量裝置,當系統集成更多功能并需要提高性能水平時,硬件設計就變得日益復雜,為系統提供參考時序的板級時鐘樹也走向這種趨勢。在進行時鐘樹設計時, “ 一成不變 ” 的策略并不適用,優化時鐘樹以滿足性能和成本的要求取決于多種因素,包括系統架構、集成電路( IC )時序需求(頻率、信號格式等)和終端應用的抖動需求。

參考時序 - 何時使用晶體或時鐘

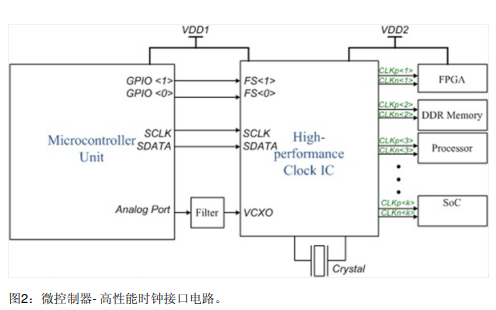

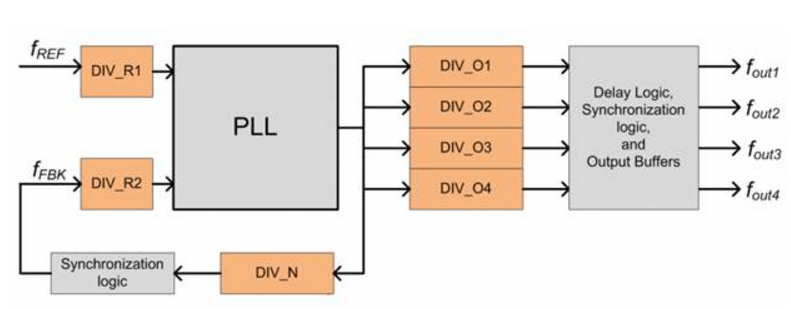

第一個設計原則是理清硬件設計的參考時鐘需求,并選擇用于系統中處理器、 FPGA、 ASIC、 PHY 、 DSP 和其他組件的參考時鐘類型。如果 IC 已集成振蕩器和片上鎖相環( PLL )用于片內時序,那么通常可以使用石英晶體。石英晶體具有成本效益,因其優異的相位噪聲特性而被廣泛使用,他們放在靠近IC的地方,以簡化電路板布局。然而,晶體的缺點之一是在整個溫度范圍內頻率有顯著變化,超出許多串化器/并化器( SerDes )應用中高精度ppm等級的穩定性需求。在許多要求高穩定性的高速SerDes 應用中,推薦使用晶體振蕩器( XO ),因其可以確保比無源晶體更可靠的穩定性。

當需要多個參考頻率時,通常使用時鐘發生器和時鐘緩沖器。在某些應用中,FPGA/ASIC有多個時鐘域用于數據通路、控制平面和存儲控制器接口,需要多個特定參考頻率。如果 IC 不提供晶體輸入接口,或者當 IC 需要與外部參考(同步源應用)同步時,又或者當所需高頻參考值很難由晶體生成時,時鐘發生器和緩沖器也是優先選擇。

自由運行對比同步時鐘樹

一旦硬件設計確定下來,并且為部分器件選擇了晶體,接下來的步驟就是為剩下的時鐘選擇時序架構:自由運行或同步。對于需要一個或多個獨立參考時鐘,且沒有任何特殊鎖相環或同步需求的應用來說,XO、時鐘發生器和時鐘緩沖器是理想選擇。處理器、存儲控制器、 SoC和外圍組件(例如, USB 和 PCI Express 轉換器)通常使用 XO、時鐘發生器和時鐘緩沖器組合,為自由運行和異步的應用提供參考時序。

如果應用需要一到兩個定時源,XO 是最好的選擇;而時鐘發生器和緩沖器更適合同時需要多個獨立時鐘的應用。時鐘發生器能夠合成多個不同頻率的時鐘,但與由時鐘緩沖器加上XO組成的時鐘樹相比,犧牲部分抖動性能。時鐘緩沖器可以與XO 參考聯合分配多個相同頻率的時鐘,并且為多輸出時鐘樹實現最低抖動。

-

時鐘設計

+關注

關注

0文章

27瀏覽量

10908 -

高性能時鐘

+關注

關注

0文章

1瀏覽量

1267 -

時鐘設計技巧

+關注

關注

0文章

1瀏覽量

1202

原文標題:高性能時鐘設計與應用

文章出處:【微信號:SiliconLabs,微信公眾號:Silicon Labs】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時鐘設備如何滿足復雜系統的高性能時序需求?

時鐘IC怎么滿足高性能時序需求?

時鐘的重要性,如何正確設計高性能轉換器

系統時鐘源的比較選擇及高性能PLL的發展趨勢

MAX3679A高性能四路輸出時鐘發生器(Maxim)

ADI公司宣布收購高性能時鐘技術MULTIGIG公司

采用MPC92433高性能時鐘合成源完成時鐘信號電路的設計

時鐘設備如何才能實現復雜系統的高性能時序需求

高性能時鐘芯片

設計高性能時鐘的幾點技巧

設計高性能時鐘的幾點技巧

評論