在這篇文章中,我將會介紹一個有趣的時鐘芯片反饋裝置。它可能意外發生,或作為嘗試恢復或測試模式,但通常應該如所解釋的那樣避免。此外,了解Ouroboros時鐘可能有助于在復雜的定時應用中解釋一些奇怪的行為。在深入了解“Ouroboros”時鐘之前,我們來看一下基本的時鐘切換術語和標準輸入時鐘切換配置。歡迎點擊“閱讀原文”觀看全文!

一些基本時鐘切換術語

時鐘芯片通常支持基于某些限定條件(例如LOS(Loss of Signal))或OOF(Out of Frequency)的條件,從一個輸入時鐘切換到另一個輸入時鐘。以下是最常用的術語:

自由模式

基于附加晶體或其他諧振器的輸出時鐘,或替代外部參考時鐘。輸出時鐘的頻率穩定性,漂移和抖動特性由芯片的晶振決定,與輸入時鐘無關。

保持模式

輸出時鐘基于所選輸入時鐘的歷史頻率數據,并且在輸入時鐘丟失并且沒有有效的備用可用時使用。通常歷史數據必須在一些最短時間內被收集,以被認為是有效的。頻率精度與收集的數據一樣好。

鎖定模式

輸出時鐘頻率和相位鎖定到所選擇的輸入時鐘,即正常操作。

標準輸入時鐘切換配置

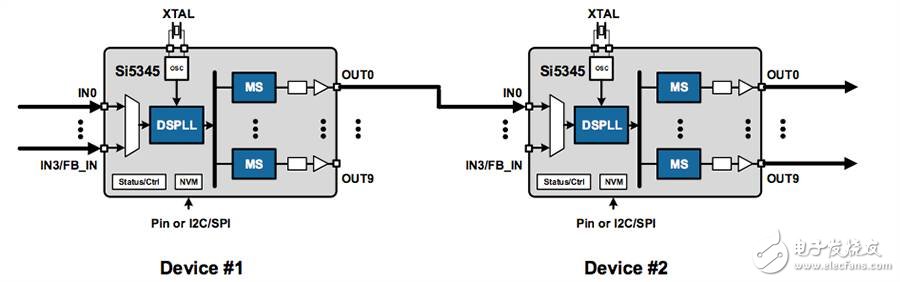

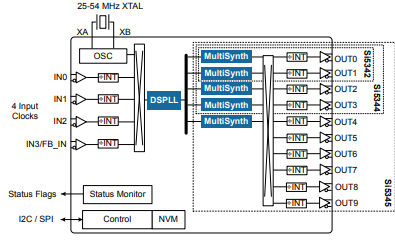

考慮下圖中的兩個抖動衰減器時鐘IC級聯的圖示。這可能用于額外的抖動衰減或優化頻率的計劃和分配。為了說明,這些設備被描繪為非常簡化的Si5345框圖。在該圖中,IN0和IN3提供給設備#1兩個輸入時鐘。

在典型的應用中,一個時鐘可以被認為是“主”時鐘,另一個被認為是“輔助”時鐘。主時鐘可能會從網絡數據恢復,而輔助時鐘則依賴本地振蕩器。如果主時鐘故障或被LOS或OOF取消資格,則時鐘芯片切換到輔助時鐘。這通常旨在使“下游”設備保持運行。如果主時鐘返回并且有效,那么根據所選擇的選項,時鐘IC可能會還原到它。

這里的推測是,只要這兩個時鐘中的任何一個存在,則在OUT0處產生有效的鎖定模式時鐘,從而向下游設備#2提供輸入時鐘。實際上,如果設備#1的兩個輸入時鐘都丟失,則設備可以進入保持模式,如上所述,甚至是自由模式,并且仍然產生臨時合理的輸出時鐘。

時鐘配置

在標準應用中,下行時鐘不反饋到上行時鐘輸入。相反,它們通常是上游獨立穩定或數據導出時鐘的縮放或抖動衰減版本。

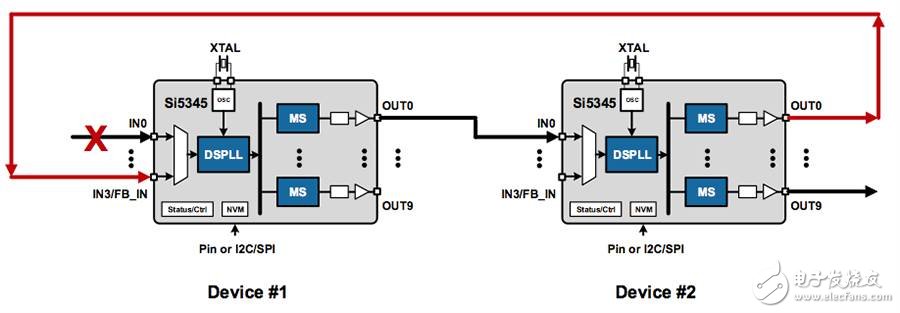

但是如果我們嘗試了如下圖2所示的配置怎么辦?在這種情況下,下游設備#2的輸出之一被反饋到上游設備#1。這可能是作為臨時的備份時鐘。

現在如下圖3所示,當我們失去主時鐘IN0時會發生什么?輔助或備用時鐘IN3至設備#1依賴于設備#2的輸出。請注意,這只是Device#1輸出的鎖定版本。我們通常不會看到這種與一個設備的連接,但偶爾提出涉及2個設備的應用程序。

這是Ouroboros時鐘配置。(是的,它聽起來就像生活大爆炸的臺詞。)Ouroborus時鐘配置的命名,是應為它的反饋類似于蛇追逐(或咬)它的尾巴的神話符號。根據維基百科,這個詞來自希臘語“ourá”和“bóros”,用于描述“吞噬或吞咽”。見圖4中的圖示。它是古代的循環無窮符號,適用于此應用。

Gedanken

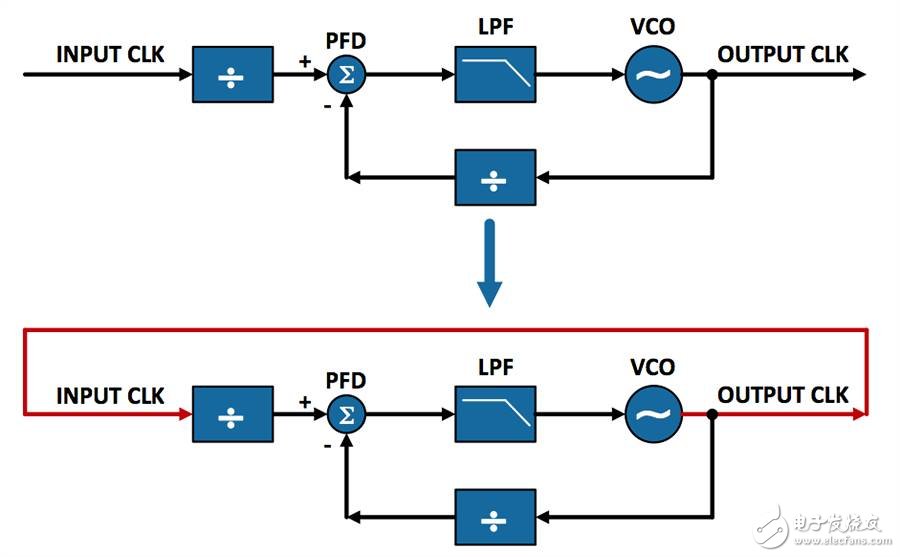

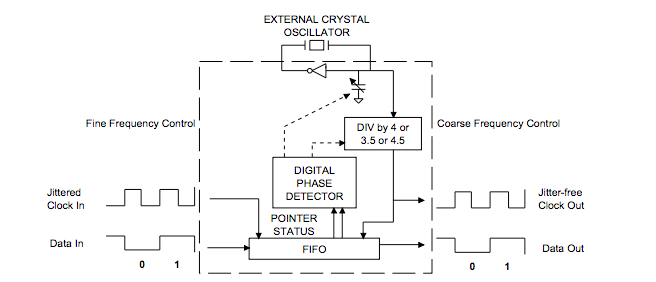

我們考慮一個簡單的gedanken實驗,由一個基本的PLL組成。然后假設它已經成功地被放置在Ouroboros配置中,如下面的圖5所示。

現在我們可以考慮可能的后果。如果一切都是理想的,并且沒有PFD(相位檢波器)錯誤輸出,則情況至少是稍微穩定的。然而,即使忽略環路噪聲,很可能在實際的PLL中,在PFD(+)和PFD( - )之間呈現的時鐘之間存在固定的相位偏移。在正常的PLL操作中,可以調節VCO,以便將輸出時鐘頻率和相位鎖定到獨立的輸入時鐘。在Ouroboros配置中,VCO無法減少相位誤差。

假設輸出時鐘以相位快速測量,在PFD(+)對PFD( - )下。然后,環路將通過將VCO調諧到更高的頻率來嘗試跟蹤。但相對相位差仍然存在。因此,循環將繼續嘗試校正所測量的相位誤差,直到VCO以其最高頻率“固定”為止。注意,為了推廣,可以根據相位差的極性將VCO調諧到更高或更低的頻率。最重要的是,PFD可以看到導致失控狀態的相位差。

實驗

那么真實情況下發生了什么呢?考慮具有以下屬性的項目計劃:

-

標稱帶寬:100.000 Hz

-

快速鎖定啟用關閉

-

從Holdover退出

-

OOF IN0和IN1:

-

聲明閾值100 ppm

-

斷言閾值98 ppm

現在采取這樣一個計劃,并將其應用到2個Si5345評估板,如上圖第二部分所示,除了使用IN1而不是IN3作為輔助或備用輸入時鐘。

將信號發生器應用到設備#1 IN0,并讓兩個電路板運行,直到HOLD_HIST_VALID為真。在IN0中刪除100 MHz輸入時鐘時會發生什么?

最初只有LOS [0]由設備#1報告。否則一切都很好。但是,來自Device#2的輸出時鐘頻率開始頻率上升(通常可能會上升或下降,但是在我的實驗中卻正在上升)。

最后,設備#2的輸出時鐘作為備用輸入時鐘,遠遠超出了設備#1的OOF標準。結算條件如下:

-

設備#1進入保持模式

-

設備#2在鎖定模式下運行。

請注意,一般來說,設備每個都在相反狀態的時候可能無理由的不穩定。我們的經驗是,大多數時候都有一些優先選擇的狀態,但是你會不時看到替代品,幾乎就好像結果中都有一個混亂的元素。

在這種情況下,Ouroboros配置沒有真正實現我們的任何東西,除了可能一點點。但是,請注意,輸出頻率在設備#1的OOF [1]斷言并且設備#2仍然依賴于設備1 HO時鐘的整個時間內上升。這對于這種不切實際的配置只是一個潛在的問題。但還有另一個可能更糟的效果。

Ouroboros振蕩

這種配置還可以產生正反饋系統,可以使振蕩,導致奇怪的行為。特別是,如果可以使其中一個設備進入退出HO,則可能會發生這種情況。例如,如果項目計劃OOF規格如下收緊,則可以觀察到這種現象。

-

OOF IN0和IN1:

-

聲明閾值000 ppm

-

斷言閾值9,375 ppm

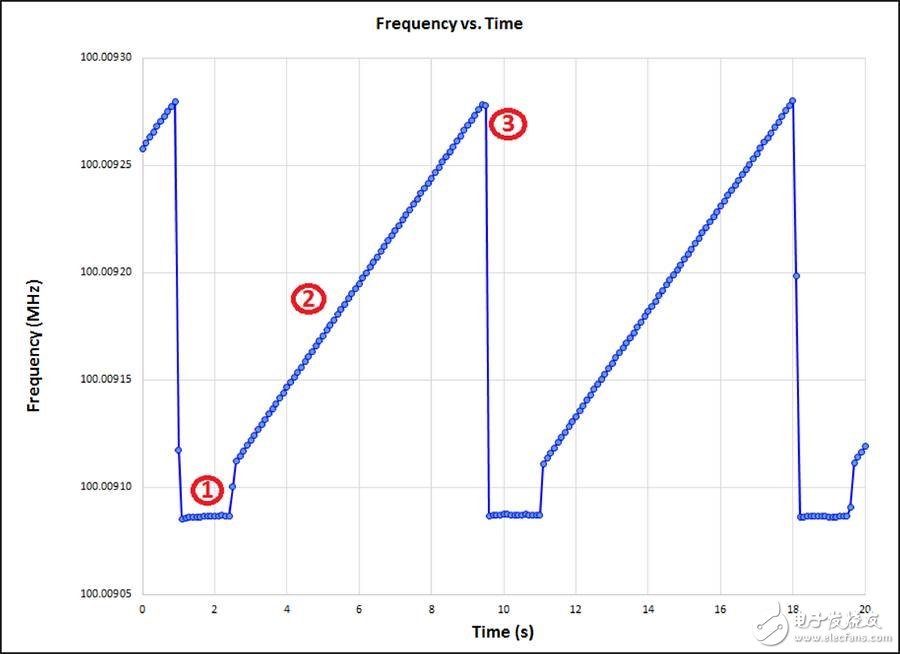

現在這兩個設備將相互交互,可能永遠不會解決。下面是Device#2輸出時鐘數據的頻率圖。您可以看到Device#2的輸出頻率在8或9秒的頻率范圍內慢慢振蕩。

上面有關于設備#1的狀態的三個功能,因為設備#2的輸出頻率有所不同:

1.器件#1處于保持或HO模式

2.裝置#1從HO斜坡退出

3.設備#1正在進入HO

在此期間,設備#2不會發出報警。這個狀態可以無限期地持續下去。我星期五下午開始試用這個實驗,星期一早上還在運行。設備甚至可以根據哪個在HO狀態交換角色!設備不斷進入和離開HO甚至比直接進入HO更糟糕。

結論

底線是,Ouroboros時鐘配置要么除了延遲進入HO沒有任何用處,或者可以觸發在輸出時鐘中產生重復漫游的振蕩。下游時鐘一般應保持下游。

-

抖動衰減時鐘應用

+關注

關注

0文章

1瀏覽量

769

原文標題:秒懂時鐘-抖動衰減時鐘設計與應用技巧 – Part 2

文章出處:【微信號:SiliconLabs,微信公眾號:Silicon Labs】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速ADC在低抖動采樣時鐘電路設計中的應用

Si5345和SI5344及SI5342系列抖動衰減時鐘倍增器的數據手冊免費下載

抖動衰減時鐘設計與應用技巧資料下載

時鐘電路設計之抖動衰減時鐘設計與應用技巧

時鐘電路設計之抖動衰減時鐘設計與應用技巧

評論