LVDS靜電放電防護(hù)方案

方案簡介

LVDS是一種低壓差分信號技術(shù),該技術(shù)通過一對差分信號線(或平衡電纜)以極低的電壓擺幅(約350mV)進(jìn)行數(shù)據(jù)的傳輸,采用LVDS接口,可以使得信號在差分線或平衡電纜上以幾百Mbps的速率傳輸,由于采用低壓和低電流驅(qū)動方式,實現(xiàn)了低噪聲、低串?dāng)_、低誤碼率和低功耗,LVDS在對信號完整性、低抖動及共模特性要求較高的系統(tǒng)中得到了越來越廣泛的應(yīng)用,常見于各電子設(shè)備的液晶顯示屏中。

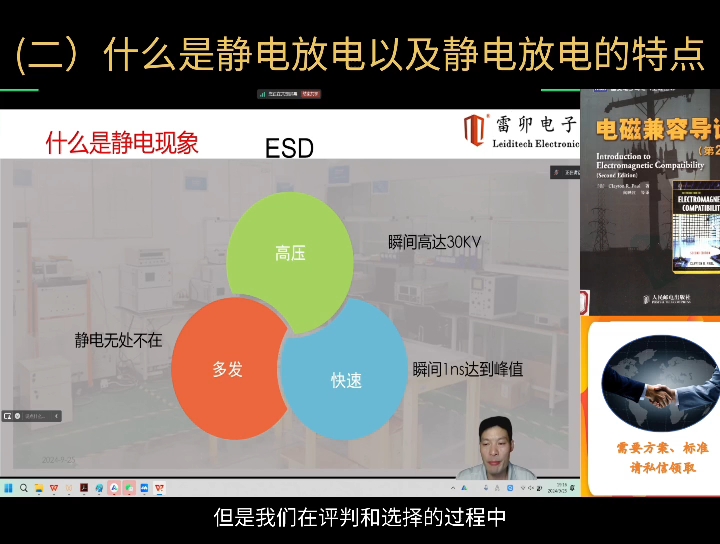

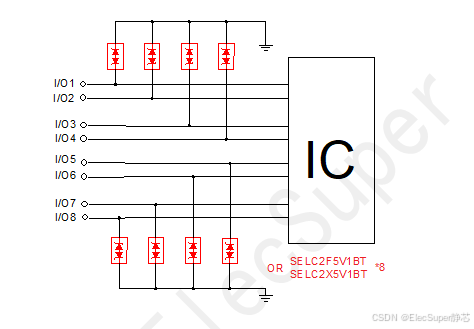

LVDS 接口擁有較高的數(shù)據(jù)傳輸速率,數(shù)據(jù)/圖像傳輸率為 650Mbps 至 1.3Gbps。由于接口試圖在保持高速的同時傳輸內(nèi)容,因此選擇線對線電容低的 ESD 保護(hù)器件對于確保信號完整性至關(guān)重要。普通的防護(hù)方案會對數(shù)據(jù)的傳輸造成一定影響。此方案高速差分信號部分采用集成低壓四通道保護(hù)、超低容值、低漏電、低殘壓的ESD靜電二極管防護(hù)器件,在不影響數(shù)據(jù)傳輸?shù)那疤嵯聺M足IEC61000-4-2 Level 4靜電放電防護(hù)需求,讓后端的電路得到有效防護(hù)。

LVDS工作原理

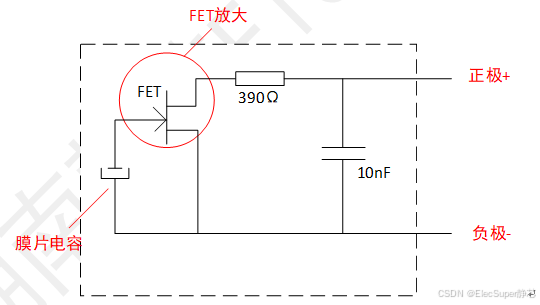

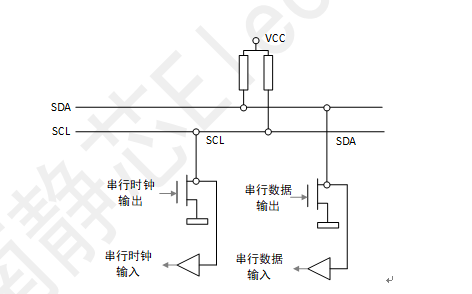

LVDS技術(shù)的基本工作原理是通過一個恒流源(通常約為3.5mA)驅(qū)動一對差分信號線。在接收端,由于接收器本身具有高直流輸入阻抗(幾乎不會消耗電流),因此幾乎全部的驅(qū)動電流都流經(jīng)100Ω的終端匹配電阻,并在接收器輸入端產(chǎn)生約350mV的電壓。當(dāng)驅(qū)動狀態(tài)反轉(zhuǎn)時,流經(jīng)電阻的電流方向改變,從而在接收端產(chǎn)生一個有效的“0”或“1”邏輯狀態(tài)。

編輯

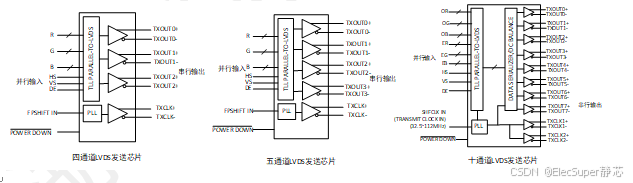

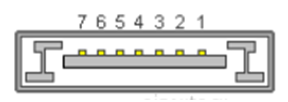

典型的LVDS發(fā)送芯片分為四通道、五通道和十通道幾種,輸入信號來自主控芯片,包含RGB數(shù)據(jù)信號、時鐘信號和控制信號三大類。發(fā)送芯片將以并行方式輸入的TTL電平RGB數(shù)據(jù)信號轉(zhuǎn)換成串行信號后,直接送往液晶面板側(cè)的接收芯片。LVDS發(fā)送芯片的輸出是低擺幅差分對信號,一般包含一個通道的時鐘信號和幾個通道的串行數(shù)據(jù)信號。由于LVDS發(fā)送芯片是以差分信號的形式進(jìn)行輸出,因此,輸出信號為兩條線,分別輸出正負(fù)信號。

應(yīng)用示例

編輯

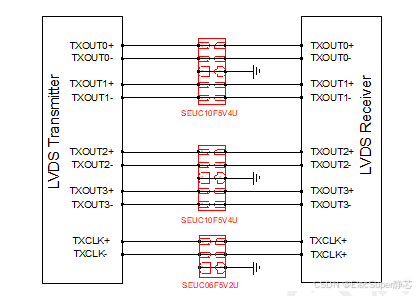

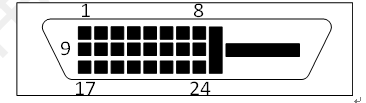

我們?yōu)長VDS接口提供了兩種電氣特性相似的ESD防護(hù)器件,專為保護(hù)差分線路而設(shè)計,其型號分別為SEUC10F5V4U和SEUC06F5V2U。器件的流通式封裝設(shè)計簡化了 PCB 布局,減少布線過程中的不連續(xù)性,促進(jìn)了信號完整性和系統(tǒng)穩(wěn)定性的提升。

SEUC10F5V4U為集成式十引腳ESD保護(hù)器件,結(jié)電容為0.6pF,鉗位電壓為12V,符合IEC 61000-4-2 (ESD) 規(guī)范,可在 ±17kV(空氣)和 ±12kV(接觸)下提供瞬變保護(hù),可同時保護(hù)LVDS接口的兩對數(shù)據(jù)傳輸高速信號差分線免受ESD靜電放電干擾。

SEUC06F5V2U為集成式六引腳ESD保護(hù)器件,結(jié)電容為0.6pF,鉗位電壓為12V,符合IEC 61000-4-2 (ESD) 規(guī)范,可在 ±17kV(空氣)和 ±12kV(接觸)下提供瞬變保護(hù),可保護(hù)LVDS接口的一對時鐘信號差分線免受ESD靜電放電干擾。

型號參數(shù)

| 規(guī)格型號 | 方向 | 工作電壓(V) | IPP(A) | 鉗位電壓(V) | 結(jié)電容(pF) | Package |

| SEUC10F5V4U | Uni. | 5 | 4.5 | 12 | 0.6 | DFN2510-10L |

| SEUC06F5V2U | Uni. | 5 | 4.5 | 12 | 0.6 | DFN1610-6L |

電氣特性表

At TA = 25℃ unless otherwise noted

| Parameters | Symbol | conditions | Min. | Typ. | Max. | Unit |

| Reverse stand-off voltage | VRWM | 5.0 | V | |||

| Reverse Breakdown Voltage | VBR | IT= 1mA | 6.0 | V | ||

| Reverse Leakage Current | IR | VRWM=5V | 1.0 | uA | ||

| Peak Pulse Current | IPP | TP=8/20us@25℃ | 4.5 | A | ||

| Clamping Voltage | VCL | IPP=1A; TP=8/20us | 9.0 | 11.0 | V | |

| Clamping Voltage | VCL | IPP=4.5A; TP=8/20us | 12.0 | 15.0 | V | |

| Junction capacitance | CJ |

I/O pins to ground; VR=0V; f = 1MHz |

0.6 | pF | ||

| Between I/O pins; | ||||||

| VR=0V; f = 1MHz | 0.3 |

表1 SEUC10F5V4U電氣特性表

| Parameter | Symbol | Conditions | Min. | Typ. | Max. | Units |

| Reverse Stand-off Voltage | VRWM | 5 | V | |||

| Reverse Breakdown Voltage | VBR | IT=1mA | 6 | 9.5 | V | |

| Reverse Leakage Current | IR | VRWM=5V | 1.0 | uA | ||

| Clamping Voltage | VC | IPP=1A; tp=8/20us | 8.5 | 10.0 | V | |

| Clamping Voltage | VC | IPP=4.5A; tp=8/20us | 12.0 | 15.0 | V | |

| Junction Capacitance | CJ | I/O to GND; VR=0V; f=1MHz | 0.6 | 0.8 | pF | |

| Between I/O; VR=0V; f=1MHz | 0.3 | 0.4 | pF |

表2 SEUC06F5V2U電氣特性表

總結(jié)與結(jié)論

LVDS接口不僅常用于消費電子類產(chǎn)品的顯示器中,還廣泛應(yīng)用于汽車中的視頻顯示系統(tǒng),所以保證其可靠性和穩(wěn)定性極為關(guān)鍵。ELECSUPER SEMI研發(fā)各種低電容低鉗位電壓的ESD保護(hù)器件,可按照客戶需求性能與封裝提供定制化開發(fā)服務(wù),為各種高速接口及通信線路提供值得信賴的保護(hù)器件。以上解決方案是保護(hù)LVDS接口的優(yōu)選之策,確保設(shè)備能夠高效、可靠地運行。

審核編輯 黃宇

-

靜電放電

+關(guān)注

關(guān)注

3文章

287瀏覽量

44656 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65812

發(fā)布評論請先 登錄

相關(guān)推薦

ESD靜電與靜電放電的區(qū)別與聯(lián)系

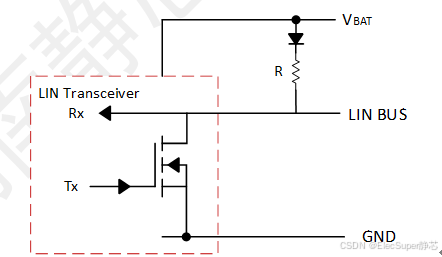

LIN接口靜電放電防護(hù)方案

Microphone靜電放電防護(hù)方案

【電磁兼容技術(shù)案例分享】某產(chǎn)品因LVDS導(dǎo)致靜電放電測試FAIL整改案例

分享幾種不同的靜電防護(hù)方案

LVDS靜電放電防護(hù)方案

LVDS靜電放電防護(hù)方案

評論