1、單片機的工作頻率

1.1單片機的設計應根據客戶的需求來選擇較低的工作頻率

首先介紹一下這樣做的優點:采用低的晶振和總線頻率使得我們可以選擇較小的單片機滿足時序的要求,這樣單片機的工作電流可以變得更低,最重要的是VDD到VSS的電流峰值會更小。

當然我們這里需要做一個妥協,因為客戶的要求可能是兼容的和平臺化的(目前汽車電子的發展趨勢就是平臺化),選擇較高的工作頻率可以兼容更多的平臺,也方便以后升級和擴展,因此要選擇一個較低的可以接受的工作頻率。

2、恰當的輸出驅動能力

在給定負載規范,上升和下降時間,選擇適當的輸出的上升時間,最大限度地降低輸出和內部驅動器的峰值電流是減小EMI的最重要的設計考慮因素之一。

驅動能力不匹配或不控制輸出電壓變化率,可能會導致阻抗不匹配,更快的開關邊沿,輸出信號的上沖和下沖或電源和地彈噪聲。

2.1設計單片機的輸出驅動器

首先確定模塊需求的負載,上升和下降的時間,輸出電流待續哦啊,根據以上的信息驅動能力,控制電壓擺率,只有這樣才能得到符合模塊需求又能滿足EMC要求。

驅動器能力比負載實際需要的充電速度高時,會產生的更高的邊沿速率,這樣會有兩個缺點:

1.信號的諧波成分增加了。

2.與負載電容和寄生內部bonding線,IC封裝,PCB電感一起,會造成信號的上沖和下沖。

選擇合適的的di/dt開關特性,可通過仔細選擇驅動能力的大小和控制電壓擺率來實現。最好的選擇是使用一個與負載無關的恒定的電壓擺率輸出緩沖器。同樣的預驅動器輸出的電壓擺率可以減少(即上升和下降時間可以增加),但是相應的傳播延遲將增加,我們需要控制總的開關時間)。

2.2使用單片機的可編程的輸出口的驅動能力,滿足模塊實際負載要求。

可編程的輸出口的驅動器的最簡單是的并聯的一對驅動器,他們的MOS的Rdson不能,能輸出的電流能力也不相同。我們在測試和實際使用的時候可以選擇不同的模式。實際上目前的單片機一般至少有兩種模式可選擇,有些甚至可以有三種(強,中等,弱)。

2.3當時序約束有足夠的余量的時候,通過降低輸出能力來減緩內部時鐘驅動的邊沿。

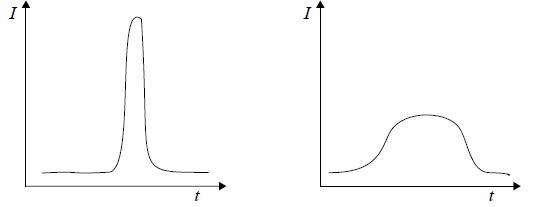

減少同步開關的峰值電流,和di/dt,一個重要的考慮因素就是降低內部時鐘驅動的能力(其實就是放大倍數,穿通電流與之相關型很大)。降低時鐘邊沿的電流,將顯著改善EMI。當然這樣做的缺點就是,由于時鐘和負載的開通時間的變長使得單片機的平均電流可能增加。快速邊沿和相對較高的峰值電流,時間更長邊沿較慢的電流脈沖這兩者需要做一個妥協。

2.4晶振的內部驅動(反向器)最好不要超過實際的需求。

這個問題,實際上前面也談過了,當增益過大的時候會帶來更大的干擾。

3、設計最小穿通電流的驅動器

3.1 時鐘,總線和輸出驅動器應盡可能使得傳統電流最小

穿通電流【重疊電流,短路電流】,是從單片機在切換過程中,PMOS和NMOS同時導通時候,電源到地線的電流,穿通電流直接影響了EMI和功耗。

這個內容實際上是在單片機內部的,時鐘,總線和輸出驅動器,消除或減少穿通電流的方法是盡量先關閉一個FET,然后再開通一個FET。當電流較大時,需要額外的預驅動電路或電壓擺率。

-

單片機

+關注

關注

6037文章

44559瀏覽量

635512 -

emc

+關注

關注

170文章

3923瀏覽量

183237

原文標題:單片機EMC設計時注意這三點太重要了。。。

文章出處:【微信號:Mouser-Community,微信公眾號:貿澤電子設計圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

技巧:對單片機EMC設計的幾點建議

單片機的EMC 測試及EMC 故障排除

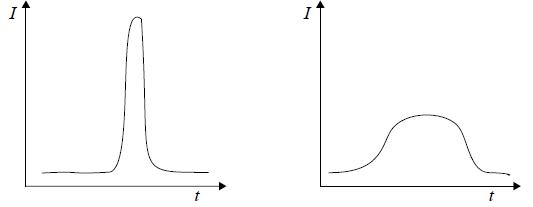

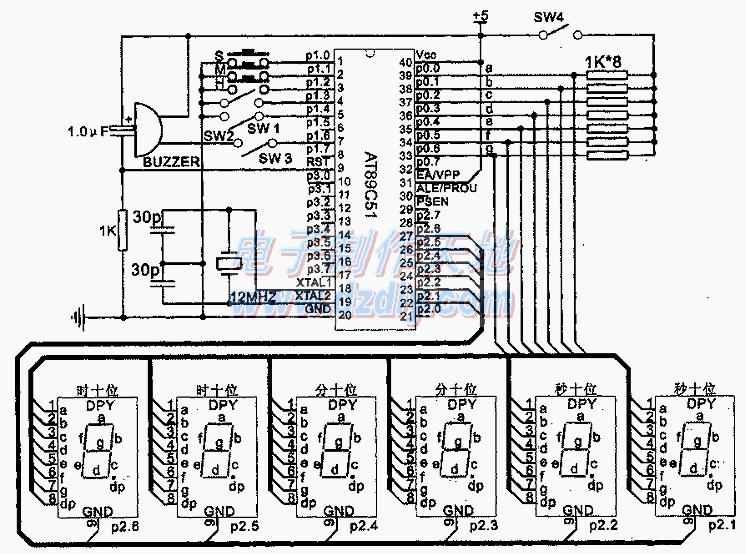

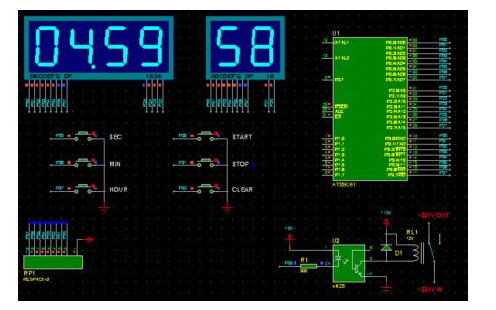

基于單片機的上網計時系統的設計

McuPlayer的EMC單片機學習筆記

三點式振蕩器,三點式振蕩器電路原理圖

單片機EMC設計的幾點建議

51單片機計時器

單片機實現EMC設計時的三點細節建議

單片機實現EMC設計時的三點細節建議

評論