為什么需要復(fù)位電路

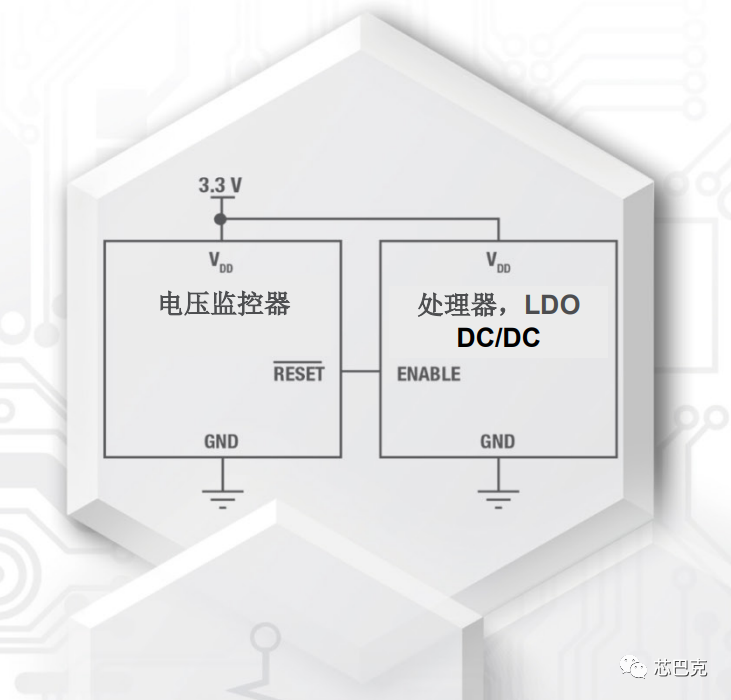

數(shù)字電路只有0和1兩種狀態(tài),在電路剛上電或電路工作不穩(wěn)定時(shí),數(shù)字電路的輸出是不穩(wěn)定的,這時(shí)需要給電路一個(gè)激勵(lì),使電路進(jìn)入一個(gè)預(yù)先設(shè)定好的狀態(tài)。復(fù)位電路的作用就是監(jiān)控電路,并在需要的時(shí)候發(fā)出這樣的激勵(lì)。

常見的復(fù)位電路設(shè)計(jì)中的問題可分為以下幾類:未提供復(fù)位信號(hào)、復(fù)位時(shí)序不正確、復(fù)位信號(hào)驅(qū)動(dòng)能力不足。

未提供復(fù)位信號(hào)

一般復(fù)雜高速電路會(huì)提供總復(fù)位電路,但有時(shí)電路中某些模塊的復(fù)位并不是由系統(tǒng)的總復(fù)位提供。這種情況之下,需要在系統(tǒng)完成總復(fù)位后,再使能特定的復(fù)位信號(hào),以實(shí)現(xiàn)特定模塊的復(fù)位。

例如,某單板選用POWERPC電路模塊作為CPU子系統(tǒng),在系統(tǒng)復(fù)位完成后,通過軟件測(cè)試CPU所掛的DDR2 SDRAM DIMM條,發(fā)現(xiàn)無法完成讀寫操作。

tips:DIMM條,SIMM條名詞解釋:Dual-Inline-Memory-Modules,即雙列直插式存儲(chǔ)模塊。SIMM(single in-line memory module,單邊接觸內(nèi)存模組),就是主板上常見的內(nèi)存條。

經(jīng)分析系統(tǒng)原理圖發(fā)現(xiàn) DDR2 SDRAM DIMM條的復(fù)位信號(hào)與GPIO29相連,而代碼中并不包括對(duì)GPIO29的配置。而與SRAM、SDRAM、DDR SDRAM、DDR2 SDRAM不同,DIMM上有多個(gè)DDR存儲(chǔ)器,需要時(shí)鐘驅(qū)動(dòng)器,而此時(shí)鐘驅(qū)動(dòng)器需要使能信號(hào),這個(gè)使能信號(hào)由DIMM復(fù)位信號(hào)充當(dāng),故當(dāng)將gpio29的配置功能加入后,CPU即可正常讀寫存儲(chǔ)器。

在復(fù)雜的高速電路設(shè)計(jì)中,尤其是涉及主控板和業(yè)務(wù)板的設(shè)計(jì)中,通常要求帶電插拔業(yè)務(wù)板,這個(gè)事件將由一個(gè)中斷信號(hào)通知主控板,主板查詢到業(yè)務(wù)板插入后,需要發(fā)出一個(gè)復(fù)位信號(hào)單獨(dú)對(duì)此業(yè)務(wù)板進(jìn)行復(fù)位,而不影響其他業(yè)務(wù)板和主控板的工作,故此復(fù)位信號(hào)不能用系統(tǒng)復(fù)位信號(hào),而應(yīng)該由cpu控制器的GPIO驅(qū)動(dòng)輸出。所以除了系統(tǒng)復(fù)位信號(hào),還應(yīng)提供各功能模塊的專用復(fù)位信號(hào)。

復(fù)位時(shí)序不正確

復(fù)位時(shí)序問題產(chǎn)生的原因有兩個(gè):發(fā)送方和接收方

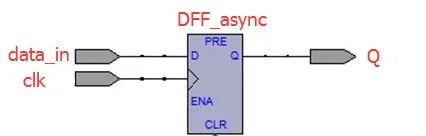

發(fā)送方的問題主要出在沒有在正確的時(shí)間輸出正確的波形。設(shè)計(jì)可編程邏輯的設(shè)計(jì),器件選型完成后,應(yīng)該制定單板總體復(fù)位框圖,并對(duì)框圖進(jìn)行仔細(xì)審核。

接收方的問題考慮復(fù)位信號(hào)到達(dá)接收端有沒有出現(xiàn)波形失真。主要衡量發(fā)送方和接收方的波形差別,由于波形的差別,可能導(dǎo)致復(fù)位時(shí)序出錯(cuò)。考慮兩個(gè)環(huán)節(jié):一是在傳輸路徑上有沒有經(jīng)過驅(qū)動(dòng)或轉(zhuǎn)換器件,這些器件帶來的延時(shí)是多少;二是傳輸路徑上的容性是否太大以至于改變了信號(hào)邊沿的斜率。

復(fù)位信號(hào)驅(qū)動(dòng)能力不足

當(dāng)復(fù)位信號(hào)在PCB上走線過長(zhǎng),或接收端容性過大,這些因素都可能導(dǎo)致復(fù)位信號(hào)驅(qū)動(dòng)能力不足,具體表現(xiàn)為信號(hào)邊沿過緩,不能滿足某些芯片對(duì)復(fù)位信號(hào)邊沿速率的要求。

-

復(fù)位電路

+關(guān)注

關(guān)注

13文章

324瀏覽量

44945

原文標(biāo)題:高速電路中的復(fù)位設(shè)計(jì)

文章出處:【微信號(hào):murata-eetrend,微信公眾號(hào):murata-eetrend】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

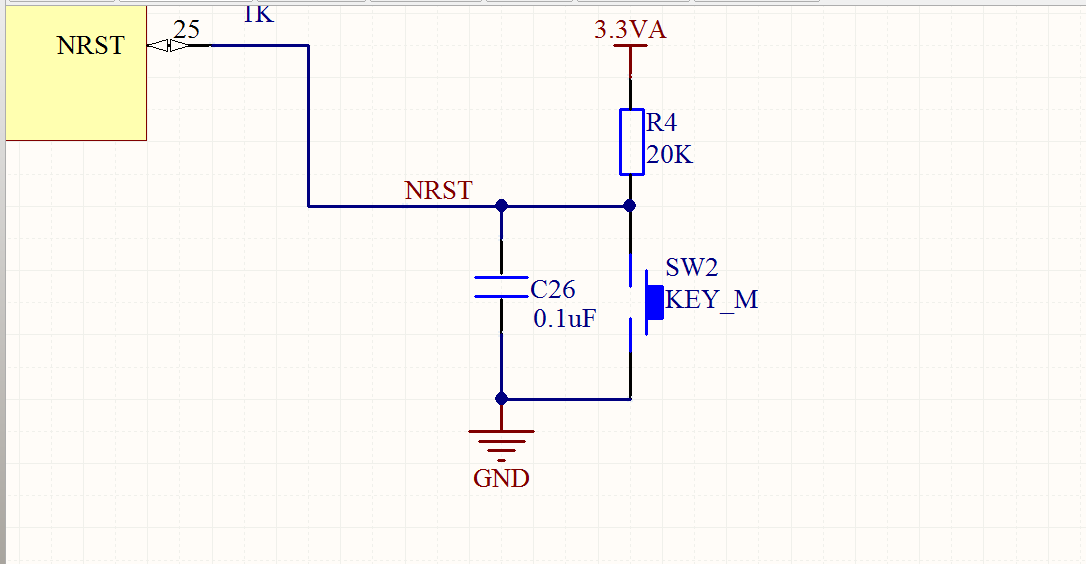

MCU的復(fù)位電路設(shè)計(jì)

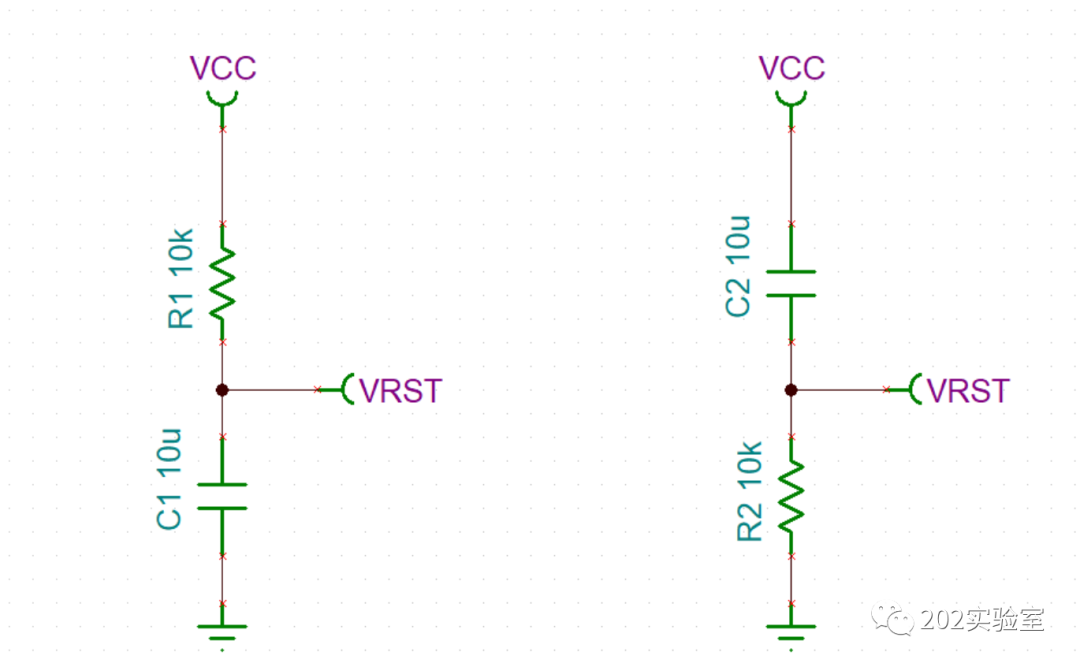

rc復(fù)位電路的電阻作用

51單片機(jī)復(fù)位電路設(shè)計(jì)

復(fù)位電路設(shè)計(jì)選型指南

ARM單片機(jī)的復(fù)位電路設(shè)計(jì)

51單片機(jī)幾種實(shí)用的復(fù)位電路設(shè)計(jì)

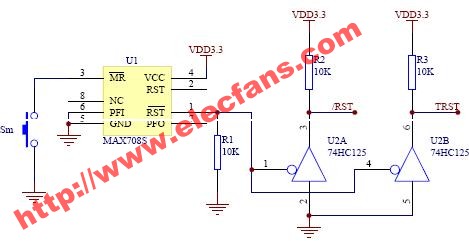

高可靠性復(fù)位電路設(shè)計(jì)(電路設(shè)計(jì)與分析)

FPGA內(nèi)部自復(fù)位電路設(shè)計(jì)方案

復(fù)位電路設(shè)計(jì)分析

深度剖析復(fù)位電路

嵌入式系統(tǒng)復(fù)位電路介紹

STM32復(fù)位電路用復(fù)位芯片和阻容復(fù)位電路區(qū)別

復(fù)位電路靜電整改案例分享(一)——交換機(jī)復(fù)位電路

評(píng)論