芯片晶粒在未來搭載愈來愈多晶體管可望成為趨勢,讓芯片運算能力達到人腦水平也可望有朝一日達成,對于這類新技術的發展,在芯片上以及在多層堆疊芯片之間打造先進3D結構成為一大主要驅動力,在2017年IEEE IEDM大會上也可見相關技術進展的發表及討論,可以預期的是,數據中心以芯片為基礎的電子存儲器及嵌入式應用如計算機與工業存儲器,朝3D技術發展將成為趨勢。

根據富比士(Forbes)報導,除了存儲器3D技術趨勢外,每顆芯片配置多元存儲器以及多層堆疊芯片的設計也將主導許多應用,此外,各類電阻式存儲器及MRAM技術也將有助儲存級存儲器、低功耗與長效物聯網(IoT),以及其它不斷成長中應用的發展。

臺積電在本屆IEEE IEDM大會上表示,至2020年業界將可見每晶粒500億個晶體管的芯片問世,但其復雜度仍比相當于有著約1兆晶體管的人類大腦為低,藉由NVIDIA及其它業者在開發的新興3D x 3D超級芯片,將可內含2,000億個晶體管,到那時才會比較接近大腦的復雜度。在芯片上及多層堆疊芯片間打造先進3D結構,成為達成新技術的主要驅力。

新興非揮發性存儲器有助進行神經運算以進行裝置中的機器學習(ML),可進一步強化當前神經網絡的能力。可變電阻式隨機存取存儲器(ReRAM)則是受神經存儲器芯片青睞采用的技術,因ReRAM可作為突觸元件進行操作。

本屆IEEE IEDM大會可見許多報告提出改善這些存儲器特性的方式,如韓國SK海力士(SK Hynix)發布一份XPoint技術的23納米ReRAM,這款ReRAM內含砷以創造閥值切換行為;GlobalFoundries發布的報告,則討論一款7納米CMOS技術如何用于高性能運算及行動裝置。

日本中央大學教授Ken Takeuchi則談到如何在NAND Flash控制器中提供額外的處理能力,該控制器可辨識特定應用的重要數據,以及將此數據儲存于可靠的存儲器單元中。在此方法中雖然電路本身的精確度降低,深度學習(DL)的推論結果這類應用級準確度則不會下降。

這也是近似運算(approximate computing)能夠被運用于提供在存儲器及儲存裝置內部所采用較小型及功耗更佳處理器更有用功能的原因。未來的數據中心將采用由中央處理器(CPU)、DRAM、儲存控制器、儲存級存儲器(SCMs)以及Flash存儲器所組成的非聚合式混合儲存技術。

針對MRAM技術,高通旗下高通技術(Qualcomm Technologies)公司出席本屆IEEE IEDM大會的代表指出,MRAM準備成為統一的存儲器子系統,能夠改造物聯網及穿戴式裝置這類新興極低功耗系統的架構,且MRAM也可改變以運算為中心的架構。例如面垂直(perpendicular) STT-MTJ MRAM具備快速讀寫特性,也有助當前的SRAM及DRAM可直接與處理器一同配置。

這將有助以單一MRAM存儲器取代應用于許多物聯網應用的SRAM及Flash架構,因而減少存儲器之間的信息流以及節省功耗支出,這對搭載電池的應用來說特別重要,加上MRAM的位元單元(Bitcell)大小約只有SRAM位元單元的25~30%,因此采用MRAM也可節省晶粒空間。

由于電路簡化,讓MRAM應可被視為是具成本競爭力的存儲器選項,特別是對嵌入式應用而言更是如此,只不過MRAM在成本上仍無法與高密度DRAM相較,因此應用驅動的客制化獨立MRAM或較具競爭力,因在價格上比eMRAM為低。

-

芯片

+關注

關注

456文章

51016瀏覽量

425321 -

3D

+關注

關注

9文章

2899瀏覽量

107694 -

MRAM

+關注

關注

1文章

236瀏覽量

31744

原文標題:【供應鏈】2017年IEEE IEDM大會存儲器圍繞3D、MRAM及新芯片探討

文章出處:【微信號:gh_44592200c847,微信公眾號:gh_44592200c847】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

3D深度感測的原理和使用二極管激光來實現深度感測的優勢

DMD芯片在3D打印中的創新應用

3D集成電路的結構和優勢

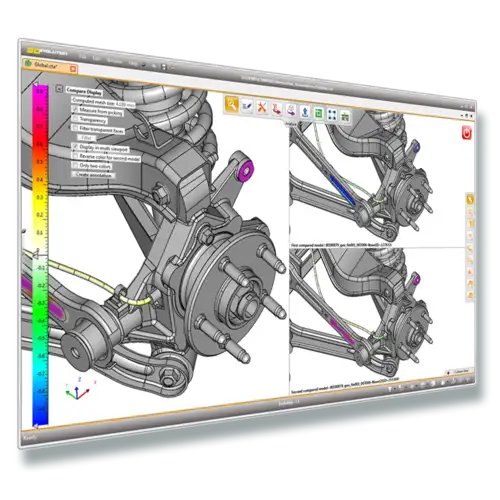

安寶特產品 安寶特3D Analyzer:智能的3D CAD高級分析工具

3D封裝熱設計:挑戰與機遇并存

裸眼3D筆記本電腦——先進的光場裸眼3D技術

西門子推出Calibre 3DThermal軟件,持續布局3D IC熱分析

英倫科技裸眼3D平板有哪些方面的優勢?

奧比中光攜多款3D相機深度參與國內3D視覺最高規格會議

新質生產力探索| AICG浪潮下的3D打印與3D掃描技術

基于深度學習的方法在處理3D點云進行缺陷分類應用

對3D、MRAM及新芯片的深度分析和探討

對3D、MRAM及新芯片的深度分析和探討

評論