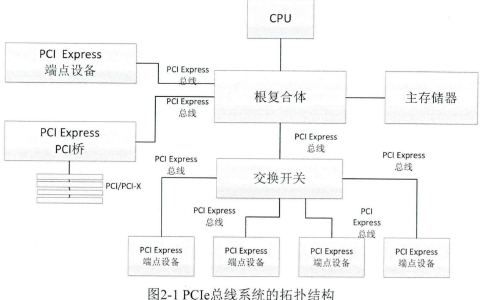

隨著通信技術(shù)的不斷發(fā)展,對(duì)數(shù)據(jù)傳輸系統(tǒng)的速度與數(shù)據(jù)傳送質(zhì)量的要求也在不斷提高。由Intel在2001年提出的第三代I/O總線技術(shù)——PCI Express總線技術(shù),采用高速差分串行的方式進(jìn)行數(shù)據(jù)傳輸,具有高帶寬、高可靠性、高拓展性等優(yōu)點(diǎn),很好地彌補(bǔ)了PCI、PCI-X總線的不足。

本文基于PCIe 2.0協(xié)議,利用Altera Transceiver PHY IP、Synopsys PCIe Core IP和AXI總線,提出了一種DMA控制器,并搭建了一個(gè)在FPGA端和PC之間的高速數(shù)據(jù)傳輸系統(tǒng)。實(shí)現(xiàn)了寄存器讀寫操作(單字讀寫)和DMA讀寫操作,并利用Synopsys VIP環(huán)境下進(jìn)行的系統(tǒng)仿真和上位機(jī)軟件進(jìn)行觀察并驗(yàn)證了數(shù)據(jù)讀寫的正確性。

1 設(shè)計(jì)方案1.1 基礎(chǔ)模塊

1.1.1 Altera Stratix V GX系列FPGA與PCIe PHY IP

本設(shè)計(jì)使用Stratix V GX系列下的5SGXEA7K2F40C2N FPGA芯片,該芯片內(nèi)部集成了PCIe PHY IP硬核模塊。PCIe PHY IP硬核包括三個(gè)部分,如圖1,PHY IP Core for PCI Express(PIPE)集成了PCIe總線的物理層。Transceiver Reconfiguration Controller IP Core可以動(dòng)態(tài)重新配置模擬參數(shù)。Transceiver PHY Reset Controller IP Core作為收發(fā)器的復(fù)位模塊,確保了PCIe鏈路的初始化。

1.1.2 Synopsys IP與VIP

VIP顧名思義就是驗(yàn)證IP(Verification IP),它為一些標(biāo)準(zhǔn)的接口提供標(biāo)準(zhǔn)的總線行為模型。Synopsys公司提供了PCIe總線的Controller IP,實(shí)現(xiàn)了PCIe總線數(shù)據(jù)鏈路層和事務(wù)層的功能,并內(nèi)置了DMA,同時(shí)也提供了針對(duì)PCIe總線的VIP,為PCIe總線提供了標(biāo)準(zhǔn)的總線行為模型,模擬了上位機(jī)的功能[8]。

1.1.3 AXI總線

AXI(Advanced eXtensible Interface)總線是一種高性能、高帶寬、低延遲的總線協(xié)議,有一個(gè)顯著的特點(diǎn),地址/控制和數(shù)據(jù)通道是分開的,共有5個(gè)單向通道,分別為read address channel,write address channel,read data channel,write data channel,write response channel[9],減少了延時(shí),提高了DMA的效率。

1.2 總體方案設(shè)計(jì)

本設(shè)計(jì)采用的整體架構(gòu)如圖2所示,為Altera PHY IP+Synopsys PCIe Core IP+AXI總線+Application。

為了利用Synopsys 的PCIe VIP環(huán)境,采用了Synopsys PCIe Core IP。在PCIe事務(wù)層和應(yīng)用側(cè)之間采用了AXI總線接口,可以在以后的設(shè)計(jì)中進(jìn)行方便的拓展和替換。應(yīng)用側(cè)設(shè)計(jì)實(shí)現(xiàn)了PCIe DMA控制器的功能,并集成了兩塊RAM,一塊大小為128 DW,用來存儲(chǔ)寄存器讀寫的數(shù)據(jù);另一塊大小為512 DW,用來存儲(chǔ)DMA讀寫的數(shù)據(jù)。

2 DMA控制器的設(shè)計(jì)與實(shí)現(xiàn)2.1 應(yīng)用端DMA操作流程

應(yīng)用端發(fā)起的DMA操作流程如圖3所示,最終DMA讀操作實(shí)現(xiàn)的結(jié)果為將主機(jī)側(cè)的數(shù)據(jù)以DMA的方式寫入到應(yīng)用端的內(nèi)存中。DMA寫操作實(shí)現(xiàn)的結(jié)果為將應(yīng)用端的數(shù)據(jù)以DMA的方式寫入到主機(jī)側(cè)的內(nèi)存中。圖3為應(yīng)用端發(fā)起的DMA操作具體的流程。

(1)主機(jī)側(cè)通過寄存器寫的方式,將DMA讀寫標(biāo)志、DMA長(zhǎng)度、DMA源和目的內(nèi)存地址寫入到應(yīng)用端的寄存器中;

(2)應(yīng)用端中的Slave模塊將這些命令發(fā)送給Master模塊;

(3)Master模塊按照Synopsys PCIe Core IP自定義的Dbi總線的方式,再將這些命令傳送給PCIe Core IP內(nèi)部的寄存器;

(4)PCIe Core IP接收DMA讀寫指令,并持續(xù)操作Master接口以實(shí)現(xiàn)后續(xù)操作;

(5)當(dāng)為DMA讀時(shí),PCIe Core IP的內(nèi)置DMA從主機(jī)側(cè)的“源內(nèi)存地址”中讀取到目標(biāo)數(shù)據(jù);當(dāng)為DMA寫時(shí),PCIe Core IP的Master接口通過AXI總線以讀的方式從“源內(nèi)存地址”讀取到目標(biāo)數(shù)據(jù);

(6)當(dāng)為DMA讀時(shí),PCIe Core IP的Master獲得DMA讀取到的目標(biāo)數(shù)據(jù),并通過AXI總線,以寫的方式寫入到應(yīng)用端的“目的內(nèi)存地址”中;當(dāng)為DMA寫時(shí),Master獲得目標(biāo)數(shù)據(jù)后,內(nèi)置DMA將數(shù)據(jù)發(fā)送到主機(jī)側(cè)的“目的內(nèi)存地址”中;

(7)當(dāng)DMA操作完成,PCIe Core IP會(huì)通知應(yīng)用端的中斷模塊;

(8)應(yīng)用端的中斷模塊會(huì)向主機(jī)側(cè)提交中斷。

2.2 應(yīng)用端DMA控制狀態(tài)機(jī)

應(yīng)用端只需將主機(jī)側(cè)寫入的DMA讀寫標(biāo)志、DMA長(zhǎng)度、DMA源和目的內(nèi)存地址以及DMA啟動(dòng)信號(hào)寫入到PCIe Core IP中的內(nèi)部寄存器,并等待DMA操作的完成,給出中斷信號(hào)。

下面為應(yīng)用端詳細(xì)的DMA控制狀態(tài)機(jī),如圖4所示,狀態(tài)機(jī)把DMA讀操作和DMA寫操作整合到了一起,減少了代碼量。

(1)IDLEPHASE:空閑狀態(tài)。當(dāng)啟動(dòng)信號(hào)start_flag有效時(shí),跳轉(zhuǎn)ENGINE_ENABLE狀態(tài);

(2)ENGINE_ENABLE:判斷DMA讀寫類型信號(hào)wr_rdn_flg,當(dāng)wr_rdn_flg為0,即為DMA讀(PC到FPGA)時(shí),使能DMA讀引擎;當(dāng)wr_rdn_flg為1,即為DMA寫(FPGA到PC)時(shí),使能DMA寫引擎;

(3)DMA_TRANS_SIZE:設(shè)置DMA數(shù)據(jù)傳輸長(zhǎng)度,最多一次傳輸512 DW,最少一次傳輸1 DW;

(4)DMA_SAR:設(shè)置DMA操作源地址(當(dāng)為DMA讀時(shí),源地址為主機(jī)端地址;當(dāng)為DMA寫時(shí),源地址為應(yīng)用端地址);

(5)DMA_DAR:設(shè)置DMA操作目的地址(當(dāng)為DMA讀時(shí),目的地址為應(yīng)用端地址;當(dāng)為DMA寫時(shí),目的地址為主機(jī)端地址);

(6)DMA_DOORBELL:使能DMA操作門鈴信號(hào)dma_strt,啟動(dòng)DMA操作;

(7)DMA_WAIT_INT:等待DMA操作完成;

(8)DMA_INT_STATUS:讀取DMA操作中斷寄存器狀態(tài),當(dāng)DMA操作完成信號(hào)dma_done有效時(shí),產(chǎn)生完成中斷,并跳轉(zhuǎn)DMA_CLEAR_INT狀態(tài);

(9)DMA_CLEAR_INT:清除中斷,回到IDLEPHASE狀態(tài),準(zhǔn)備下一次DMA傳輸。

3 DMA控制器功能驗(yàn)證3.1 仿真驗(yàn)證

在完成代碼編寫之后,在VIP環(huán)境下搭建仿真平臺(tái),使用Synopsys公司的仿真驗(yàn)證工具VCS進(jìn)行功能測(cè)試,主要測(cè)試驗(yàn)證模塊能否正確對(duì)寄存器讀寫和DMA讀寫產(chǎn)生正確的反應(yīng)。

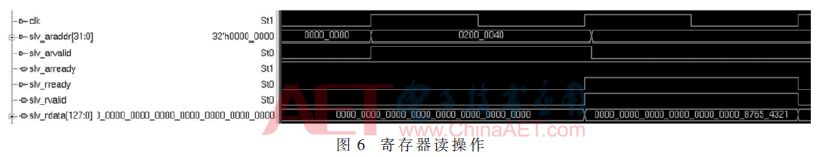

從圖5、圖6中可以看到,寫地址偏移為0x40,寫數(shù)據(jù)為32’h87654321;讀地址偏移為0x40,讀數(shù)據(jù)為32’h87654321,由此可判斷寄存器讀寫正確。

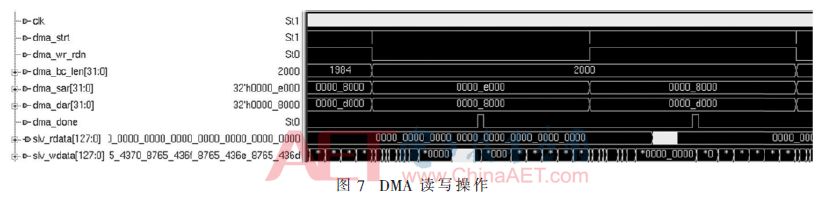

如圖7所示,由dma_strt和dma_done信號(hào)可以看出為2次DMA傳輸,由dma_wr_rdn可看出第一次為DMA讀操作(RC端到APP側(cè)),第二次為DMA寫操作(APP側(cè)到RC端)由dma_bc_len可看出當(dāng)前DMA操作長(zhǎng)度為2 000 Byte,即500 DW,slv_rdata和slv_wdata信號(hào)較為密集的部分分別為2次DMA操作的數(shù)據(jù),對(duì)比這兩次數(shù)據(jù),得知DMA操作正確。

為了更加方便地比較結(jié)果,采取自動(dòng)對(duì)比文件的方法,即把寄存器或DMA寫的數(shù)據(jù)存放到一個(gè)文件中,再把寄存器或DMA讀回的數(shù)據(jù)存放到另一個(gè)文件中,通過對(duì)比兩個(gè)文件,判斷寄存器和DMA傳輸是正確的。

3.2 FPGA測(cè)試驗(yàn)證

在仿真驗(yàn)證完成之后,進(jìn)行FPGA測(cè)試驗(yàn)證,將硬件部分燒錄到板卡的FPGA芯片后,通過板卡的PCIe金手指插入到PC機(jī)的主板上,PC機(jī)重啟后檢測(cè)到PCIe硬件的插入,即可安裝對(duì)應(yīng)的PCIe驅(qū)動(dòng)軟件,利用上位機(jī)進(jìn)行測(cè)試。

上位機(jī)軟件界面如圖8所示,包括寄存器讀寫(Target操作)和DMA讀寫(Master操作)測(cè)試模塊。

選擇“Target”操作的“dual”模式,寄存器長(zhǎng)度設(shè)置為118,因?yàn)榍?0個(gè)寄存器與DMA操作相關(guān),可能會(huì)觸發(fā)DMA操作,所以在軟件中選擇跳過。點(diǎn)擊“啟動(dòng)測(cè)試”,數(shù)據(jù)將會(huì)被先從主機(jī)側(cè)寫到FPGA,再從FPGA讀回到主機(jī)側(cè),比較兩次寄存器操作的數(shù)據(jù),即可判斷寄存器操作的正確性。

如圖9所示,選擇“Master”操作的“dual”模式,點(diǎn)擊“memory”,即在PC側(cè)開辟一塊內(nèi)存存放數(shù)據(jù),然后點(diǎn)擊“啟動(dòng)測(cè)試”,數(shù)據(jù)先從PC寫到FPGA的RAM中,接著再從FPGA回到PC,比較存放到PC內(nèi)存的數(shù)據(jù)和從FPGA寫回到PC的數(shù)據(jù),即可判斷DMA讀寫操作的正確性。

根據(jù)DMA傳輸固定大小的數(shù)據(jù)的時(shí)間,可以計(jì)算出DMA讀寫速率,經(jīng)過多次測(cè)試,DMA讀寫速率分別為1 547 MB/s和1 607 MB/s。本設(shè)計(jì)采用的是PCIe Gen2、×4通道,理論最大傳輸速率為2 000 MB/s。分析代碼得出可能由于應(yīng)用端向PCIe Core IP寫入和讀取數(shù)據(jù)過程占用了一定的時(shí)間,另外驅(qū)動(dòng)程序向DMA寄存器寫入或讀取參數(shù)也占用了一些時(shí)間,都會(huì)影響速率。

4 結(jié)語本文實(shí)現(xiàn)的基于FPGA的PCIe總線接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基礎(chǔ)上實(shí)現(xiàn)的,利用Synopsys VIP驗(yàn)證環(huán)境進(jìn)行了功能仿真驗(yàn)證,并通過FPGA進(jìn)行了系統(tǒng)實(shí)測(cè),達(dá)到了較高的傳輸速率,在Gen2、×4模式下,DMA讀寫操作的帶寬分別為 1 547 MB/s和1 607 MB/s,達(dá)到了預(yù)期的設(shè)計(jì)目標(biāo)。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603419 -

控制器

+關(guān)注

關(guān)注

112文章

16361瀏覽量

178071 -

PCIe

+關(guān)注

關(guān)注

15文章

1239瀏覽量

82658 -

dma

+關(guān)注

關(guān)注

3文章

561瀏覽量

100587

原文標(biāo)題:【學(xué)術(shù)論文】基于FPGA的PCIe總線接口的DMA控制器的設(shè)計(jì)

文章出處:【微信號(hào):ChinaAET,微信公眾號(hào):電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA的PCIE接口應(yīng)用需要注意哪些問題

【FPGA干貨分享三】基于FPGA的LBS控制器設(shè)計(jì)

基于FPGA的PCI Express總線接口應(yīng)用

采用FPGA實(shí)現(xiàn)PCIe接口設(shè)計(jì)

如何通過PCIe進(jìn)行FPGA到PC的通信?

如何利用PCIe DMA總線實(shí)現(xiàn)一個(gè)基于FPGA的PCIe 8位數(shù)據(jù)采集卡?

CPU數(shù)字通信接口和FPGA進(jìn)行數(shù)據(jù)通信設(shè)計(jì)實(shí)現(xiàn)

全愛科技Atlas200I A2 AI加速模塊-FPGA PCIE接口驗(yàn)證平臺(tái)

基于FPGA的PCI接口控制器的設(shè)計(jì)與實(shí)現(xiàn)

FPGA實(shí)現(xiàn)CAN總線控制器源碼

基于FPGA 的SPI Flash 控制器設(shè)計(jì)及驗(yàn)證

Crossbar的多通道DMA控制器設(shè)計(jì)

如何使用FPGA的PCIe總線進(jìn)行DMA平臺(tái)設(shè)計(jì)

dma控制器的組成

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

基于FPGA的PCIe總線接口的DMA控制器的實(shí)現(xiàn)并進(jìn)行仿真驗(yàn)證

基于FPGA的PCIe總線接口的DMA控制器的實(shí)現(xiàn)并進(jìn)行仿真驗(yàn)證

評(píng)論