以下文章來源于西風念,作者zwliu

前幾天測試中心在對伺服電機控制板進行測試中,發現多次隨機點擊控制屏上控制指令時,會出現正常運行的電機突然就停了。在當前指令還沒有執行完,并且確認沒有下發急停指令的情況下,正常轉著的電機突然就停了。

突然停機,,馬上要交付的機器突然暴露還有問題,慌得一批。明明之前都經過長時間測試了的,不管了,趕緊查原因。

1、首先查復位信號,對系統發起復位重啟指令,能恢復,所以我一開始還以為是不是系統誤發了復位指令,于是繼續測試,讓現象復現,此時去查看復位信號寄存器,顯示復位信號是正常的;

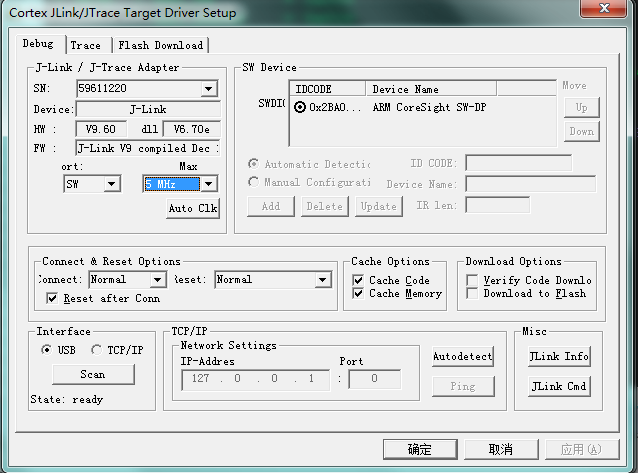

2、該板子由于沒有引出jtag無法使用在線邏輯分析儀VLA看信號,當時為了方便排查設計問題,將很多關鍵信號引入到了寄存器,通過寄存器一路排查,發現問題出在fifo上。Fifo數據寫不進,前方發來的控制指令無法被后方的執行端正確接收,也就是說控制指令傳達不下去,信號在這里中斷了。

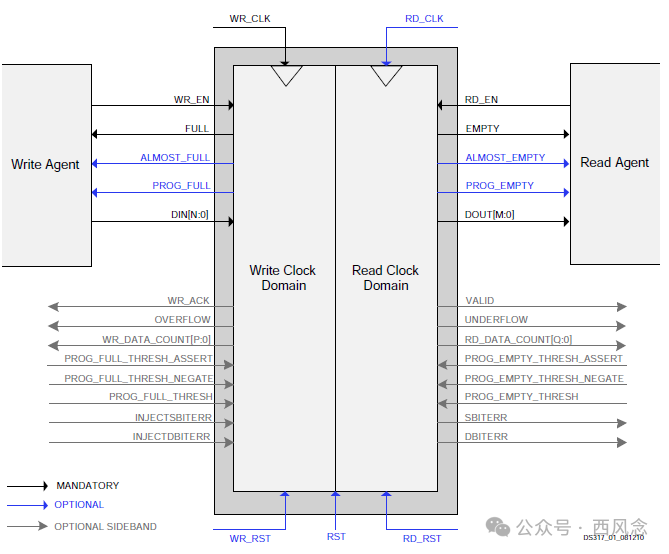

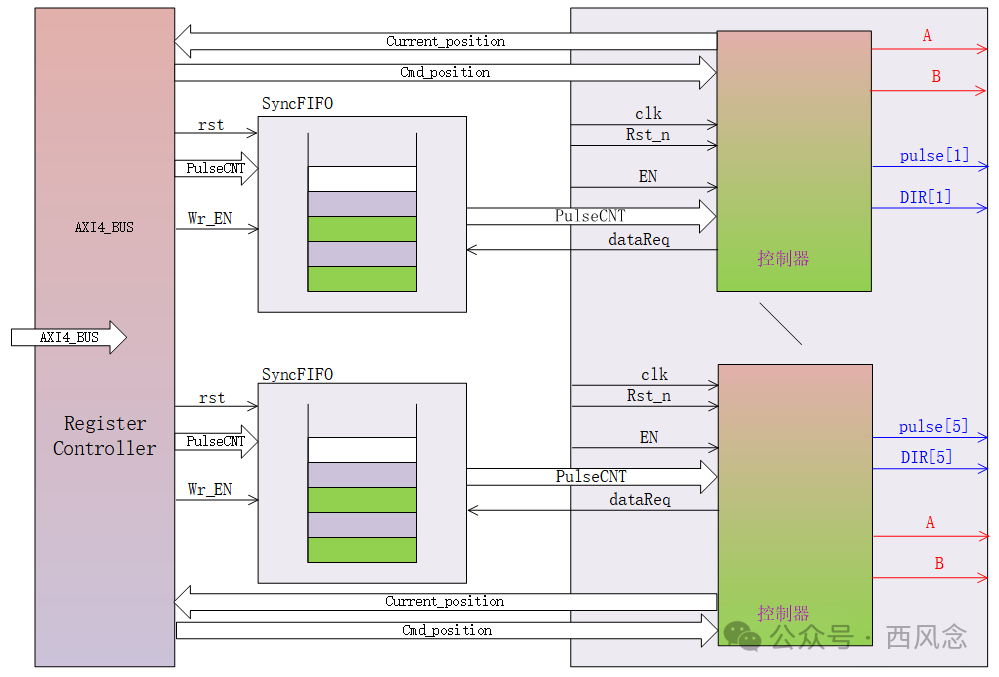

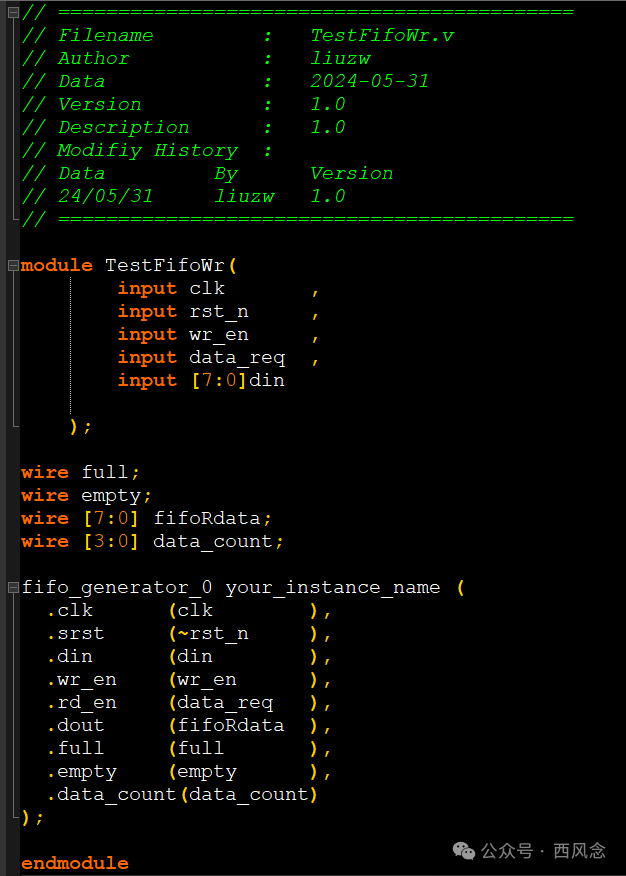

下圖:fifo接收上位機過來的指令,指令數據緩存在同步fifo,下級模塊在fifo讀取相應的指令做執行。

2、因為設計中對寫使能信號,寫數據,以及fifo數據量都做了監測,寫使能是單周期脈沖信號,通過計數器對寫次數,以及寫數據都進行了累加,這些統計信號都放到了寄存器,于是直接把寄存器狀態值調出來看,發現寫次數一直在累加,寫數據也在變化,但是數據量卻一直保持為0,也就是這個FIFO在寫時鐘正常,寫數據正常的情況下,數據卻死活寫不進,讀不出數據,數據量保持為0不增加。

這種情況一開始確實一點違背我的認知邏輯了,我認為在寫信號正常的情況下,并且fifo數據量為0也就是fifo為空的情況下,寫不進數據,這很難理解。

于是去網上搜索,看看有沒有人出現過類似的現象,一搜還真有好幾篇文章提到這個問題,都說在工程中遇到了FIFO寫不進的問題,并且解決問題的過程費了很大的功夫,花了很長時間才定位到問題所在,比較典型的是明德揚寫的這篇:

截圖如下:

限于篇幅,只截了一部分,如果有遇到了類似的問題可以搜索這篇文章看全篇,他們最后是查閱官方FIFO手冊,提示fifo的復位信號必須是和寫時鐘同步,也就是異步復位存在亞穩態,會導致低概率的錯誤使FIFO無法工作,就是說不能使用異步復位。

于是把異步復位同步化,問題得到解決。

問題是他們的測試過程都是反復開機,這種情況可能發生在上電的時候,一上電由于復位信號異常沒有正確復位,是有可能導致系統不能正常工作。

可是我這里的情景并不相同,不是上電之初,而是工作中突然死機,感覺和復位信號關系不太大,但是我又沒有好的辦法,還是按同樣的方法對復位信號同步處理。測試結果還是會死機,也就是說確實和這個復位信號無關。

這下有點一籌莫展了。。。

思考良久,我在想是不是vivado的IP核還有哪里有需要注意又沒有注意到的方,但是黑盒子我又沒辦法查細節原因。于是索性不用官方提供的fifo,自己動手寫了個同步fifo,自己寫的fifo當然所有的細節原理自己是很清楚的,即使出現問題,也是很容易查的。

結果是把自己寫的同步fifo掛上去,電機還是照死不誤,只是這樣一來,我就清楚了應該不是fifo的用法問題了,應該是設計邏輯哪里還有隱藏的問題;

fifo是做過基礎的仿真的,邏輯是沒有大問題的。開始把寫的fifo拿出來仿照實際工作環境進行更細致地仿真,我們的使用條件是,上位機每隔一段時間發一次數據,比如10毫秒,FPGA把時間起點錯開,然后在FIFO后端邏輯每隔10毫秒取一次數據,并且這個間隔時間是相對很穩定的。上位機和FPGA都做了嚴格的控制,確保5毫秒的精確度,上位機的5毫秒精度可能因為系統原因不能很準確,允許左右偏移1-8ms都可以,但是不能出現累計誤差。

Fifo的讀機制是自動根據數據量判斷非空,非空就立即啟動讀動作。

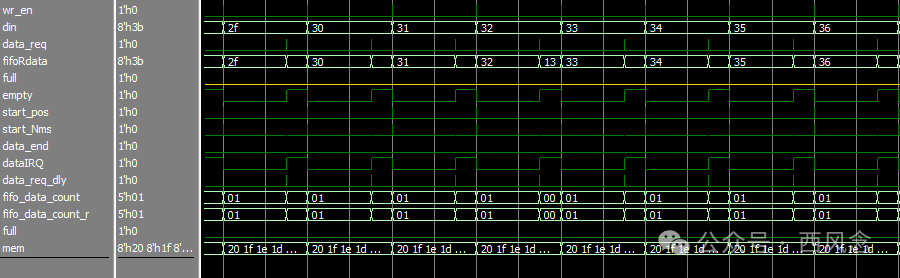

現在仿照實際環境進行測試,固定間隔寫,等間隔固定讀,可以看到同時開啟讀寫,數據量是保持0,1平衡的;

本來想錯開一點,提前寫入兩個數據,讓fifo數據量保持在2,3之間,結果手誤寫使能沒有拉低,一直在寫數據,直接把fifo干滿了。這下看到的情景令所有問題豁然開朗。

1、fifo滿了以后的數據個數不是最大值,而是溢出清零后變成最小值0;

2、之前以為fifo數據量等于0就以為fifo是空的,這里卻恰恰相反,fifo數據量為0的時候可能是fifo剛滿溢出了導致清零。

3、寫滿導致fifo一直寫不進數據,數據量保持為0;

4、數據量為0,導致系統認為fifo一直是空狀態,無法自動發起讀信號;

5、這次上位機控時測試機制有點問題,導致寫快于讀,原以為不會出現寫滿的情景,如果操作不當還是會出現寫滿,寫滿就會卡死停機。

于是很快確定原因,當前測試的上位機時間控制設置不夠嚴謹,導致雙方同步時間產生累計誤差,這個誤差累計長了就會把fifo填滿,而我們的設計本意是得有機制保證不會出現寫滿才行。這個后面把fifo深度加大,長時間測試后出現數據滯后的原因是一致的。

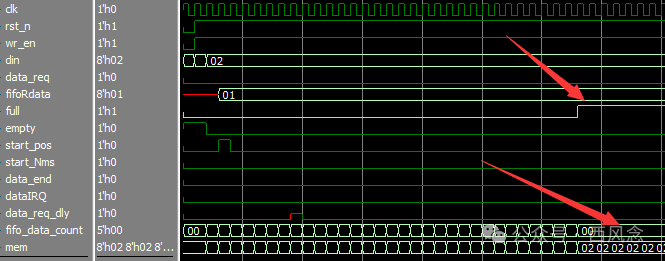

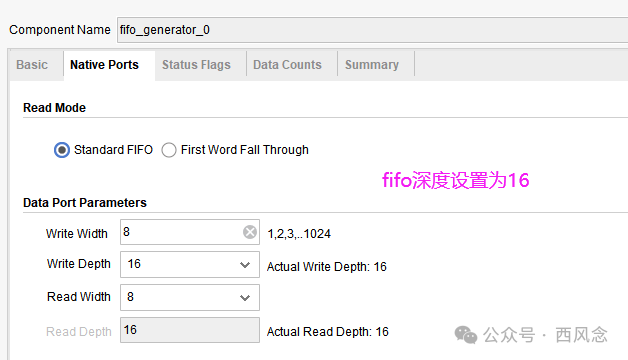

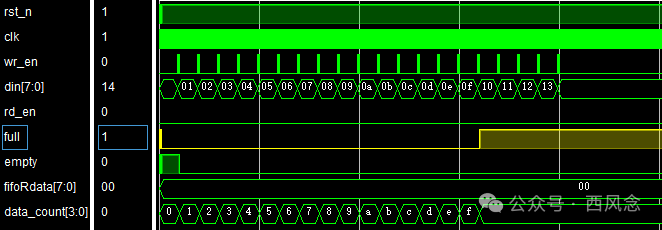

下面在vivado用官方的IP復現這一現象:

fifo深度設置為16,連續寫,發現數據寫入16個數后,full信號拉高,此時數據量并不是保持在f,而是會在此刻清零。最開始以為的數據量是0,做出fifo是空的判斷是錯誤的。

Fifo的用法是芯片/FPGA設計的基礎,早些年也寫過一系列的測試筆記只為全方位理解fifo的工作邏輯和用法,包括:

1、standard fifo模式和first fall-through模式的區別

2、fifo復位的機制,復位時間復位時長

3、讀寫信號自動關聯empty和full的關系

4、wr_rst_busy信號的使用邏輯

5、fifo用來打包傳輸控制信號和數據信號的方法

6、同步異步fifo數據量和Fifo模式以及讀寫信號之間的對齊關系

等等...

這些機制對于正確設計fifo邏輯,對于系統穩定性都很重要,今天也算是發現一個以過去的經驗可能會忽略導致出錯的地方,覺得還有點意思,于是整理分享出來。

很多時候我們的知識的獲取來源于網絡,來源于眾多網友的經驗總結,時常懷著一顆感恩的心,也想著回饋于網絡,于是也會分享一些小經驗,若能使人有益,也覺得挺有意思。

另外也是自己的一種學習手段,凡是問題,總是覺得凡是問題,能清晰地表達和總結出來就是真的理解了。

保持輸出就是持續學習的動力。

所以經常和身邊的家長或小朋友說學習也是這樣的,只有用輸出倒逼輸入,二者構成反饋閉環,學習才是有效的,才會學以致用正向促進。通過不斷地輸出和反思,我們可以不斷完善自己的知識結構。

-

fifo

+關注

關注

3文章

389瀏覽量

43769 -

指令

+關注

關注

1文章

608瀏覽量

35777 -

伺服電機

+關注

關注

85文章

2053瀏覽量

58017 -

復位信號

+關注

關注

0文章

54瀏覽量

6349

原文標題:FIFO寫數據失敗問題分析

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【鋯石A4 FPGA試用體驗】fifo實驗(2)-異步fifo

異步FIFO的設計分析及詳細代碼

你們知道FIFO最小深度計算嗎

DEBUG-在存在中斷的情況下SPI寫數據失敗

XILINX FIFO寫不進去的問題分析及解決方法

FIFO的使用介紹

異步FIFO之Verilog代碼實現案例

采用格雷碼異步FIFO跟標準FIFO有什么區別

FIFO寫數據失敗問題分析

FIFO寫數據失敗問題分析

評論